标签:

TXS(开漏优化设计),如I2C

TXB(上拉优化设计),如SPI

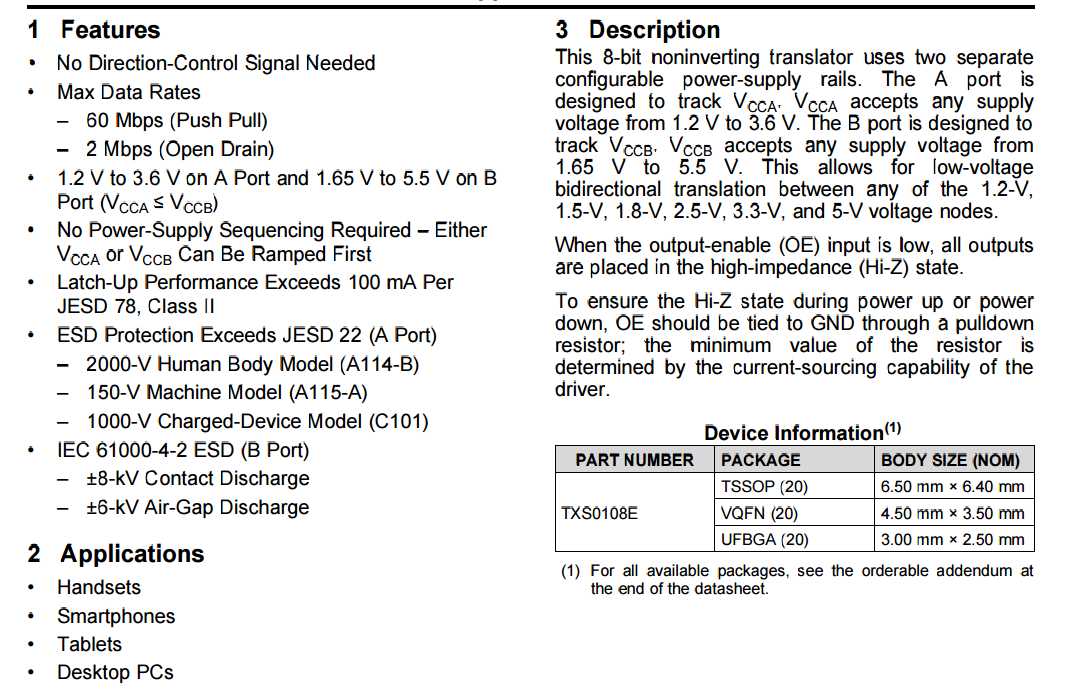

TXS0108 has integrated pull-up resistors to save board space and cost in open-drain applications.

The TXS0108 Does NOT need external pullup resistors.

The TXS0108 is intended for high drain devices and external pullups will cause problems.

Integrating the pullups into the chip is the main differerance between the TXS0108 and TXB0108.

For the sake of search ability, this is the same for the TXS0102, TXS0104, TXS0106.

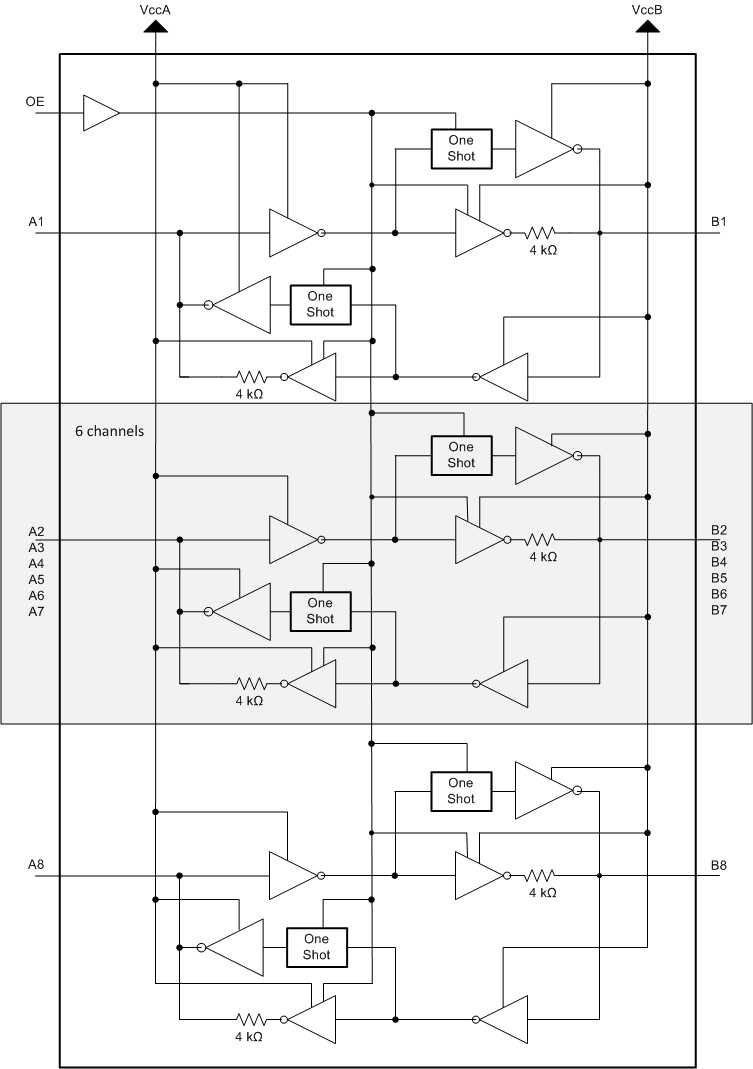

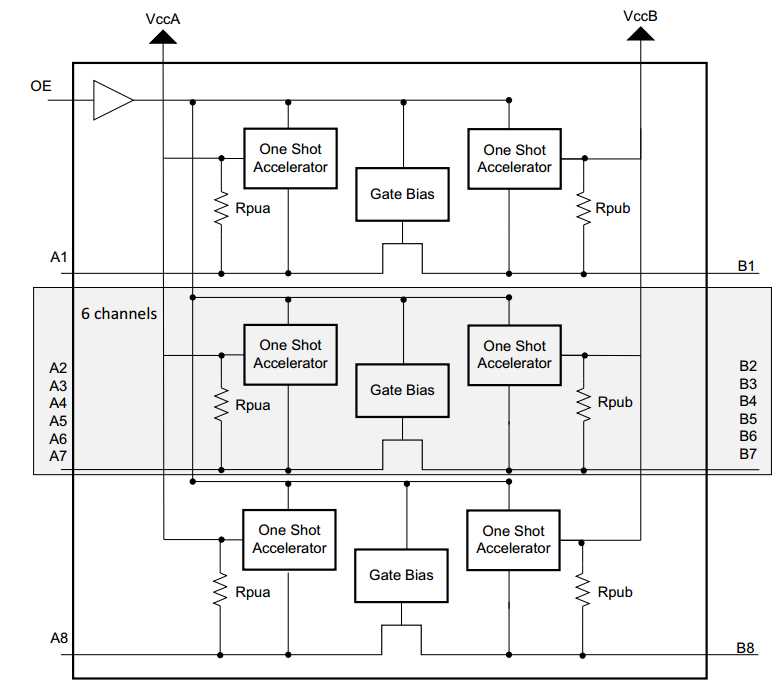

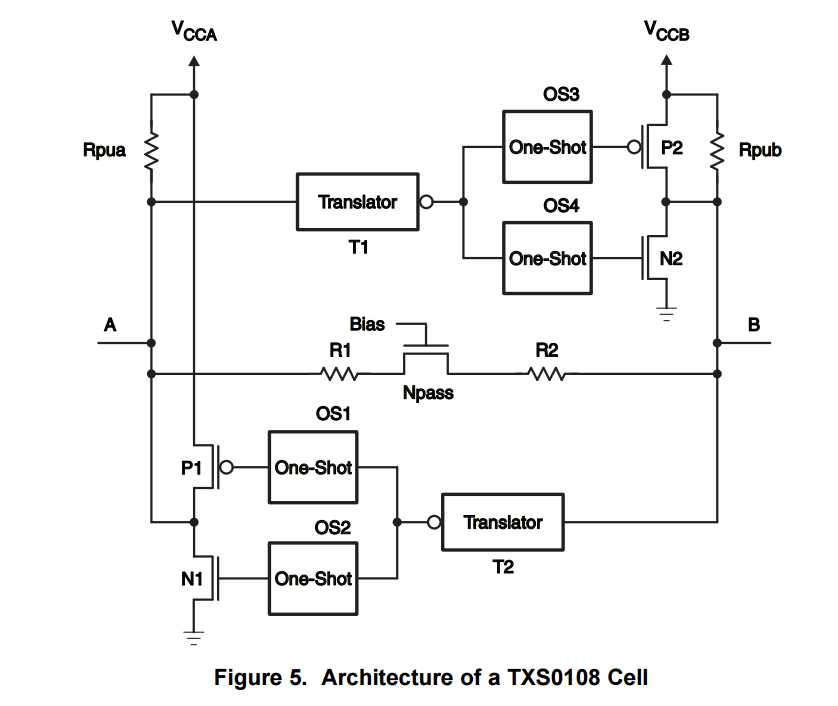

To address the application requirements for both push-pull and open-drain mode,

a semi-buffered architecture design is used and is illustrated below (see Figure 5).

Edge-rate accelerator circuitry (for both the high-to-low and low-to-high edges),

a High-Ron n-channel pass-gate transistor (on the order of 300 Ω to 500 Ω)

and pull-up resistors (to provide DC-bias and drive capabilities) are included to realize this solution.

A direction-control signal (to control the direction of data flow from A to B or from B to A) is not needed.

The resulting implementation supports both low-speed open-drain operation as well as high-speed push-pull operation.

When transmitting data from A- to B-ports,

during a rising edge the One-Shot (OS3) turns on the PMOS transistor (P2) for a short-duration

and this speeds up the low-to-high transition.

Similarly, during a falling edge, when transmitting data from A to B, the One-Shot (OS4) turns on NMOS transistor (N2) for a short-duration

and this speeds up the high-to-low transition.

The B-port edge-rate accelerator consists of one-shots OS3 and OS4,

Transistors P2 and N2 and serves to rapidly force the B port high or low when a corresponding transition is detected on the A port.

When transmitting data from B- to A-ports,

during a rising edge the One-Shot (OS1) turns on the PMOS transistor (P1) for a short-duration

and this speeds up the low-to-high transition.

Similarly, during a falling edge, when transmitting data from B to A, the One-Shot (OS2) turns on NMOS transistor (N1) for a short-duration

and this speeds up the high-to-low transition.

The A-port edge-rate accelerator consists of one-shots OS1 and OS2,

transistors P1 and N1 components and form the edge-rate accelerator and serves to rapidly force the A port high or low

when a corresponding transition is detected on the B port.

标签:

原文地址:http://www.cnblogs.com/shangdawei/p/4817661.html