标签:style blog http 2014 com html

继续之前的问题。。

查了一些资料,其中zhaoyongke的博客http://www.openhw.org/zhaoyongke/blog/13-04/293202_a1698.htmlAXI总线学习中 提到:

ARM将用户自定义IP编入某一地址进行访问,读写时就像在读写自己的片内RAM,编程也很方便,开发难度较低。代价就是资源占用过多,需要额外的读地址线、写地址线、读数据线、写数据线、写应答线这些信号线,而且传输速度受限(主要是因为采用AXI-GP物理接口,带宽很低)。

我这种应用 用AXI4 应该可以做。所以 详细学习一下AXI4工作模式。

AXI4总线分为主从两端,两者间可以连续通信。让PL是muster,负责数据搬运好啦。

参见zedboard zynq 架构整理 jefby的博客http://www.eefocus.com/jefby1990/blog/13-05/293838_5ea28.html

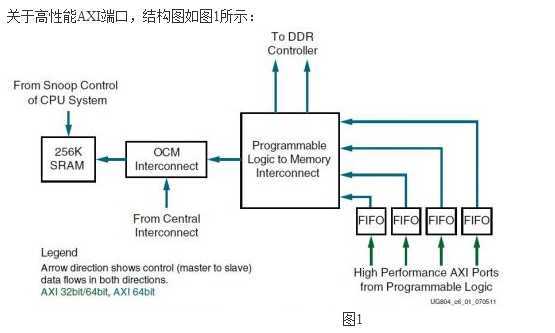

这个图1中显示,FPGA作为主设备,DDR Controller作为从设备有相应的AXI,看来之前的猜测对了,这个AXI就是AXI4吧

继续探索中。。

怎么把PS和PL部分结合起来,这个首先得知道怎么自定义通用IP核,或者用现有的IP核。并将之导入到PS中,然后编写驱动和应用程序来入门。这个DDR controller

应该就是现有的IP核。但是看见好多人写的基于AXI 总线的从设备IP设计,但是就是没有生成DDRcontroller的例子。。。

看看熟悉一下流程也好:

1.首先使用XPS创建ARM PS系统;2.创建AXI IP 3.将自定义IP核添加到PS系统 4.使用SDK编写IP核驱动程序和应用程序 5.下载及代码调试

就是说DDR controller属于AXI IP,那么就是一个由AXI连接到FPGA的一个从设备,也就是说DDR Controller 另一端是FPGA 那么我应该去找硬件说明中DDR 怎么通过AXI连到FPGA的。再次翻看ZedBoard_RevC.1_Schematic_130129.pdf 依然只有DDR与PS端的连线。看来应该找zedboard中关于AXI的文档,不知道什么文档。。。

先看一下cuter的博客 创建基于AXI Lite总线vga测试IP核系列。http://blog.chinaaet.com/detail/30923 做一下看看什么流程:(这一系列的看完就知道开发工具的使用流程并且知道怎么新建自己的IP核)虽然不是解决我的问题,还是看一下。

下面继续回到我的问题:PS直接读写DDR,PL作为主设备通过AXI4与从设备DDR Controller 相连,再访问DDR。现在的问题就分成2个小问题。一个是PS访问DDR怎么做。另一个是怎么讲PL与DDR Controller连起来并实现读写DDR。之前我们根据向导生成IP的过程中出了问题...

刚刚又问了个牛人,他提到了xilinx的application note。让我想起来,最开始问达人的时候也提到了这个app note 说是一些常用的上面都有,但是我还是不知道这个application note里面都有些啥。 找了一下xilinx官网发现一下信息可能会有用 http://www.xilinx.com/support/answers/45195.html 太晚了 明天继续看。。

标签:style blog http 2014 com html

原文地址:http://www.cnblogs.com/ly323/p/3704469.html