标签:

回到quartus,我们新建一个Verilog文件,将之前复制的代码粘贴进去,保存文件为led.v。为了后面的编译,需要将nioscpu的Quartus IP File(.qip)加入项目中,点击Assignments->Settings,在File中将nioscpu.qip加入,如下图所示,点击Add,再点击OK。

接下来,我们建立锁相环PLL,给Nios提供时钟。

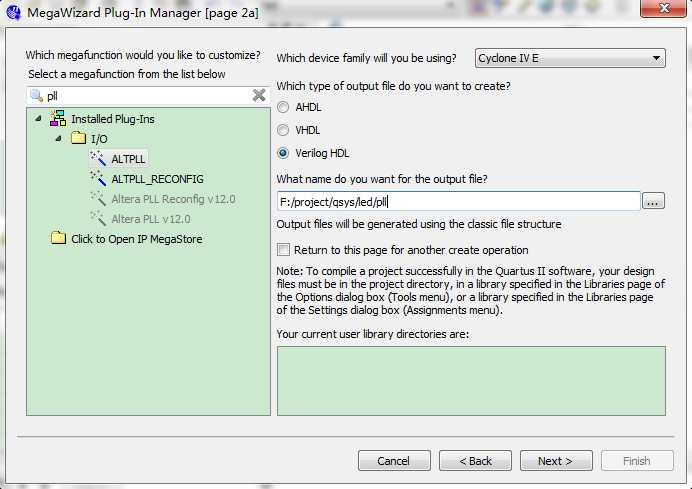

单击Tools->MegaWizard Plug-In Manager,点击Next,如图所示,搜索PLL,选择ALTPLL,在右边的输出文件地址中补上pll,点击Next:

接着page 1设置如下:

器件速度等级选8,输入时钟设为50M(因为开发板晶振为50M),点击Next,在page 2上把2个钩去掉,如图所示:

接着一直点击Next,直到设置clk c0,如下图所示设置,将c0输出频率设为100M,这是提供给Nios软核的时钟,与我们之前在Nios中设置的100M时钟频率相对应。

接下来我们还需要设置SDRAM的时钟频率,点击Next,如下图所示,

首先将Use this clock勾选,然后将Enter output clock parameters设置为2,这样实际频率就是100MHz。由于电路板及芯片的信号延迟等原因,我们需要对时钟相移进行调节,以达到 SDRAM 的时钟与软核之间的协调。我们将 Clock phase shift 设置为-73(具体原因请参考Nios那些事儿)。

设置好以后,点击Finish,出现Quartus Ⅱ IP Files的对话框,点击Yes,PLL构建就完成了。接着在led.v文件中对pll进行实例化,并补全整个工程,结果如下图所示,可能有人要问:为什么要用CLOCK,LED和RESET等名字呢?这先卖个关子,后面再解释。

接下来,我们对管脚进行分配。将随开发板一起的资料打开,找到AX301.tcl文件,将它复制到工程目录下。在quartus中点击Tools->Tcl scripts,如下图所示:

点击AX301.tcl,在Preview中我们看到,E15脚被设置为RESET,E1脚被设置为CLOCK,在LED对应的引脚中也有4个脚。大家可以去查看电路图看看对应的对不对。举个例子,如下图所示,E1脚对应CLOCK,而CLOCK正是对应于50M的晶振输入的,可见tcl文件中的设置是正确的。我们在Tcl scripts中点击Run,再点击OK,再点击Close。这时我们点击Assignments –> Pin planner,就可以看到管脚分配已经OK。

最后对工程进行设置,点击Assignments->Device,在出现的页面中点击Device and Pin Options,在Configuration选项卡中钩选Use configuration device,选择EPCS16,如下图所示:

接着在Unused Pins中选择As input tri-stated,这个主要是防止蜂鸣器响,如下图所示,

然后在Dual-Purpose Pins中把所有Value都设置为Use as regular I/O,如下图所示,

然后点击OK。最后开始编译,编译完成后退出。

标签:

原文地址:http://www.cnblogs.com/fimwest/p/5180633.html