标签:

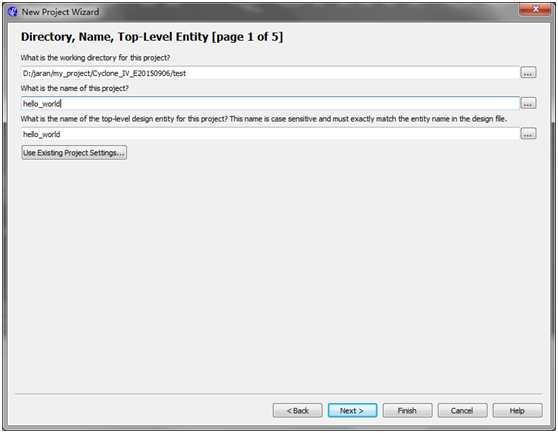

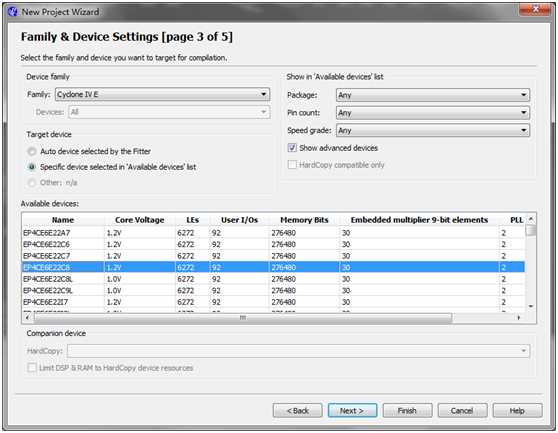

2、添加已经存在的文件,这里没有需要添加的文件,直接单击?Next>?进入下一步。进行器件设置。使用的?是Cyclone IV家族的?EP4CE6E22C8芯片,选择好后直接进入下一步。进行EDA工具设置,由于工程中不进行仿真等,故不进行设置,如果需要进行ModelSim仿真,则在Simulation行中,选择Tool Name?为ModelSim-Altera(这里根据所安装的ModelSim版本进行选择),Format(s)选择为Verilog HDL(这里也是根据所掌握的硬件描述语言进行选择)。点击?Next>?,进入了Summary(摘要)页面,然后单击?Finish?完成即可。

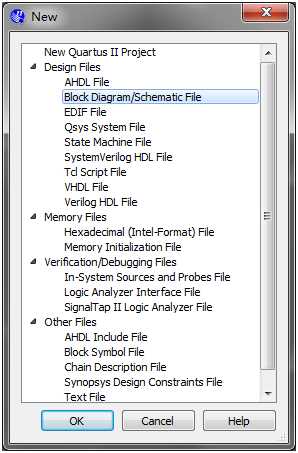

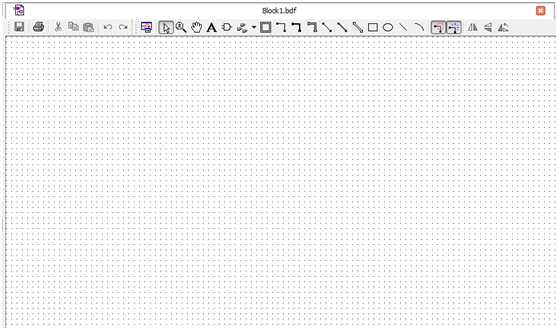

3、新建?Block Diagram/Schematic File?(方块图/原理图文件)。单击?File -> New..,选择Design Files中的Block Diagram/Schematic File,单击OK即可。

?

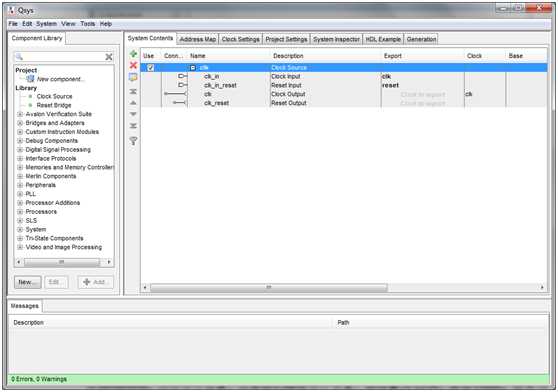

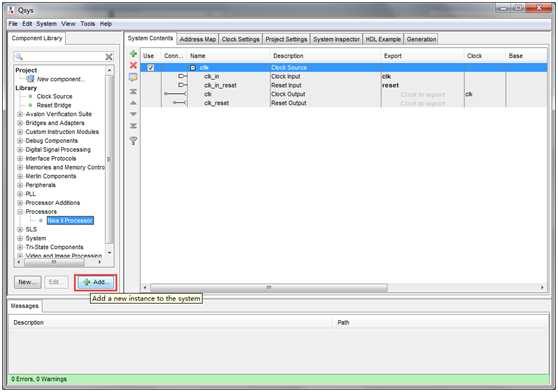

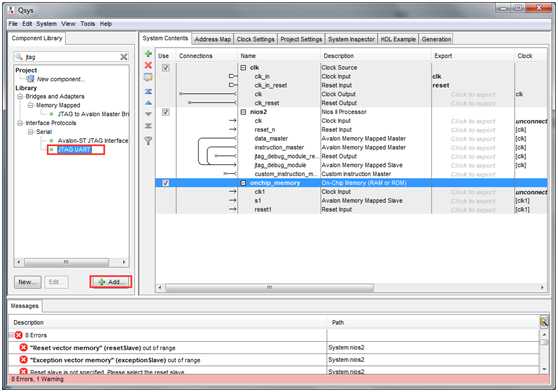

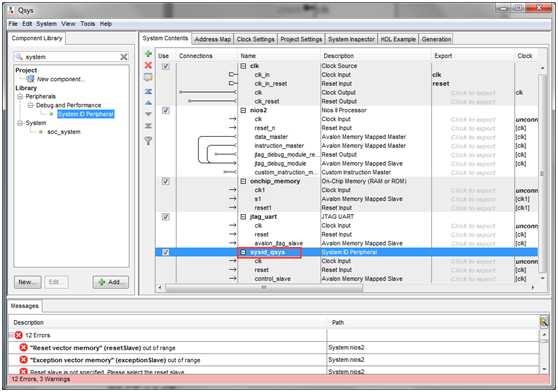

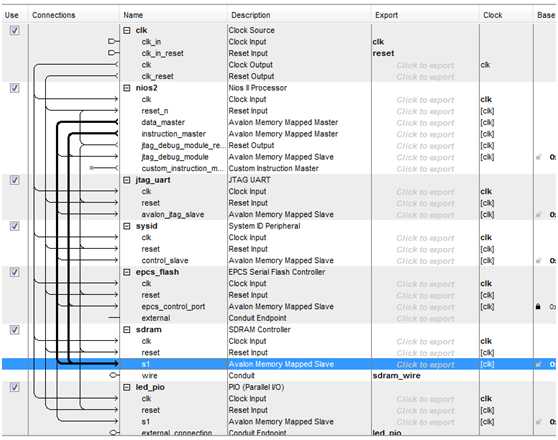

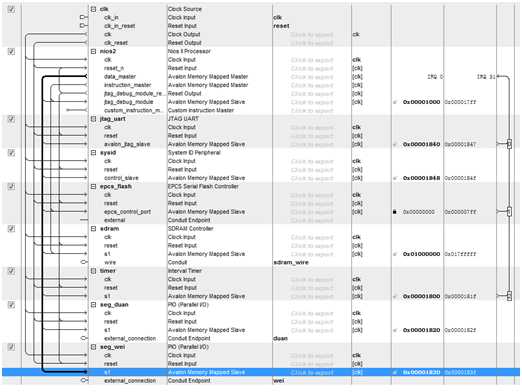

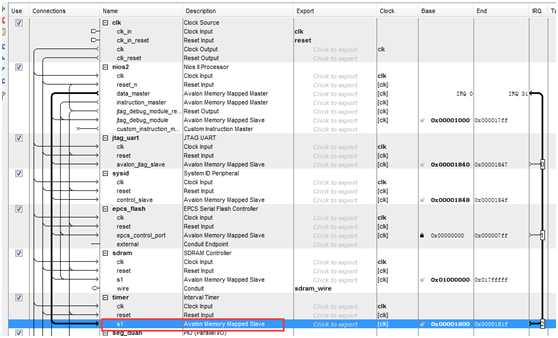

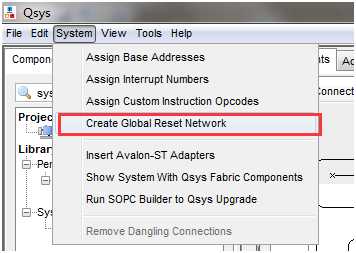

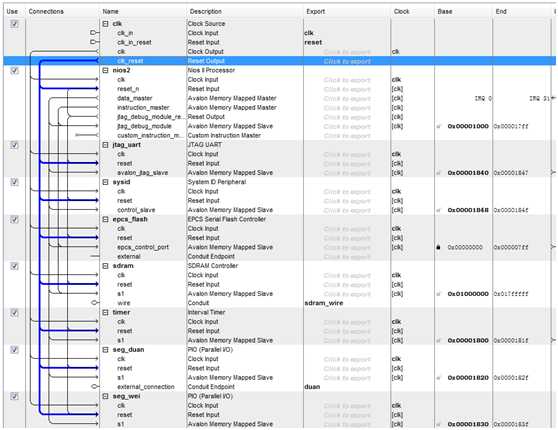

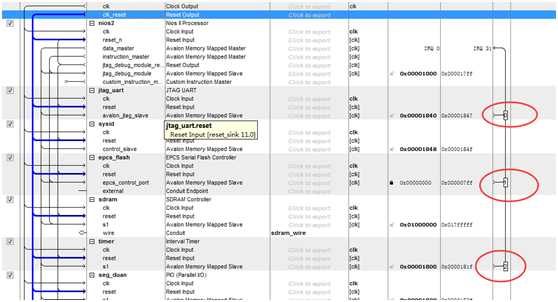

?,进入Qsys设置界面。系统已经默认添加了时钟模块,名称为?clk_0?,这里选中?clk_0,右击,选择Rename,将其名称更改为clk。以下再添加任何模块,都进行类似的名称更改,更改名称的方法类似,就不在重复叙述了。

?,进入Qsys设置界面。系统已经默认添加了时钟模块,名称为?clk_0?,这里选中?clk_0,右击,选择Rename,将其名称更改为clk。以下再添加任何模块,都进行类似的名称更改,更改名称的方法类似,就不在重复叙述了。

Nios II Processor、

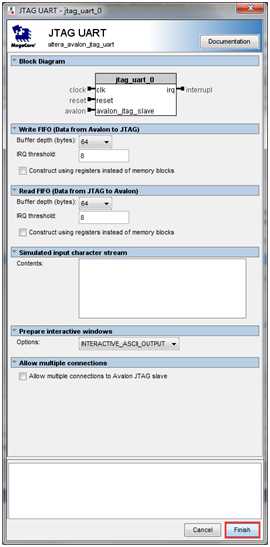

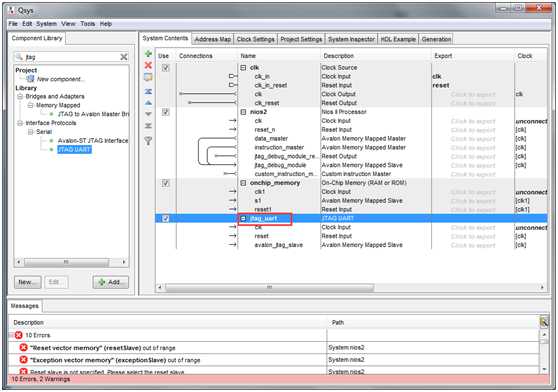

JTAG UART、

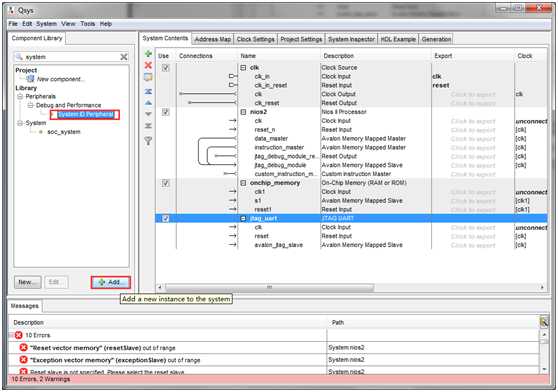

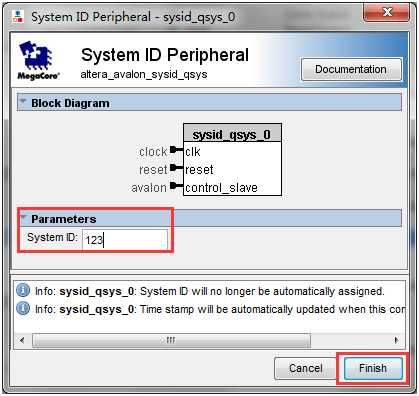

System ID Peripheral

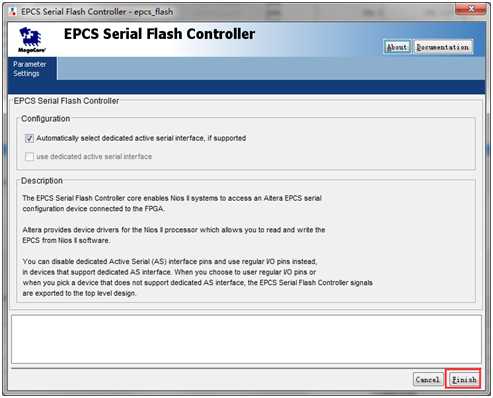

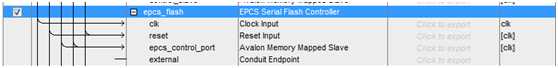

EPCS Serial Flash Controller

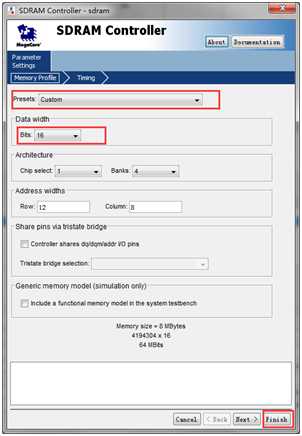

Sdram controller

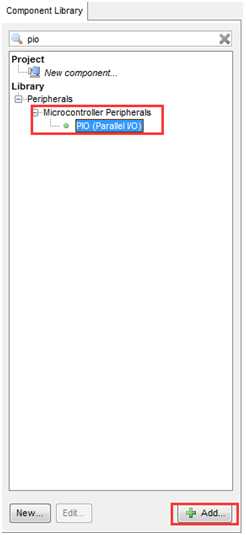

Pio

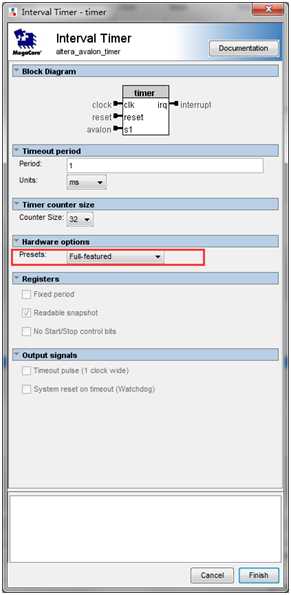

timer

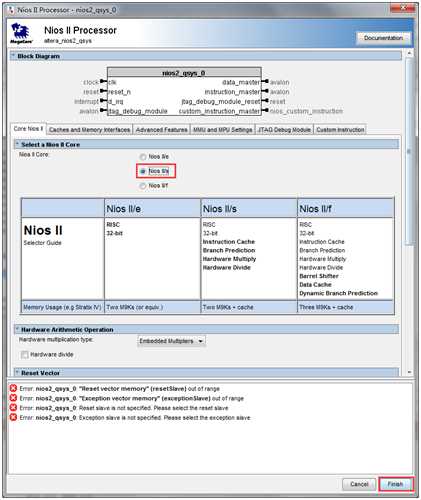

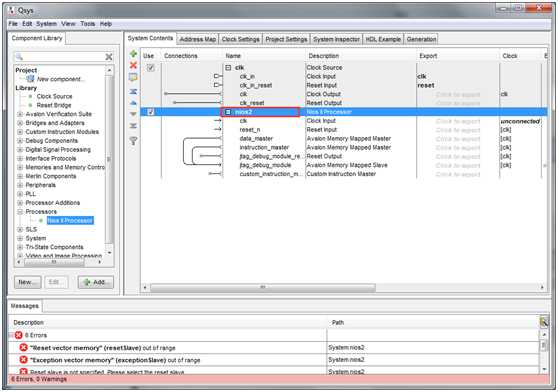

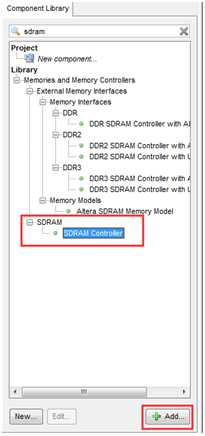

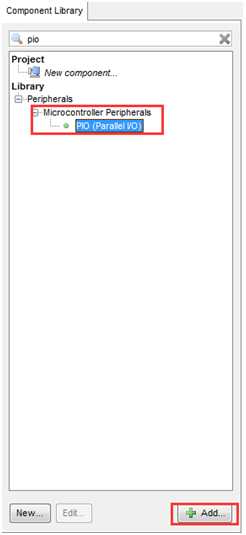

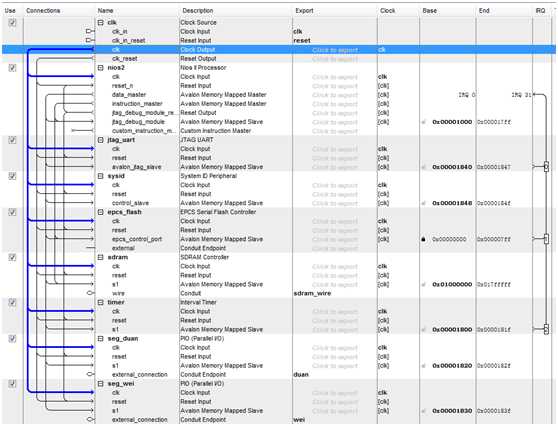

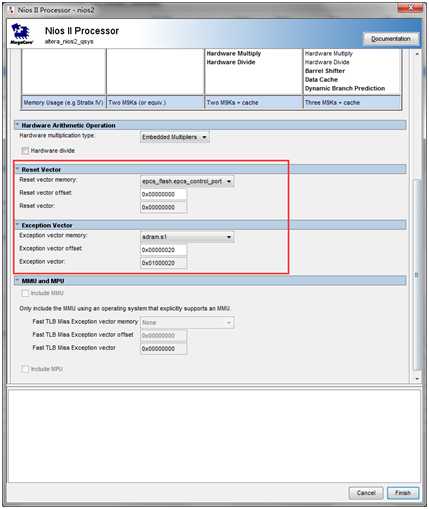

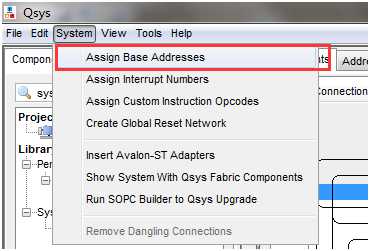

这7个模块。首先熟悉一下?Qsys?的界面。左面Component Library,是系统提供的元件库,里面有一些构成处理器的常用模块。右面是已经添加到系统的模块,也就是说,Nios II?软核处理器是可以定制的,根据具体需要来。在Component Library中搜索Nios II Processor,双击即可进行配置。首先需要选择的是Nios II?核心的类型。Nios II?软核的核心共分成三种,为e型、s型以及f型。e型核占用的资源最少,功能也最简单,速度最慢。s型核占用资源其次,功能和速度较前者都有所提升,f型核的功能最多,速度最快,相应的占用资源也最多,选择的时候根据需求和芯片资源来决定,这里选择s核。然后单击?Finish,结束当前配置。

?

?

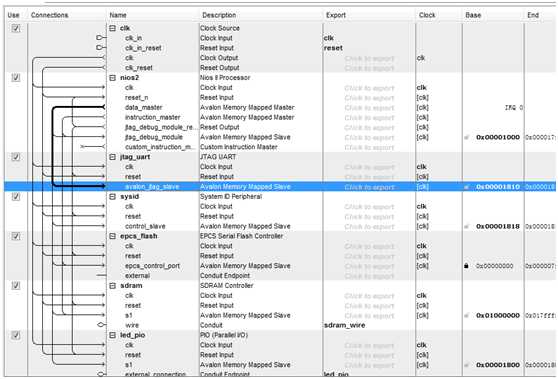

重命名为sdram;

重命名如下:

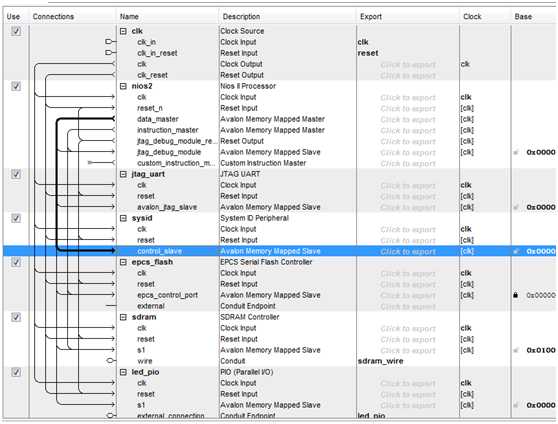

然后片内存储器sdram的s1和处理器nios2的data_master和instruction_master相连。

JTAG调试模块jtag_uart的avalon_jtag_slave和处理器nios2的data_master相连。

系统ID模块sysid_qsys的control_slave和处理器nios2的data_master相连。

?

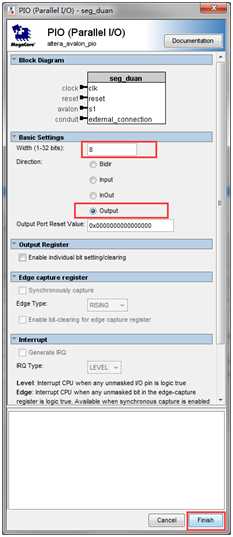

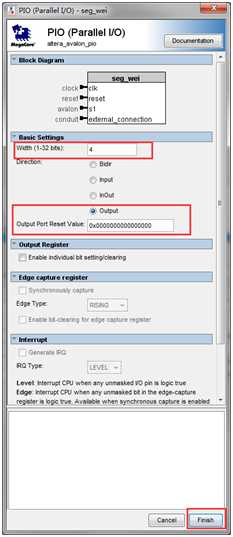

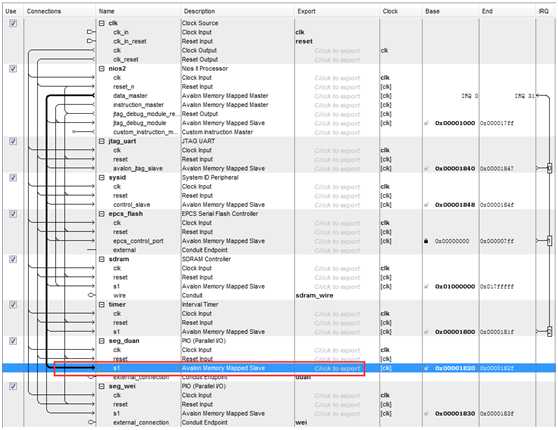

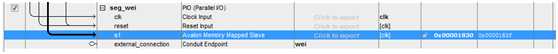

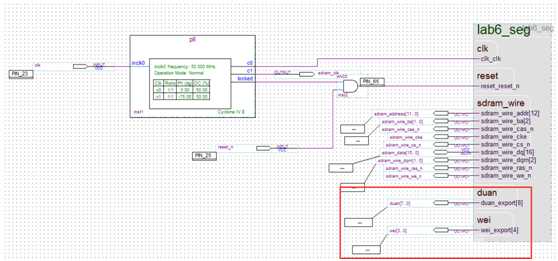

设置Seg_duan的输出端口,并重命名端口名;

设置Seg_wei的输出端口,并重命名端口名;

参照实验二(led),重新调用脚本对引脚进行配置

标签:

原文地址:http://www.cnblogs.com/logic3/p/5228923.html