标签:

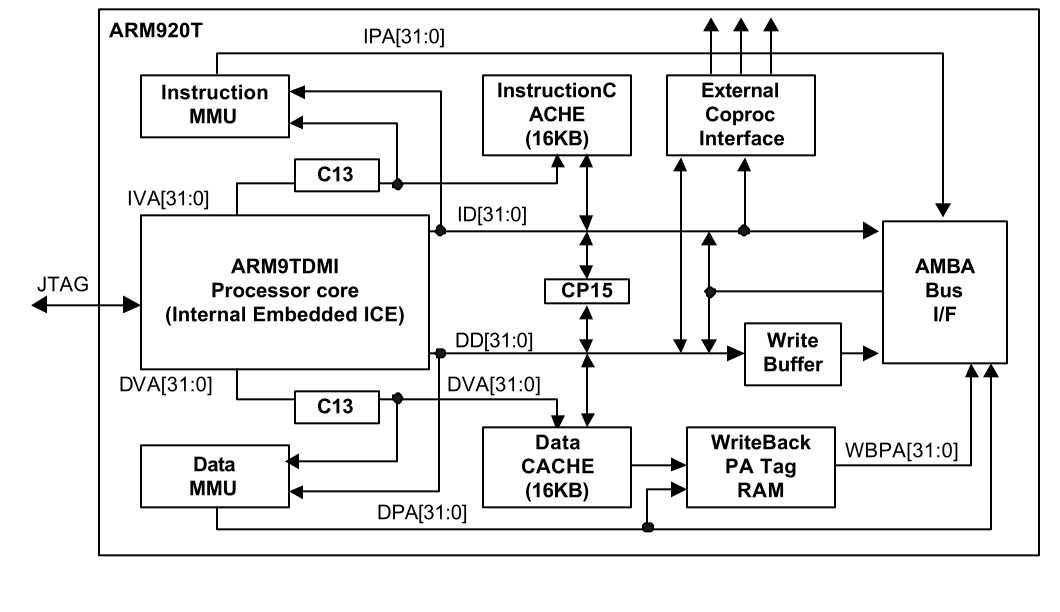

S3C2440处理器的结构如下图所示,其核心单元为ARM9TDMI处理器核,主要包括16K的指令Cache和16K的数据Cache,以及分开的指令和数据MMU单元等。CP15为一个协处理器(Co-Processor)。通过AMBA2.0(Advanced Microcontroller Bus Architecture)总线接口与外部设备相连。

图 1 S3C2440处理器框图

IVA指Instruction Virtual Address,指令虚拟地址;DVA指Data Virtual Address,数据虚拟地址。IPA指Instruction Physical Address,指令物理地址;DPA指Data Physical Address,指数据物理地址。

S3C2440处理器的封装大小为14mmx14mm,289-FBGA封装类型。工作频率最高为400MHz。

2.0版AMBA总线标准定义了三组总线,如下表所示:

表 1 AMBA总线标准中的三组总线

|

总线名称 |

全称 |

说明 |

|

AHB |

the Advanced High-performance Bus 高性能总线 |

应用于高性能、高时钟频率的系统模块,它构成了高性能的系统骨干总线。 |

|

ASB |

the Advanced System Bus 系统总线 |

是第一代AMBA系统总线,同AHB相比,它数据宽度要小一些,它支持的典型数据宽度为8位、16位、32位。 |

|

APB |

the Advanced Peripheral Bus 外设总线 |

是本地二级总线(local secondary bus),通过桥和AHB/ASB相连。它主要是为了满足不需要高性能流水线接口或不需要高带宽接口的设备的互连。 |

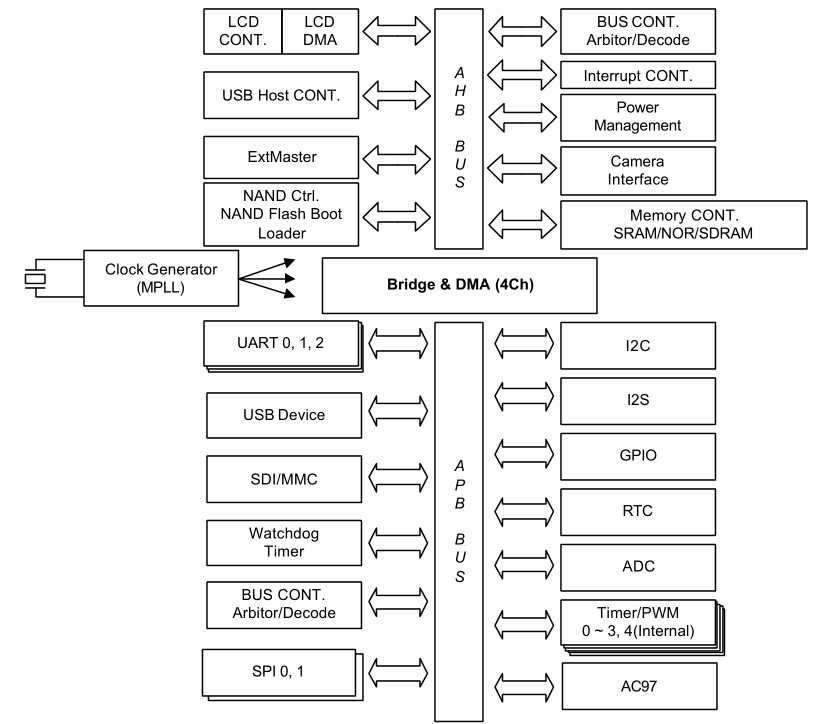

S3C2440处理器的外设与AMBA总线的连接如下图所示。

图 2 S3C2440外部设备连接图

MPLL锁相环产生时钟,供给AMBA总线上的各个设备使用。AHB总线上,主要包括LCD控制器、LCD的DMA模块,USB Host控制器,ExtMaster(允许外部设备作为总线的Master),NAND 控制器、NAND Flash启动的装载器,总线控制器、仲裁器和译码器,中断控制器,电源管理模块,摄像头接口模块,内存控制器(包括SRAM、NOR Flash和SDRAM三种)。

APB总线上挂载各种外设,包括3个UART,USB设备,SDI/MMC卡,看门狗定制器,总线控制器、仲裁器和译码器,2个SPI总线,I2C总线,I2S总线,GPIO接口,RTC实时时钟,ADC模数转换器,定时器/PWM发生器,AC97音频编解码器。

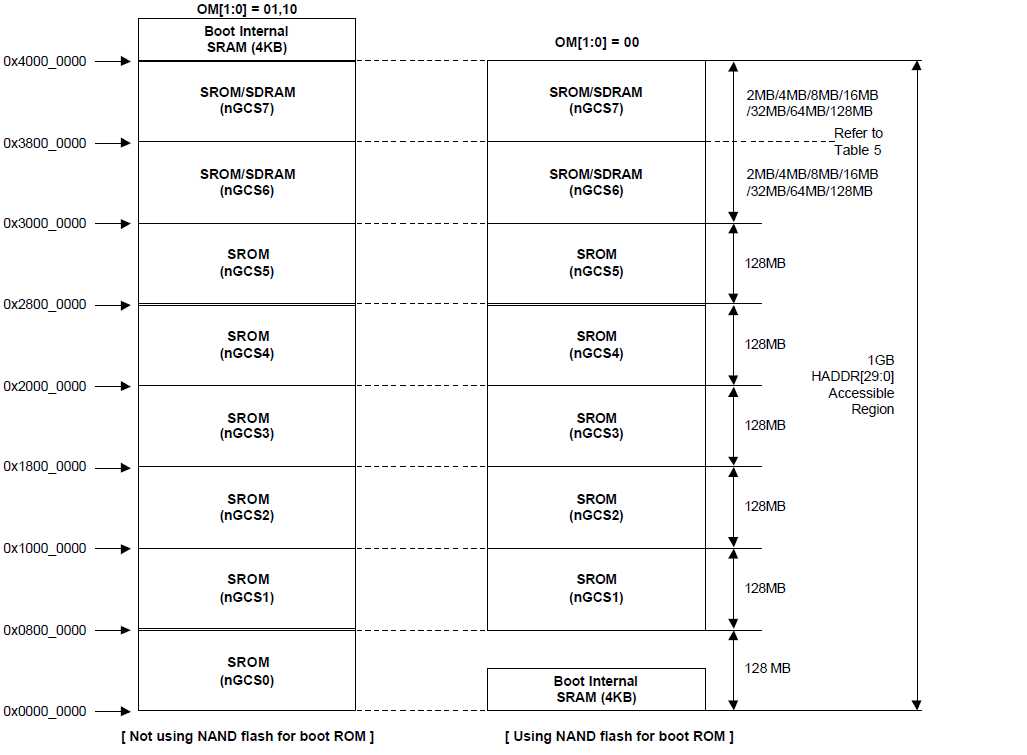

S3C2440的地址空间如下所示:

图 3 S3C2440复位后的内存映射

从图中可以看到,S3C2440的内存控制器将可访问的内存划分为8个Bank,每个Bank通过nGCS[0~7]引脚选通,占用空间为128MB,总计可访问1GB的内存空间。前6个Bank可访问SROM(包括ROM和SRAM),后两个Bank可访问ROM、SRAM和SDRAM。

根据OM[1:0]引脚的不同,可选择是否使用Nand Flash作为启动ROM,这时内存在地址空间的映射不同。具体地说,是Bank0和内部4K的启动SRAM(Boot Internal SRAM)的映射不同。Boot Internal SRAM是处理器内部的一块专用的SRAM存储区,大小为4K,专门用于系统的启动。

当OM[1:0]的值为01或者10时,Bank0可访问SROM,内部的4KB启动SRAM位于0x4000_0000处;当OM[1:0]的值为00时,选择Nand Flash为启动RAM,此时Bank0不能访问SROM,内部的4KB启动SRAM位于Bank0的地址0x0000_0000处。

选择Nand Flash为启动ROM时,Nand Flash Boot Loader模块会自动将Nand Flash的前4K数据读取到启动RAM,然后复位从启动RAM处的指令开始执行。

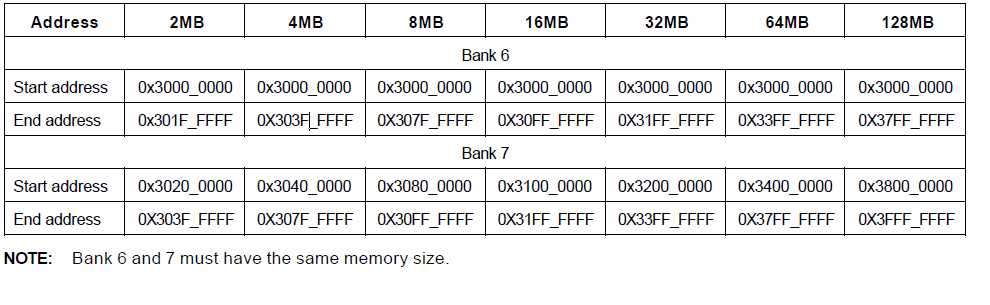

图 4 S3C2440的Bank6和Bank7地址

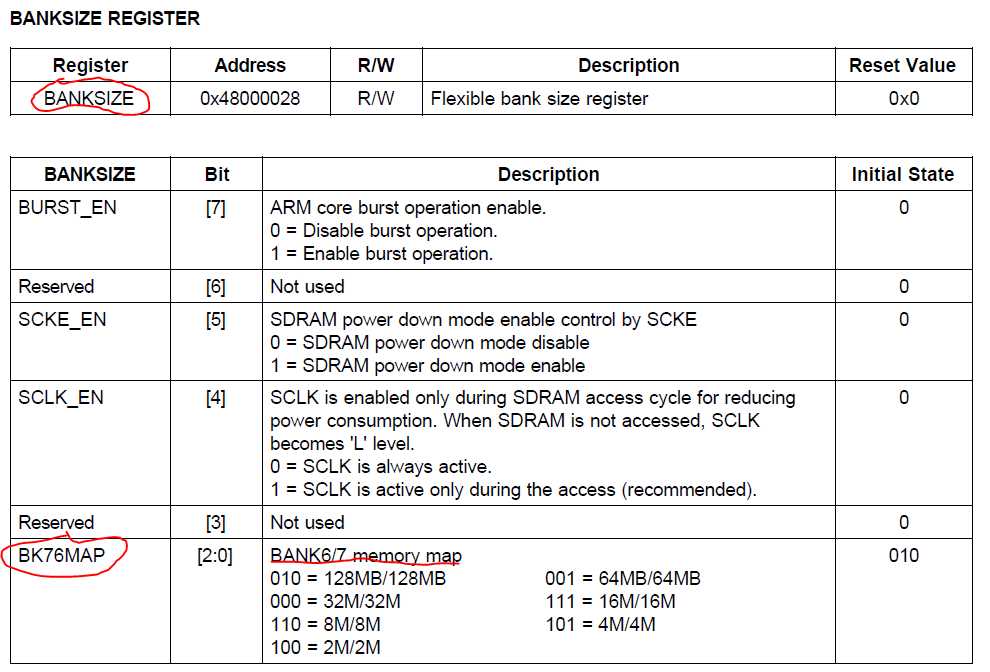

Bank6和Bank7用于连接SDRAM,其起始地址和结束地址是可配置的,如上图所示。Bank6地址一定是从0x3000_0000开始,根据SDRAM内存大小的不同,Bank6的地址结束,然后Bank7直接从Bank6结束的地方开始,使Bank6和Bank7形成物理上连续的地址空间。具体的配置需要设置BANKSIZE专用寄存器。如下图所示。

BANKSIZE寄存器的地址为0x4800_0028,其bit[2:0]可是只Bank6/7的映射方式,表示Bank的内存空间大小。

S3C2440使用外部SDRAM的频率为133MHz左右。

BANKSIZE寄存器的地址为0x4800_0028,其bit[2:0]可是只Bank6/7的映射方式,表示Bank的内存空间大小。

S3C2440使用外部SDRAM的频率为133MHz左右。

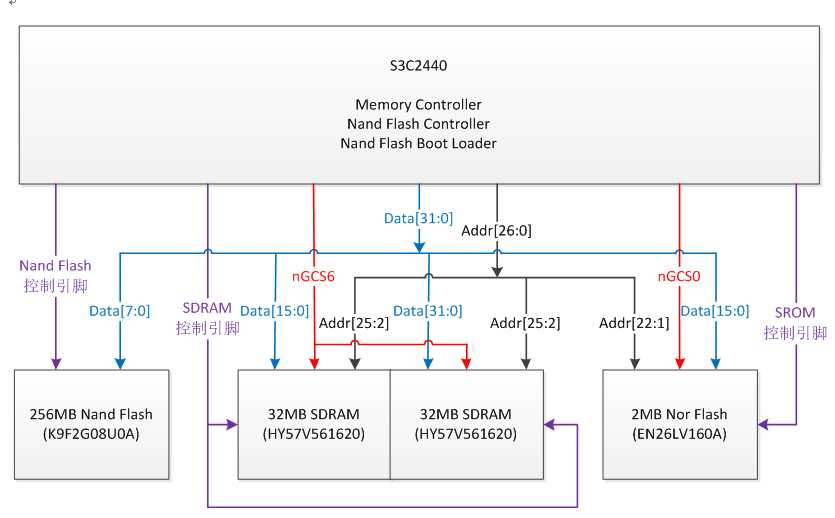

前面讲述了S3C2440芯片的内存地址空间的划分,这里我们通过TQ2440开发板上的设计给出一个实际的例子。TQ2440是广州天嵌计算机技术有限公司提供的一款基于S3C2440处理器的开发板,其Memory连接结构如下图所示:

图 6 TQ2440开发板的Memory连接

从图中可以看出,TQ2440仅使用了S3C2440处理器中8个Memory Bank中的2个,即Bank0和Bank6。Bank0连接2MB的Nor Flash,数据宽度为16bit;Bank6连接2个数据宽度为16bit的SDRAM颗粒,每个颗粒内存容量32MB,组成总容量为64MB数据宽度为32bit的DDR主存。通过Nand Flash控制器,连接8bit数据宽度的Nand Flash,容量为256MB。

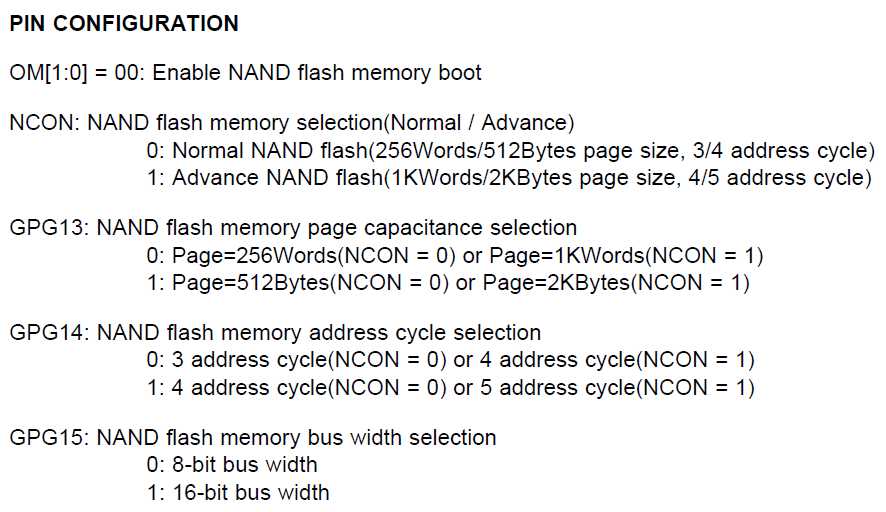

Nand Flash控制器的相关配置主要通过引脚完成,相关引脚包括:

在TQ2440上,OM[0]可通过拨码开关选择,OM[1]接地。OM[1:0]只能选择为00或01,为00时表示Nand Flash启动,为01时表示nGCS0的Bank为16bit模式。nGCS0连接在Nor Flash上,即从16bit数据总线宽度的Nor Flash启动。

TQ2440上对Nand Flash控制器的配置引脚连接如下,在开发板上使用的Nand Flash型号为K9F2G08U0A,故NR5电阻不焊接。

图 7 TQ2440开发板的Nand Flash控制器配置

从图中可以看出,NCON引脚的值为1,GPG13引脚的值为1,GPG14的引脚值为1,GPG15的引脚值为0。这些值分别与K9F2G08U0A芯片的特征对应——内存容量为256MB(2Gbit),Page Size为2KB,需要5个Address Cyle,数据宽度为8bit。

S3C2440的Linux启动过程分析(一)——SC2440处理器结构

标签:

原文地址:http://www.cnblogs.com/greatwind/p/5452133.html