标签:

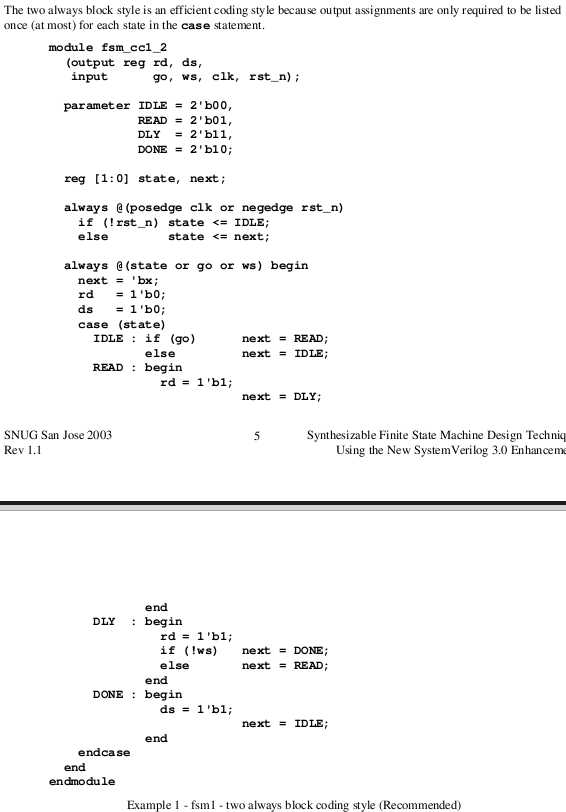

1.Two always block style with combinational outputs(Good Style)

对应的代码如下:

2段式总结:

(1)the combinational always block sensitivity list is sensitve to changes on the state variable and all of the inputs referenced in the combinaltional always block.

这个实际中一般就用always@(*)就OK了。

(2)the combinaltional always block has a default next state assignments at the top of the always block

(3)default output assignments are made prior to the case statement(this eliminates latches and reduces the amount of code required to code the rest of the outputs in the case statement and hightlights

in the case statement exactly in which states the individual output(s) change).

开始所有的output and next state变量都要初始化默认值,否则会有latches产生(特别是当outputs比较多时,容易漏掉个别output singals)。

(4)in the states where the output assignment is not the default value assigned at the top of always block,the output assignment is only made once for each state.

每一个state,如果output输出不是默认值,仅仅被赋值一次。

(5)状态跳转的弧线(arc)个数与if-else-type语句个数相同。

(6)每一行只有一个next_state语句,方便阅读调试。

default X-assignments common trick:

标签:

原文地址:http://www.cnblogs.com/chip/p/5468100.html