标签:

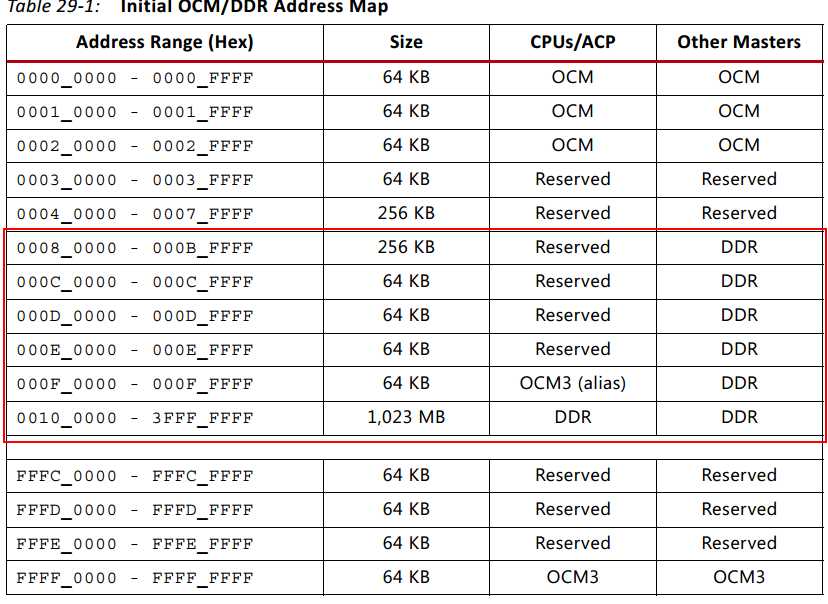

上一节说到了DDR寻址的问题,如下图:

从官方文档上我们看到了DDR的地址是从0008_0000开始的,那么我们开始修改Xilinx给我们提供的IP核代码。其实很简单,上一节已经分析了地址停留在0000_1000的原因,现在我们只需要把write_burst_counter的位宽变大就可以了。

从上表看到地址范围由全0到全1,计算一下就知道需要的宽度为27,即 C_NO_BURSTS_REQ = 26;

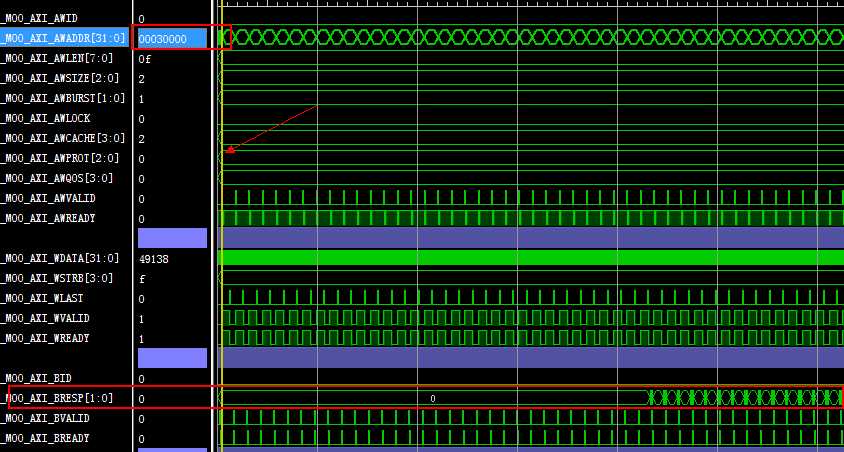

重新打包IP核,生成比特流。开始调试

由于从0003_0000开始的地址是保留位,理论上来说当我们写到这里了应该会报错,但实际上并没有,有上面两张图看出报错是从0003_07c0开始的,具体是什么原因还得以后继续深挖

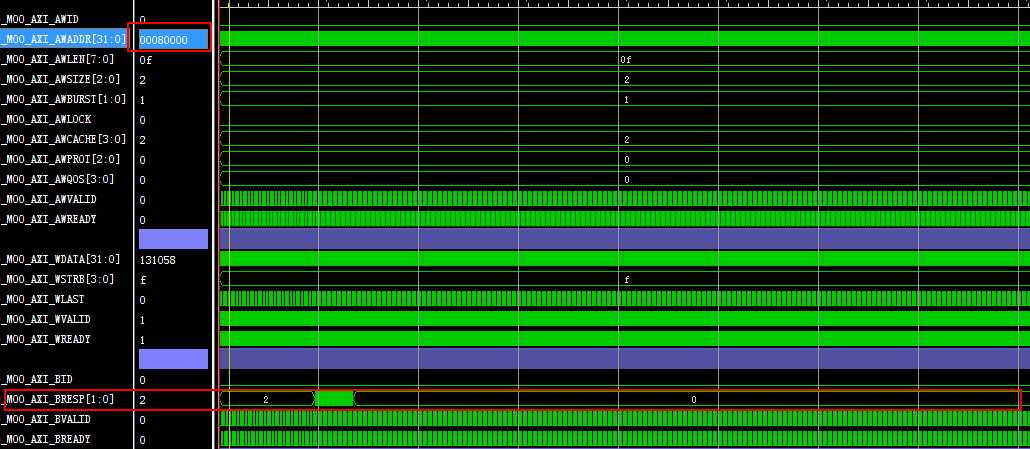

同样的,理论上从0008_0000开始的地址应该返回正常,但实际上是从0008_07c0开始正常的。

到这里从PL控制DDR的读写基本就已经成功了,但是两个地方都是07c0,到底是为什么?还有待进一步研究,文档全是英文的,看起来有点吃力,进度可能会比较慢

by the way , Jeff Johnson also has a good tutorial on using AXI DMA: http://www.fpgadeveloper.com/2014/08/using-the-axi-dma-in-vivado.html ,感兴趣的可以参考一下

标签:

原文地址:http://www.cnblogs.com/christsong/p/5689750.html