标签:直接映射 结构 硬件 变换 替换 原理 芯片 操作 概率

2017-02-22

注:本文并非原创,来自百度文库,只是觉得写得较好,故分享之。若是某人的知识产权,望告知!谢谢

1.高速缓冲存储器的功能、结构与工作原理

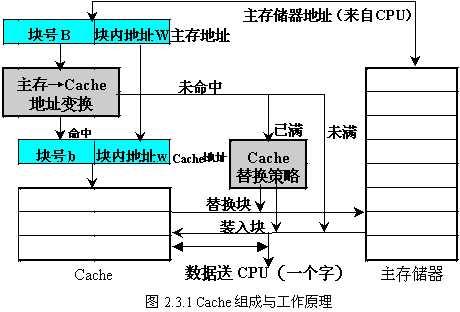

高速缓冲存储器是存在于主存与CPU之间的一级存储器, 由静态存储芯片(SRAM)组成,容量比较小但速度比主存高得多, 接近于CPU的速度。 Cache的功能是用来存放那些近期需要运行的指令与数据。目的是提高CPU对存储器的访问速度。为此需要解决2个技术问题:一是主存地址与缓存地址的映象及转换; 二是按一定原则对Cache的内容进行替换。Cache的结构和工作原理如图2.3.1所示。

主要由三大部分组成:

2.地址映象与转换

地址映象是指某一数据在内存中的地址与在缓冲中的地址,两者之间的对应关系。下面介绍三种地址映象的方式。

1.全相联方式

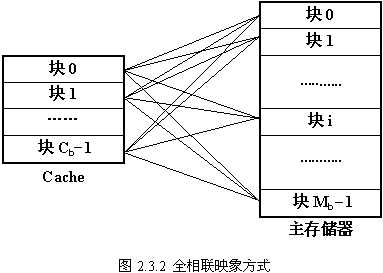

地址映象规则:主存的任意一块可以映象到Cache中的任意一块

(1) 主存与缓存分成相同大小的数据块。

(2) 主存的某一数据块可以装入缓存的任意一块空间中。

全相联方式的对应关系如图2.3.2所示。如果Cache的块数为Cb,主存的块数为Mb,则映象关系共有Cb×Mb种。

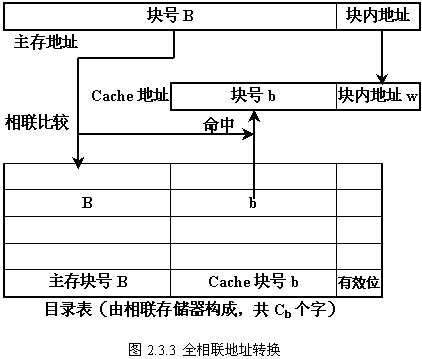

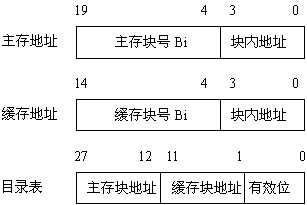

图2.3.3示出了目录表的格式及地址变换规则。 目录表存放在相关(联)存储器中,其中包括三部分:数据块在主存的块地址、存入缓存后的块地址、及有效位(也称装入位)。由于是全相联方式,因此,目录表的容量应当与缓存的块数相同。

举例:某机主存容量为1M,Cache的容量为32KB, 每块的大小为16个字(或字节)。 划出主、缓存的地址格式、 目录表格式及其容量。

容量:与缓冲块数量相同即211=2048(或32K/16=2048)。

优点:命中率比较高,Cache存储空间利用率高。

缺点:访问相关存储器时,每次都要与全部内容比较,速度低,成本高,因而应用少。

2.直接相联方式

地址映象规则: 主存储器中一块只能映象到Cache的一个特定的块中。

(1) 主存与缓存分成相同大小的数据块。

(2) 主存容量应是缓存容量的整数倍,将主存空间按缓存的容量分成区,主存中每一区的块数与缓存的总块数相等。

(3) 主存中某区的一块存入缓存时只能存入缓存中块号相同的位置。

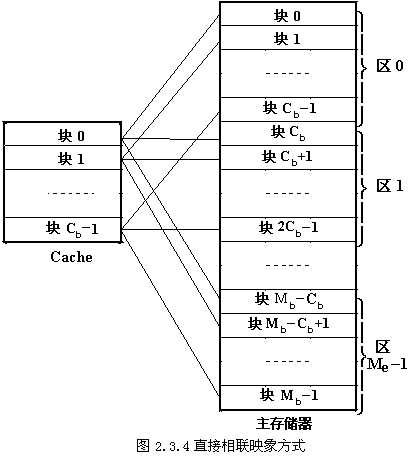

图2.3.4示出了直接相联映象规则。 可见,主存中各区内相同块号的数据块都可以分别调入缓存中块号相同的地址中,但同时只能有一个区的块存入缓存。由于主、缓存块号相同,因此,目录登记时,只记录调入块的区号即可。

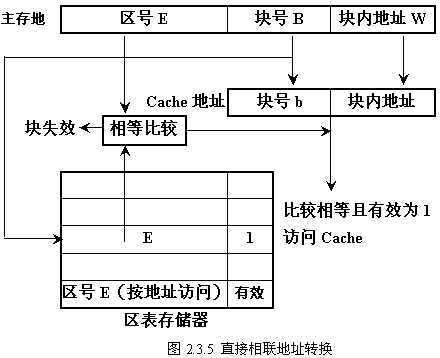

图2.3.5示出了主、 缓冲地址格式、目录表的格式及地址变换规则。主、缓存块号及块内地址两个字段完全相同。目录表存放在高速小容量存储器中,其中包括二部分:数据块在主存的区号和有效位。目录表的容量与缓存的块数相同。

地址变换过程:用主存地址中的块号B去访问目录存储器, 把读出来的区号与主存地址中的区号E进行比较, 比较结果相等,有效位为1,则Cache命中,可以直接用块号及块内地址组成的缓冲地址到缓存中取数;比较结果不相等,有效位为1, 可以进行替换,如果有效位为0,可以直接调入所需块。

优点:地址映象方式简单,数据访问时,只需检查区号是否相等即可,因而可以得到比较快的访问速度,硬件设备简单。

缺点:替换操作频繁,命中率比较低。

举例:上例中,主存容量为1M, Cache的容量为32KB,每块的大小为16个字(或字节)。划出主、缓存的地址格式、目录表格式及其容量。

容量:与缓冲块数量相同即211=2048(或32K/16=2048)。

3.组相联映象方式

组相联的映象规则:

(1) 主存和Cache按同样大小划分成块。

(2) 主存和Cache按同样大小划分成组。

(3) 主存容量是缓存容量的整数倍,将主存空间按缓冲区的大小分成区,主存中每一区的组数与缓存的组数相同。

(4) 当主存的数据调入缓存时,主存与缓存的组号应相等,也就是各区中的某一块只能存入缓存的同组号的空间内,但组内各块地址之间则可以任意存放, 即从主存的组到Cache的组之间采用直接映象方式;在两个对应的组内部采用全相联映象方式。

图2.3.6示出了组相联的映象关系, 图中缓存共分Cg个组,每组包含有Gb块; 主存是缓存的Me倍,所以共分有Me个区, 每个区有Cg组,每组有Gb块。那么, 主存地址格式中应包含4个字段:区号、区内组号、组内块号和块内地址。 而缓存中包含3个字段:组号、组内块号、块内地址。主存地址与缓存地址的转换有两部分,组地址是按直接映象方式,按地址进行访问,而块地址是采用全相联方式,按内容访问。组相联的地址转换部件也是采用相关存储器实现,见图2.3.7。

相关存储器中每个单元包含有: 主存地址中的区号E与组内块号B,两者结合在一起,其对应的字段是缓存块地址b。相关存储器的容量,应与缓存的块数相同。当进行数据访问时,先根据组号,在目录表中找到该组所包含的各块的目录,然后将被访数据的主存区号与组内块号,与本组内各块的目录同时进行比较。如果比较相等,而且有效位为“1”则命中。

可将其对应的缓存块地址b送到缓存地址寄存器的块地址字段,与组号及块内地址组装即形成缓存地址。如果比较不相等,说明没命中,所访问的数据块尚没有进入缓存,则进行组内替换;如果有效位为0,则说明缓存的该块尚未利用, 或是原来数据作废,可重新调入新块。

优点:块的冲突概率比较低,块的利用率大幅度提高,块失效率明显降低。

缺点:实现难度和造价要比直接映象方式高。

Cache与主存之间的全相联映射,直接映射和组相联映射的区别

标签:直接映射 结构 硬件 变换 替换 原理 芯片 操作 概率

原文地址:http://www.cnblogs.com/ck1020/p/6428293.html