标签:无限 conf gem 信号 res 时间 操作 比较 get

MII Management interface用于MAC层或其他控制芯片(不一定是MAC层芯片,可能是MCU,如高通芯片建构中,1个MAC芯片可以控制2个PHY芯片,然后MCU控制3个网卡(MAC+2PHY)芯片)控制、配置PHY层芯片。

Through MII Management interface it is possible to control and configure multiple PHY devices, get status and error infomation, and determine the type and capabilities of the attached PHY device(s).

MDIO接口包括两根信号线:MDC和MDIO,通过它,MAC层芯片(或其它控制芯片)可以访问物理层芯片的寄存器,并通过这些寄存器来对物理层芯片进行控制和管理。MDIO管理接口如下:

MDC:管理接口的时钟,它是一个非周期信号,信号的最小周期(实际是正电平时间和负电平时间之和)为400ns,最小正电平时间和负电平时间为160ns,最大的正负电平时间无限制。它与TX_CLK和RX_CLK无任何关系。

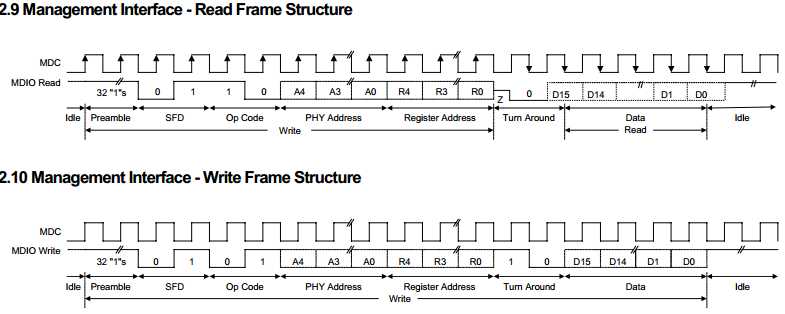

MDIO是一根双向的数据线,用来传送MAC层的控制信息和物理层的状态信息。MDIO数据与MDC时钟同步,在MDC上升沿有效。MDIO管理接口的数据帧结构如:

图MDIO管理接口的数据帧结构

In read/write operation, the management data frame is 64-bits long and starts with 32 contiguous logic one bits (preamble) synchronization clock cycles on MDC. The Start of Frame Delimiter (SFD) is indicated by a <01> pattern followed by the operation code (OP):<10> indicates Read operation and <01> indicates Write operation. For read operation, a 2-bit turnaround (TA) filing between Register Address field and Data field is provided for MDIO to avoid contention. Following the turnaround time, 16-bit data is read from or written onto management registers.

帧结构各域的含义如下:

PRE:帧前缀域,为32个连续“1”比特,这帧前缀域不是必要的,某些物理层芯片的MDIO操作就没有这个域。

ST:帧开始标志,出现“01”比特表示帧设计开始。

OP:帧操作码,比特“10”表示此帧为读操作帧,比特“01”表示此帧为写操作帧。

PHYAD:物理层芯片的地址,5个比特,每个芯片都把自己的地址与这5个比特进行比较,若匹配则响应后面的操作,若不匹配,则忽略掉后面的操作。

REGAD:用来选择物理层芯片的32个寄存器中的某个寄存器的地址。

TA:状态转换域,若为读操作,则第一比特时MDIO为高阻态,第二比特时由物理层芯片使MDIO置“0”。若为写操作,则MDIO仍由MAC层芯片控制,其连续输出“10”两个比特。

DATA:帧的寄存器的数据域,16比特,若为读操作,则为物理层送到MAC层的数据,若为写操作,则为MAC层送到物理层的数据。

IDLE:帧结束后的空闲状态,此时MDIO无源驱动,处高阻状态,但一般用上拉电阻使其处在高电平,即MDIO引脚需要上拉电阻。

注:上述图片及英文来自“DM9161a数据手册”

标签:无限 conf gem 信号 res 时间 操作 比较 get

原文地址:http://www.cnblogs.com/embedded-linux/p/6659828.html