本次介绍用Vivado构建Zedboard开发板的硬件平台+SDK开发应用程序(Zedboard裸机开发)

过程如下:

一、运行Vivado,建立新工程

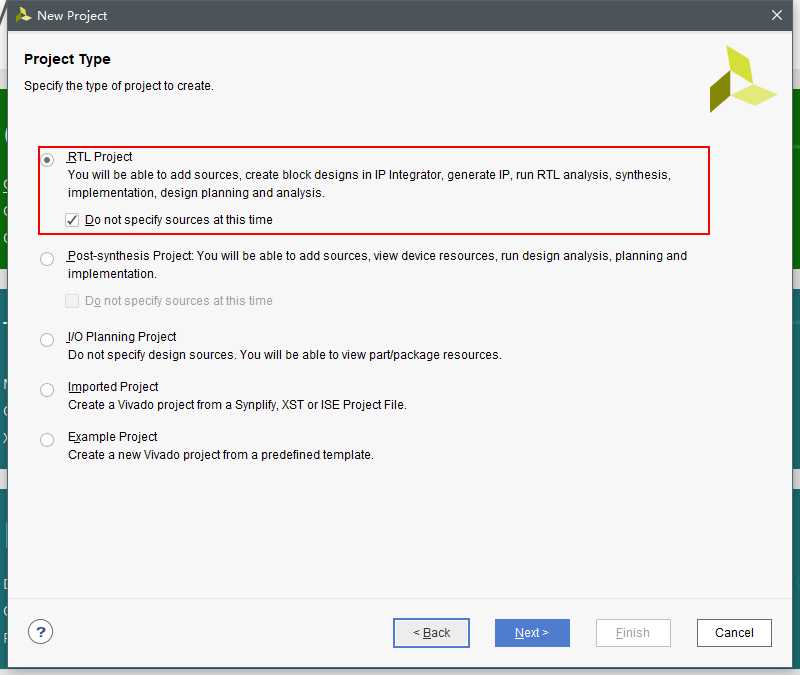

指定好工程路径,下一步,选择RTL Project,勾选“Do not specify sources at this time”(先不添加源文件和引脚约束)

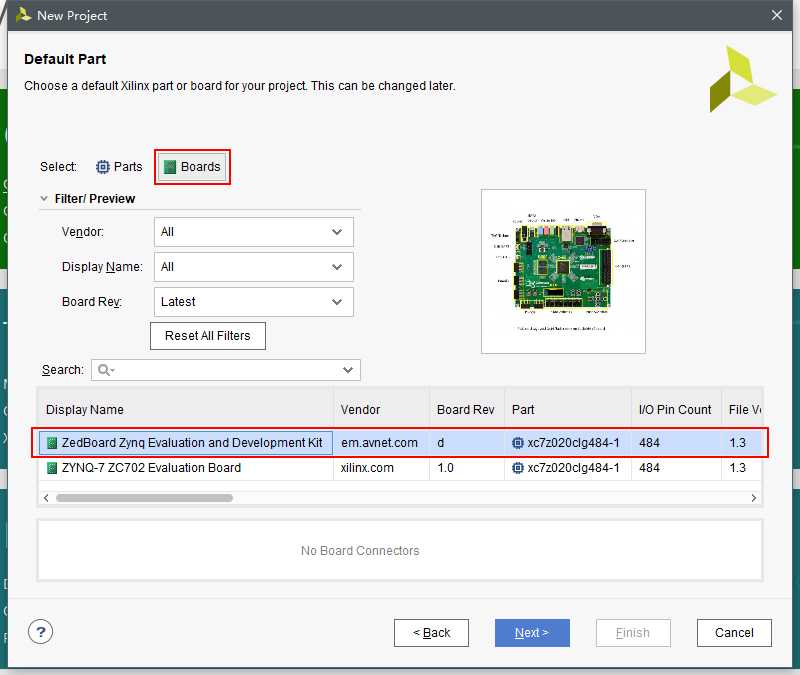

接下来选择对应的开发板,勾选Board,选择Zedboard XXXX

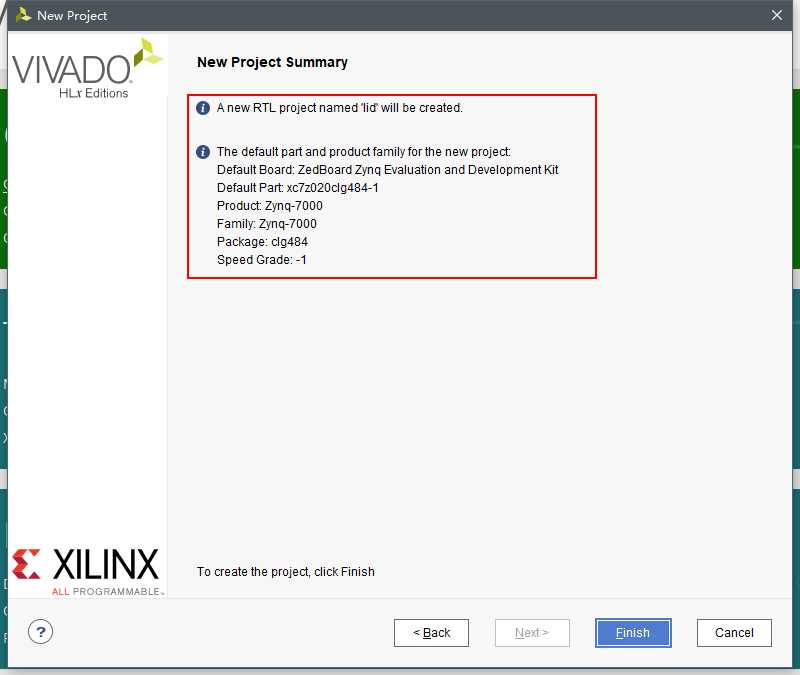

最后的界面显示了新建工程的相关信息:

点击finish完成。

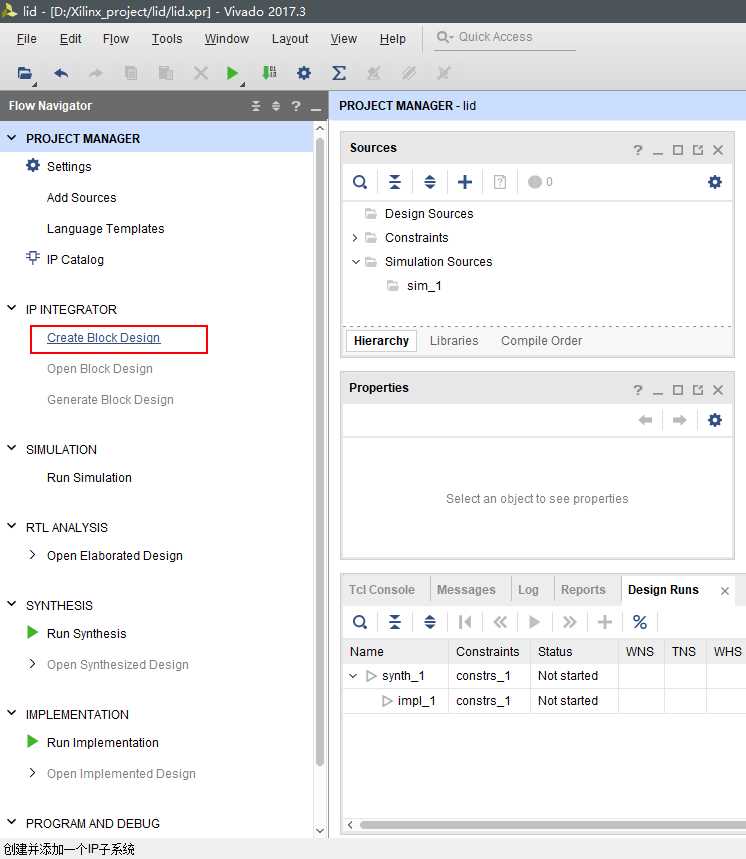

二、添加处理器zynq-7000(IP)内核

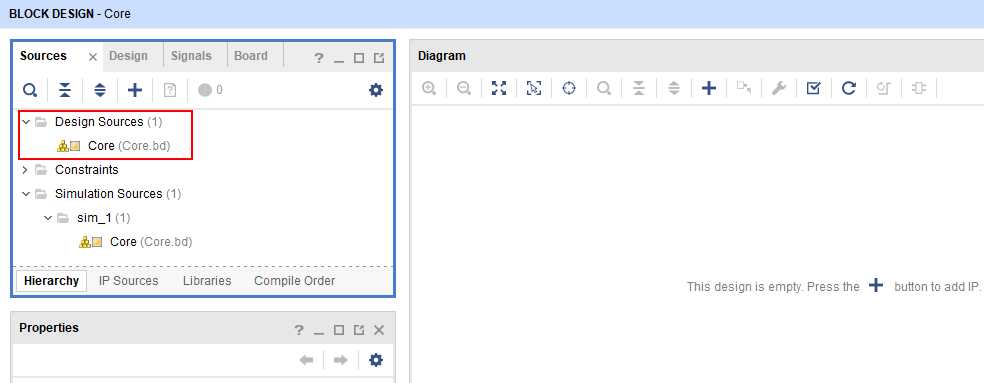

点击左侧菜单栏Flow Navigator->IP Intergrstor->Create Block Design

填上名字,选好所在文件夹(其实就是下图的Sources)

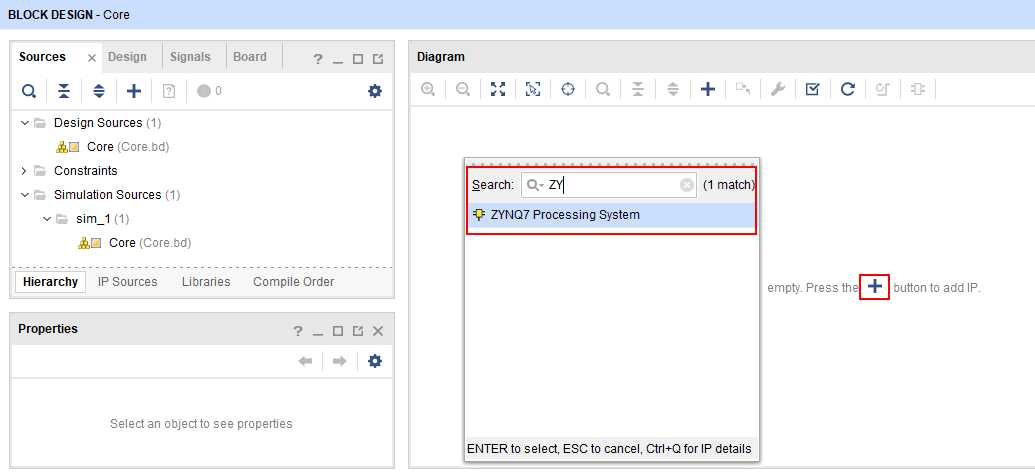

点击开发界面中的Add IP的加号,通过输入关键词来搜索需要添加的IP核

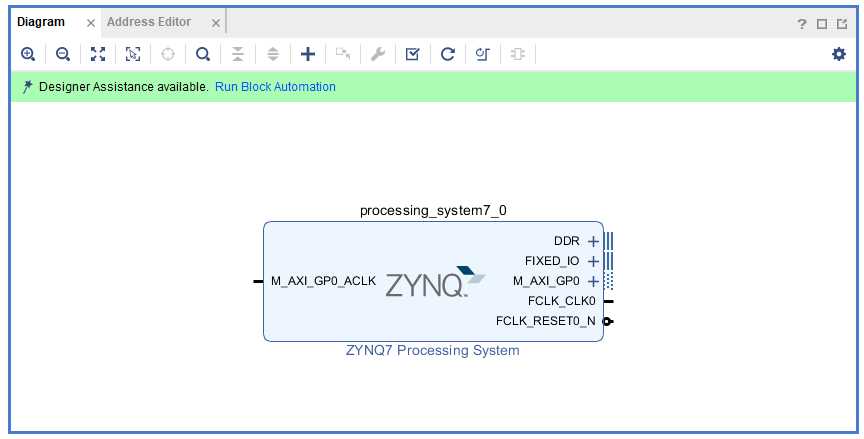

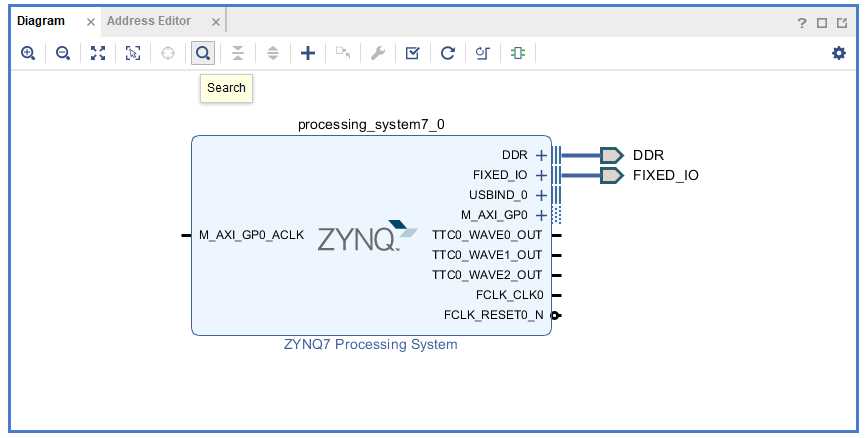

选中IP核后,系统会以图形界面的形式把IP核显示出来:

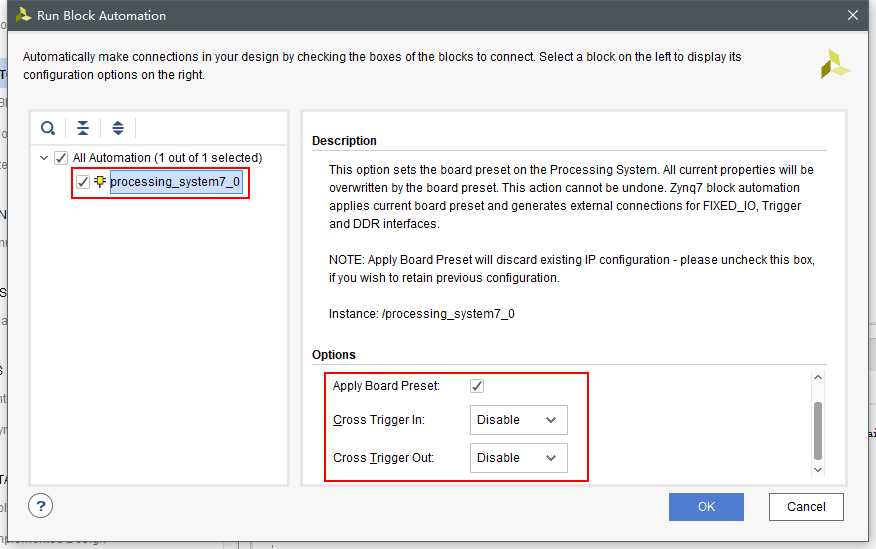

点击上图浅绿色条带中的Run Block Automation

勾选apply board preset,将这个IP核相关的输入/输出信号映射到芯片具体的引脚上,并添加必要的约束。

点击OK按钮后启动自动化,完成后结果如下图:

通过双击图中的IP核(图案会变成橙色)可以更改其内部配置。

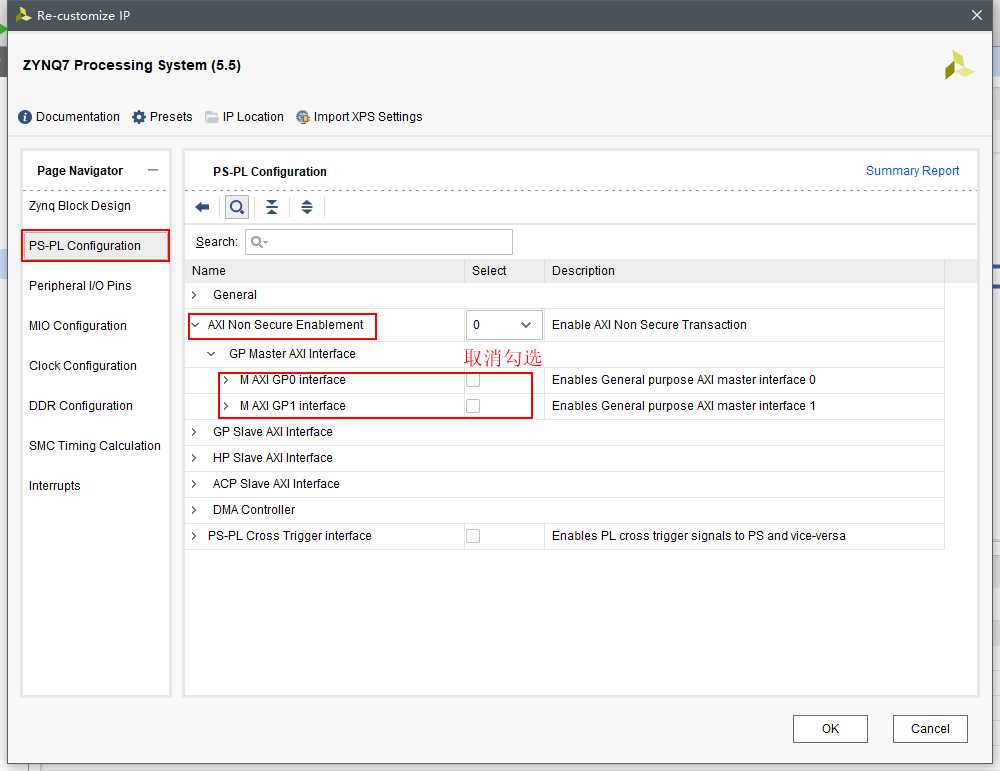

默认状态下使能了M_AXI_GP0,可以将PL部分带AXI从接口的IP连接到PS进行控制。这里我们暂时不用到PL部分,所以把其禁用,否则验证设计时会报错。双击方块,见下图

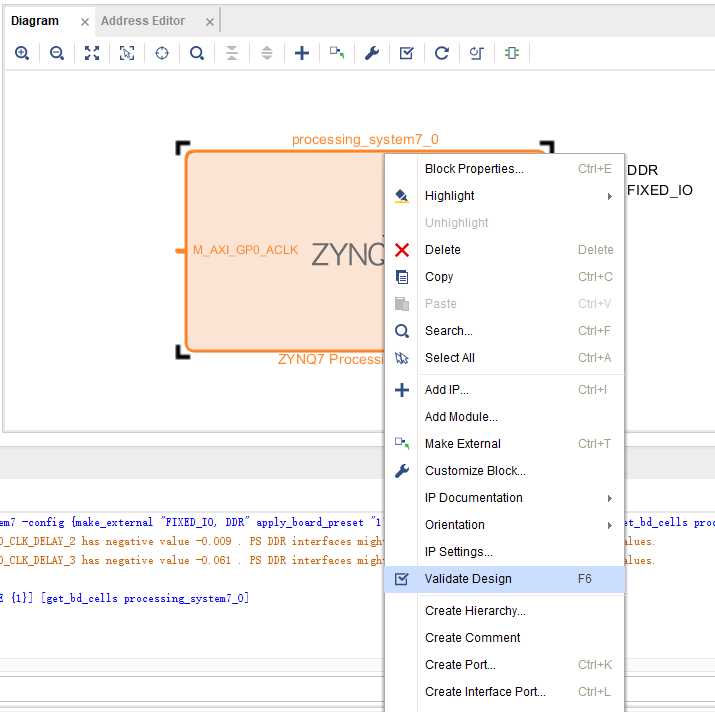

完成配置后,右击图案,选择“Validate Design”进行规则检查。

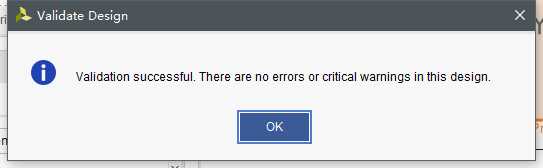

如果没错误则出现以下提示:

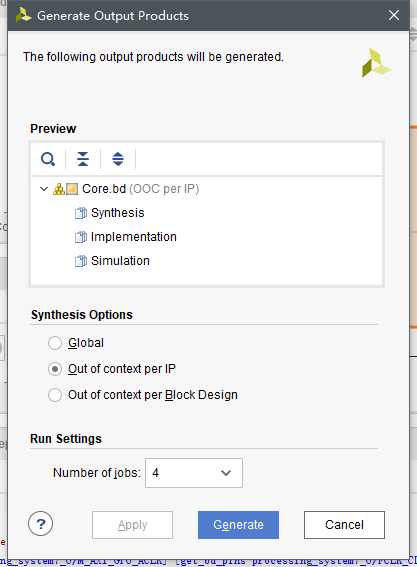

接下来是生成输出文件并封装成HDL形式

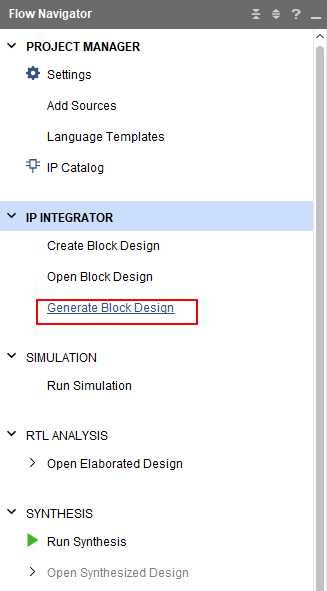

为上述添加的模块生成相关的综合、实现及仿真文件,点击Flow Navigator->IP Intergrstor->Generator Block Design

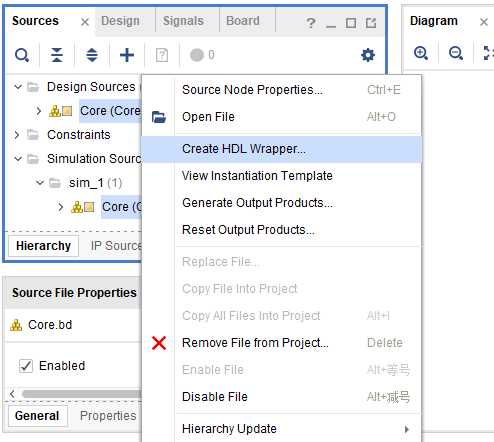

生成输出文件后,将其封装成顶层HDL文件,Source窗口右击core(添加的IP核名字),选择Create HDL Wrapper

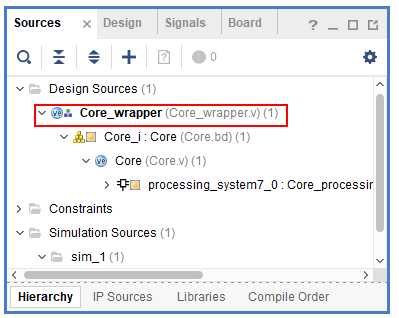

完成后,Source窗口多了一个HDL文件Core_wrapper.v

至此,我们完成了一个IP核的内部设计并将其封装成基本的HDL形式(可以作为一个模块被其他设计调用),接下来就可以进行RTL分析、综合、实现和生成硬件比特流文件

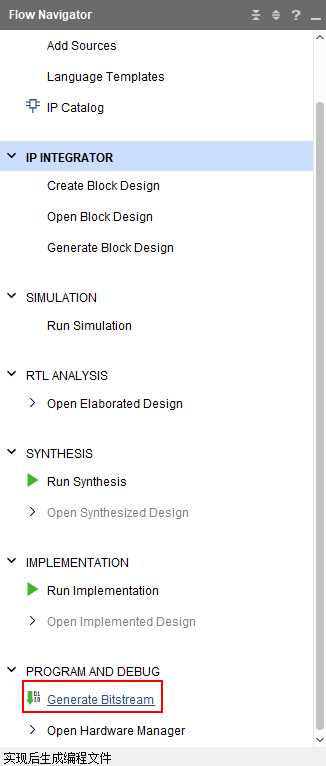

下一步,我们将生成比特流文件:

左侧导航栏Flow Navigator->Program and Debug->Generate Bitstream,如果之前没有进行综合和实现,则系统会提示是否进行,点击yes即可。

三、使用SDK完成软件开发

在上一步中我们已经完成了处理器硬件架构的设计,如果此时将比特流文件下载到ZYNQ-7000芯片内部,则此时的芯片将是一款用户自己定制的处理器,但它还缺乏软件程序。

这一节,我们将硬件平台信息导入到SDK

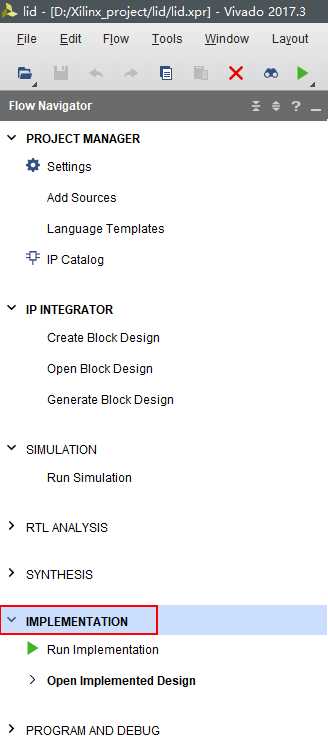

打开工程core,选择IMPLEMENTATION(这一步是必须的,否则后面会报错)

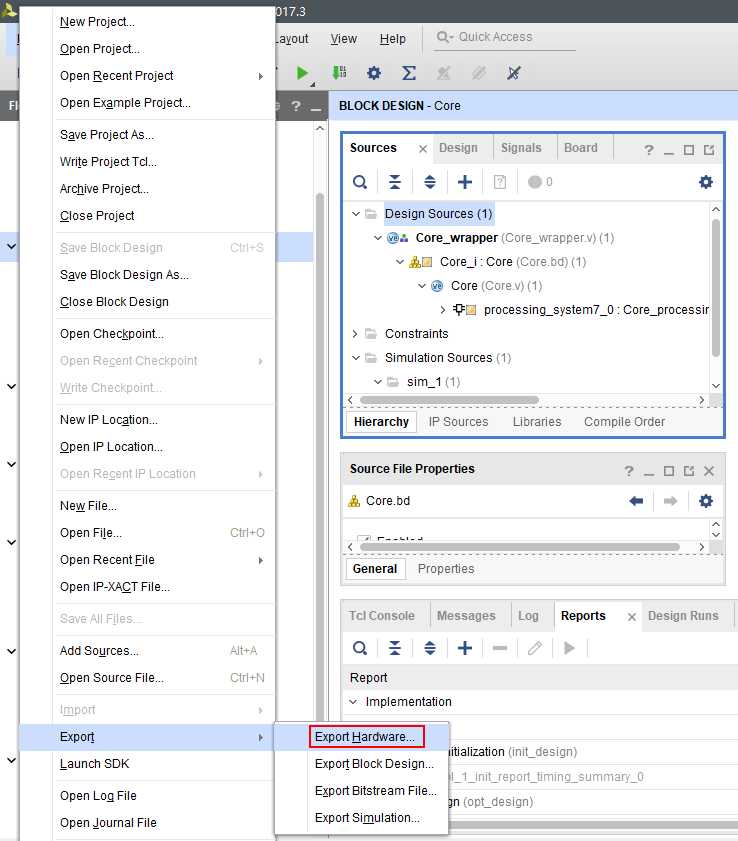

接着File->Exprot->Exprot Hardware for SDK,将硬件平台信息、硬件比特文件全部导入SDK平台并打开SDK软件(打开后SDK的system.hdf就是)

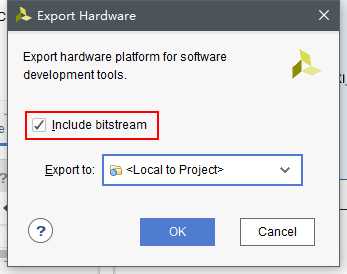

注意勾选加入比特流文件

生成完成好,我们就完成了硬件平台的构建,下一步就是进入SDK进行应用软件开发了。

File->Launch SDK,SDK开始运行。

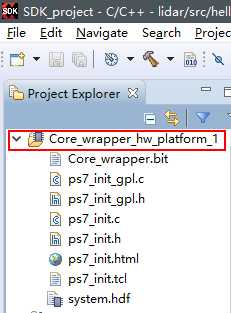

左侧栏可以看到硬件平台信息已经被导入。

下一步是创建BSP(板级驱动包)和Application Project(应用程序)

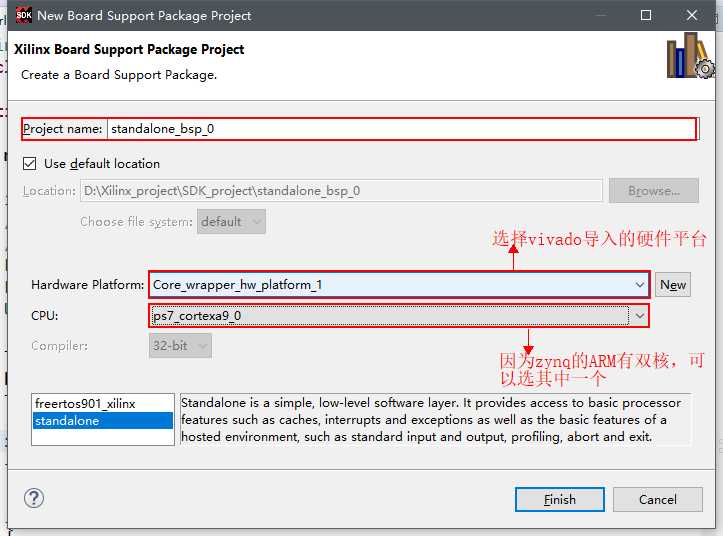

BSP是在硬件平台上运行程序必不可少的组件,在SDK中选择File->New->Board Support Package

*裸机开发选standalone

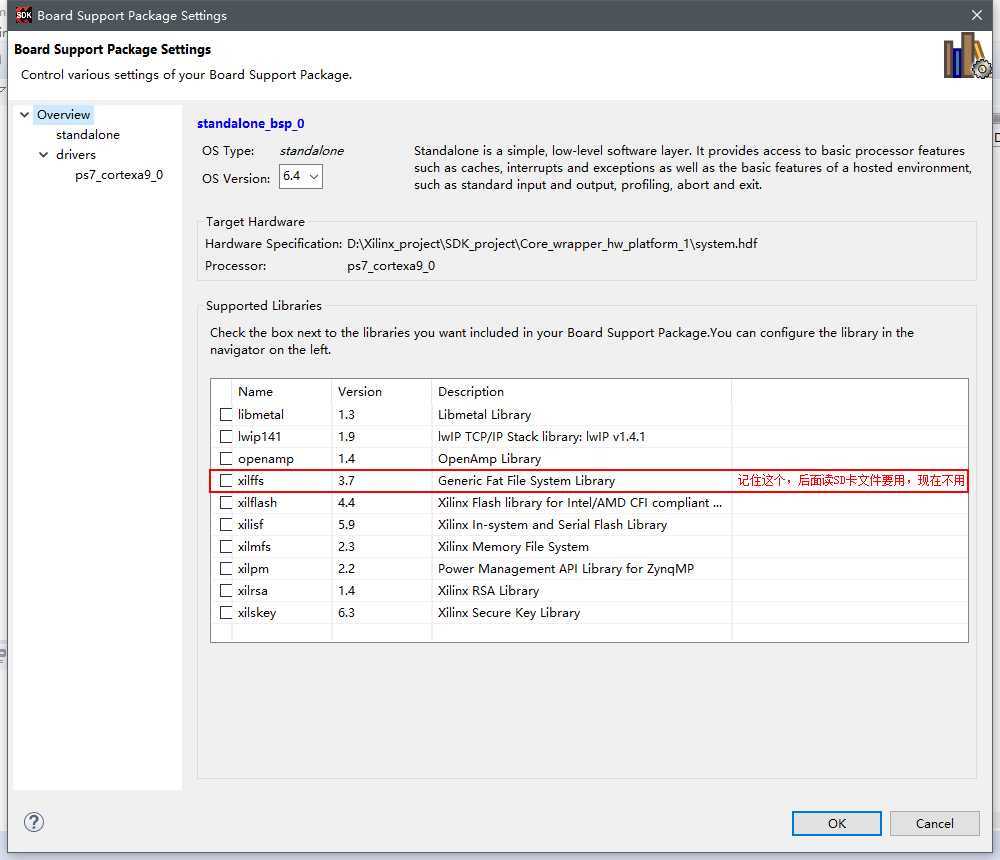

点击finish以后会出现新创建BSP的配置信息:

这里我们默认配置即可,点OK

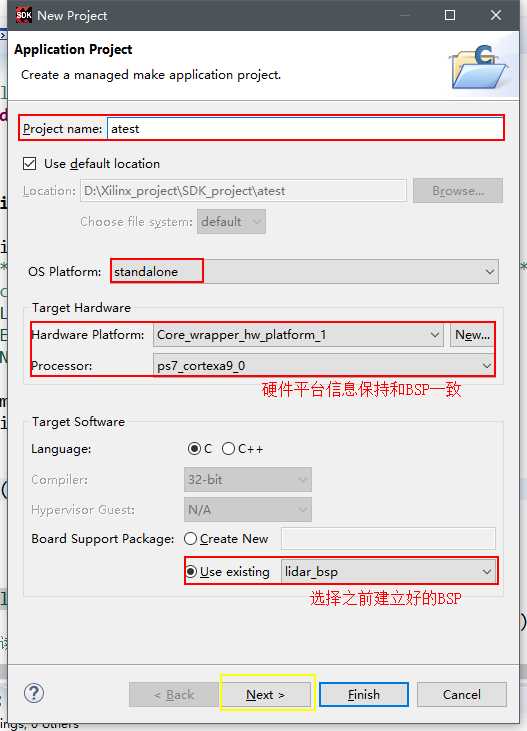

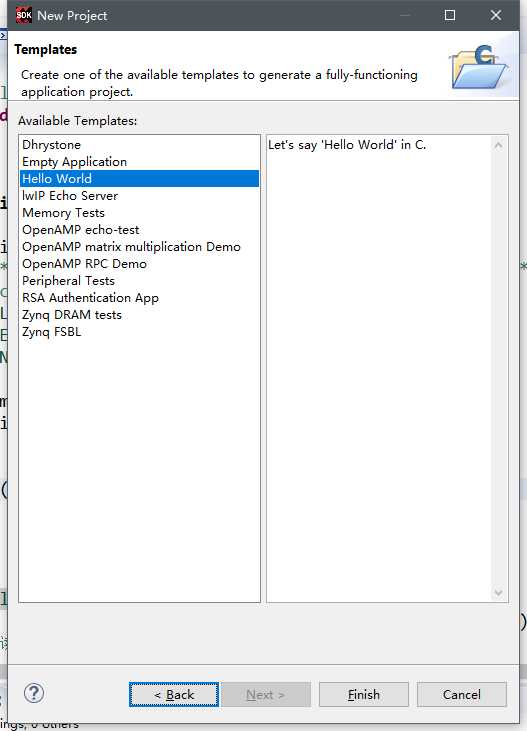

接下来就是建立应用工程,在SDK中选择File->New->Application Project

命名和选择信息,完成后点击Next,

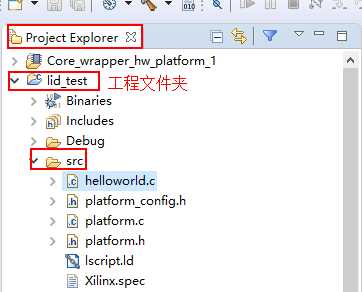

选择Hello World作为工程模板,Finish。这时左侧的工程浏览器就出现了刚刚建立的工程文件夹,下拉菜单src中找到helloworld.c,双击就可以编辑了

编辑好代码,点击保存 ,然后编译

,然后编译

在console中查看编译报告,如果没有出现错误,则编译成功。下一步就可以连接Zedboard进行板级调试了。

四、进行板级调试

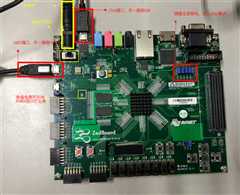

完成应用程序的编写并编译成功以后,下一步便是连接PC和Zedboard进行调试。

首先需要2根Micro-USB连接线,分别连接J14(UART)和J17(JTAG),如下图所示。

这里稍微说明下J14和J17两个接口的作用:

(1)J14是USB转UART串口,在这里是用来输出板卡的信息的(比如最简单是输出“Hello World”语句,要连接这条线才能在SDK的Console中显示)

(2)J17是USB-JTAG配置端口,用来配置板卡信息

连接好线后,将跳帽JP7-11全部接地(进入JTAG模式),如下图所示:

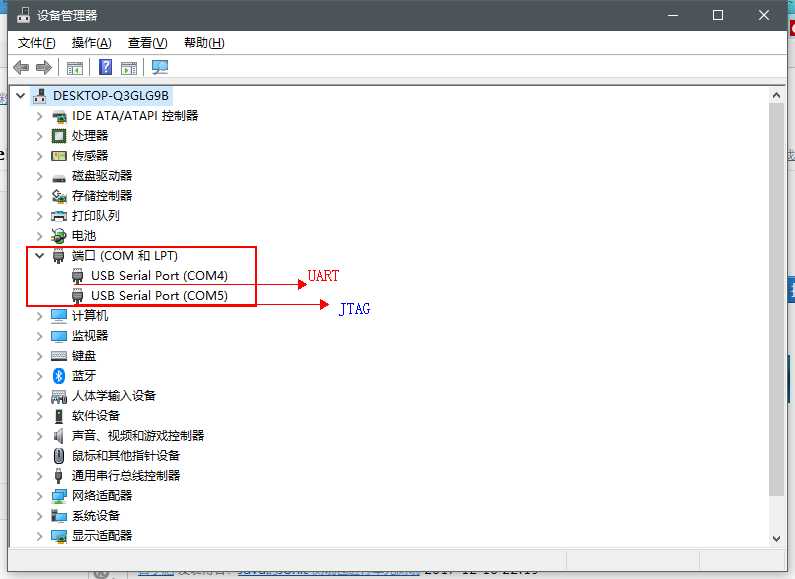

接通Zedboard电源,打开电源开关ON,通过PC的“设备管理器”,查看端口。

注意要辨别哪个COM端口是UART的,后面要用到。

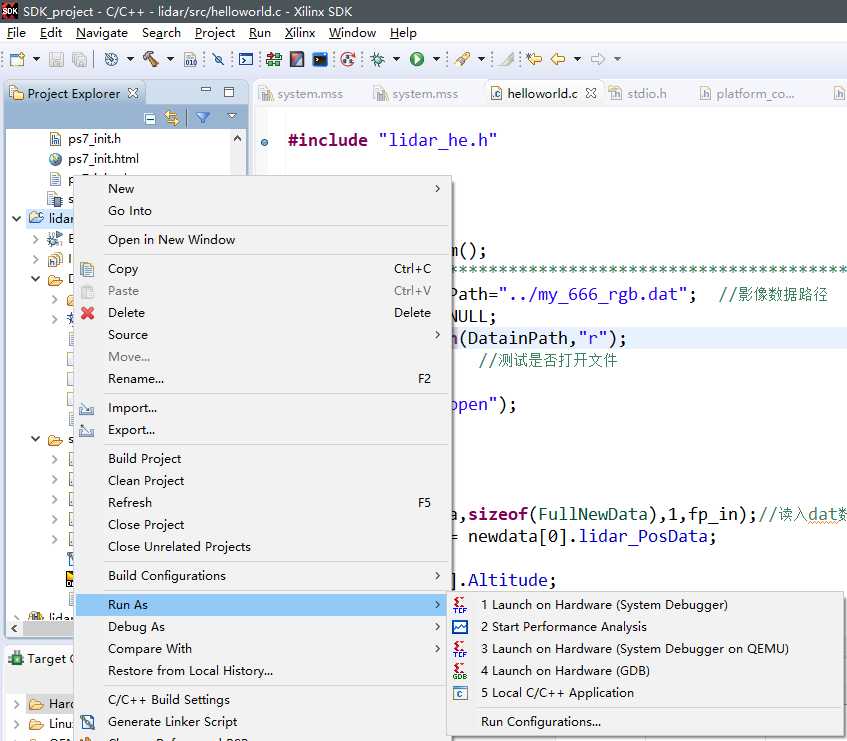

回到SDK,右击工程lidar->Run As->Run configurations

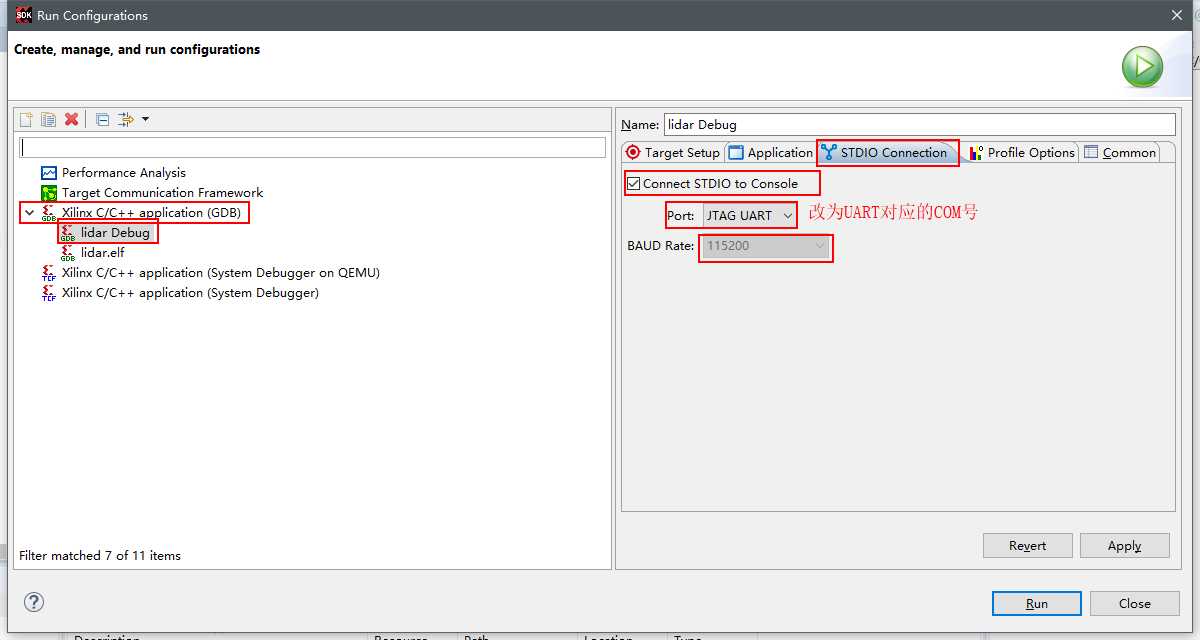

双击Xilinx C/C++ application(GDB),出现“工程名 Debug”,选中后选中右侧的STDIO Connection页

勾选"connect STDIO xxxx",将Port下拉选中UART对应的COM号(比如我的是COM4),下面是数值设置为115200,点击Apply然后Close

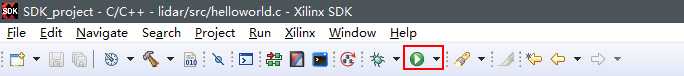

设置好以后,我们就可以开始板级调试了,点击菜单栏的 按钮进入Run模型(当然在上面你Apply之后直接点Run也是一样的效果)

按钮进入Run模型(当然在上面你Apply之后直接点Run也是一样的效果)

*如果是要一步一步调试,则点击 按钮,进入Debug模式。

按钮,进入Debug模式。

*可能会提示没有配置FPGA,跳过就好。

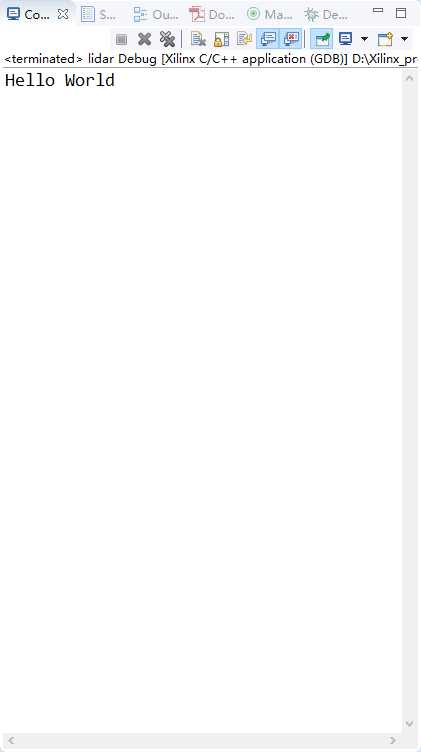

通过Console就可以查看输出了。

至此,一个简单的应用程序就完成了。

回顾一下,整个流程下来包括了以下几个阶段:

1.搭建硬件平台(在vivado中进行)

2.将硬件平台信息(包括比特流文件)导入SDK

3.在SDK中建立驱动包和应用工程

4.连接PC和开发板,进行板级调试