标签:有一个 技术 rowspan font 算术运算 无符号 ble 情况下 x86

CPU资源和存储器

在汇编语言中,需要访问的硬件资源主要有:CPU内部资源、存储器和I/O端口。本章将着重讲解CPU内部寄存器的命名、功能及其常见的用途,还要介绍存储器的分段管理模式、存储单元地址的表示法以及其物理地址的形成方式。

2.1 寄存器组

寄存器是CPU内部重要的数据存储资源,是汇编程序员能直接使用的硬件资源之一。由于寄存器的存取速度比内存快,所以,在用汇编语言编写程序时,要尽可能充分利用寄存器的存储功能。

寄存器一般用来保存程序的中间结果,为随后的指令快速提供操作数,从而避免把中间结果存入内存,再读取内存的操作。在高级语言(如:C/C++语言)中,也有定义变量为寄存器类型的,这就是提高寄存器利用率的一种可行的方法。

另外,由于寄存器的个数和容量都有限,不可能把所有中间结果都存储在寄存器中,所以,要对寄存器进行适当的调度。根据指令的要求,如何安排适当的寄存器,避免操作数过多的传送操作是一项细致而又周密的工作。有关“寄存器的分配策略”在后续课程《编译原理》中会有详细的介绍。

由于16位/32位CPU是微机CPU的两个重要代表,所以,在此只介绍它们内部寄存器的名称及其主要功能。

2.1.1 寄存器组

1、 16位寄存器组

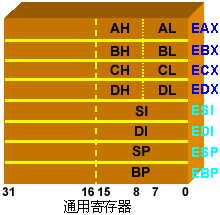

16位CPU所含有的寄存器有(见图2.1中16位寄存器部分):

4个数据寄存器( AX、BX、CX、DX );

2个变址和指针寄存器( SI、DI );

2个指针寄存器( SP、BP );

1个指令指针寄存器( IP );

1个标志寄存器( Flags );

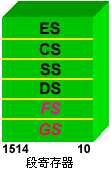

4个段寄存器(ES、CS、SS、DS );

2、 32位寄存器组

32位CPU除了包含了先前CPU的所有寄存器,并把通用寄存器、指令指针和标志寄存器从16位扩充成32位之外,还增加了2个16位的段寄存器:FS和GS。

32位CPU所含有的寄存器有(见图2.1中的寄存器):

4个数据寄存器( EAX、EBX、ECX、EDX );

2个变址和指针寄存器( ESI、EDI );

2个指针寄存器( ESP、EBP );

1个指令指针寄存器( EIP );

1个标志寄存器( EFlags );

6个段寄存器( ES、CS、SS、DS、FS、GS );

图2.1 CPU寄存器组的示意图

2.1.2、通用寄存器的作用

通用寄存器可用于传送和暂存数据,也可参与算术逻辑运算,并保存运算结果。除此之外,它们还各自具有一些特殊功能。汇编语言程序员必须熟悉每个寄存器的一般用途和特殊用途,只有这样,才能在程序中做到正确、合理地使用它们。

表2.1 通用寄存器的主要用途

| 寄存器的分类 | 寄存器 |

主 要 用 途 |

|

| 通

用 寄 存 器 |

数据

寄存器 |

AX |

乘、除运算,字(16位)的输入输出,中间结果的缓存(AX=AH+AL) |

| AL |

字节(8位)的乘、除运算,字节的输入输出,十进制算术运算 |

||

| AH |

字节(8位)的乘、除运算,存放中断的功能号 |

||

| BX |

存储器指针 |

||

| CX |

串操作、循环控制的计数器 |

||

| CL |

移位操作的计数器 |

||

| DX |

字(16位)的乘、除运算,间接的输入输出 |

||

| 变址 寄存器 |

SI |

存储器指针、串指令中的源操作数指针 |

|

| DI |

存储器指针、串指令中的目的操作数指针 |

||

| 变址 寄存器 |

BP |

存储器指针、存取堆栈的指针 |

|

| SP |

堆栈的栈顶指针 |

||

|

指令指针 |

IP/EIP | ||

| 标志位寄存器 | Flag/EFlag | ||

| 32位

CPU的 段寄存器 |

16位CPU的

段寄存器 |

ES | 附加段寄存器 |

| CS | 代码段寄存器 | ||

| SS | 堆栈段寄存器 | ||

| DS | 数据段寄存器 | ||

| 新增加的 段寄存器 |

FS | 附加段寄存器 | |

| GS | 附加段寄存器 | ||

更详细的内容请点击:汇编语言从入门到精通-通用寄存器功能的说明。

2.1.3、专用寄存器的作用

16位CPU内部有一个16位的标志寄存器,它包含9个标志位。这些标志位主要用来反映处理器的状态和运算结果的某些特征。各标志位在标志寄存器内的分布如图2.2所示。

|

| 31 | … | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| … | … | VM | RF | NT | IOPL | OF | DF | IF | TF | SF | ZF | AF | PF | CF |

图2.2 16位/32位标志寄存器的示意图

上面9个标志位可分为二组:运算结果标志位(有背景色的标志位)和状态控制标志位。前者受算术运算和逻辑运算结果的影响,后者受一些控制指令执行的影响。(还不太明白)

更详细的内容请点击:汇编语言从入门到精通-标志位的说明。

有些指令的执行会改变标志位(如:算术运算指令等),不同的指令会影响不同的标志位,有些指令的执行不改变任何标志位(如:MOV指令等),有些指令的执行会受标志位的影响(如:条件转移指令等),也有指令的执行不受其影响。

程序员要想熟练运用这些标志位,就必须掌握每个标志位的含义、每条指令的执行条件和执行结果对标志位的作用。

注意:虽然知道每个标志位在标志寄存器内的具体位置是有好处的,但通常情况下,没有这个必要。在使用第5.2.9节中的“条件转移指令”时,系统会自动引用相应标志位的值来决定是否需要“转移”的,所以,不必过分强调标志位在标志寄存器内的具体位置。

2.2 存储器的管理模式

Intel公司的80X86系列的CPU基本上采用内存分段的管理模式。它把内存和程序分成若干个段,每个段的起点用一个段寄存器来记忆,所以,学习微机汇编语言,必须要清楚地理解存储器的分段含义、存储单元的逻辑地址和其物理地址之间的转换关系。

2.2.1 16位微机的内存管理模式

1、存储器的分段

我们知道:计算机的内存单元是以“字节”为最小单位进行线性编址的。为了标识每个存储单元,就给每个存储单元规定一个编号,此编号就是该存储单元的物理地址。

存储单元的物理地址是一个无符号的二进制数。但为了书写的简化,物理地址通常用十六进制来表示。

16位CPU内部有20根地址线,其编码区间为:00000H~0FFFFFH,所以,它可直接访问的物理空间为1M(220)字节。而16位CPU内部存放存储单元偏移量的寄存器(如:IP、SP、BP、SI、DI和BX等)都是16位,它们的编码范围仅为:00000H~0FFFFH。这样,如果用16位寄存器来访问内存的话,则只能访问内存的最低端的64K,其它的内存将无法访问。为了能用16位寄存器来有效地访问1M的存储空间,16位CPU采用了内存分段的管理模式,并引用段寄存器的概念。

|

16位微机把内存空间划分成若干个逻辑段,每个逻辑段的要求如下: |

图2.4 16位微机内存分段管理示意图 |

|

|

|

逻辑段的起始地址(通常简称为:段地址)必须是16的倍数,即最低4位二进制必须全为0; | |

|

|

逻辑段的最大容量为64K,这由16位寄存器的寻址空间所决定。 | |

|

按上述规定,1M内存最多可分成64K个段,即65536个段(段之间相互重叠),至少可分成16个相互不重叠的段。 右图2.4是内存各逻辑段之间的分布情况示意图,其中有相连的段(如:C和D段)、不相连的段(如:A和B段)以及相互重叠的段(如:B和C段)。 |

||

这种存储器分段的内存管理方法不仅实现了用两个16位寄存器来访问1M的内存空间,而且对程序的重定位、浮动地址的编码和提高内存的利用率等方面都具有重要的实用价值。

标签:有一个 技术 rowspan font 算术运算 无符号 ble 情况下 x86

原文地址:https://www.cnblogs.com/little-kwy/p/9738589.html