标签:教程 调试 向量 www. 开始 负数 文件 进制 状态机

0.模型训练:暂时跳过

CNN有监督,可以用BP训练:http://www.mamicode.com/info-detail-2288678.html

1.参数:

1.1一开始混乱的点

(1)每个核有一个bias,每个核出一个通道的结果(一个特征)。

(2)fcweight1:500行;fcweight1:10行;

(3)一组核:所求特征(输出)由多个子特征(输入)组成,每个子特征有一个核

1.2过程

(1)卷积一:输入28*28,20个核(5*5),20个bias(1*20),输出20通道24*24,算步长:28=5+(24-1)*步长,所以步长=1;

(2)卷积一池化:每2*2选一个最大值,无重合,规模横纵减半;

(3)卷积二:输入20通道12*12,20*50个核(50组核,一组核对应一个bias,得一个通道结果)(每个通道输入*对应组对应通道的核),50个bias,输出50通道8*8,12=5+7*1,步长=1;

(4)卷积二池化:减半

(5)全连接层一:输入50通道4*4,展开1*800,映射到1*500(全连接->每个输入都要乘weightN+biasN=iN,所以有500*800个参数,500个bias,:(500*800)* (800*1)=(500*1)+bias(500*1))

(6)全连接层一过滤:输入1*500,负数取正,输出1*500

(7)全连接层二:输入1*500,输出1*10:(10*500)*(500*1)=10*1+bias(10*1)

(8)输出:找到1*10向量中最大值,输出下标为识别结果

2.设计:看指导书

数据通路不要和控制写一起,控制单独写状态机!

(1)定点数问题:

参数和数据处理:转为8位二进制数(有符号,参数有负数)。运算后要移位?

教程:https://jingyan.baidu.com/article/f71d6037b3b43f1ab641d10d.html

处理成1符号+2整数+5小数,相当于一个数放大了2^5倍

原始数据*32=输入数据,还要看数据会不会溢出(大于3)

错误:

1.clock design生成.v文件后,再把里面的模块设成top,单独写仿真或综合时是找不到这个模块的,要把block design生成的.v文件删了之后才能找到。。。但是重启vivado后又可以直接改top了?妙

2.lia:https://blog.csdn.net/qq_34322603/article/details/72854621:

然后常规方法进入软件调试界面,设置断点。(这里提醒一下,联合调试一定要在SDK下将比特流下载到FPGA中,而不要在vivado中下载比特流。Xilinx官方给出的解释是:由于使用PS端的时钟来接入ILA,所以要现在SDK中将比特流进行下载)

3.verliog:一个信号只能有一个驱动,多个改变位置要加选择器。

4.加完debug后布线报错:

[Chipscope 16-213] The debug port ‘dbg_hub/clk‘ has 1 unconnected channels (bits). This will cause errors during implementation.

原因:综合之后没有选debug的设置,有的线还没有连时钟。给clk加debug好像有个buff报错解决不了,就把clk的debug删了

5.lia的wave出不来:要用sdk烧一遍才行。先用vivado 的hardware烧板子作为启动,然后用sdk烧,就能弹出来了。

6.#include "xil_io.h"报错:clean一遍编译

7.ila的wave图点运行就走一点点:可能是时钟没跑起来,需要抓的复杂一点,我加了一个axi数据就能起来了。也不知道为啥。

8.初始化的使能是必须加的,因为pl初始化好了之后ps可能还没开始传东西。。。要用axi-lite告诉初始化模块我要开始传有效数据了。

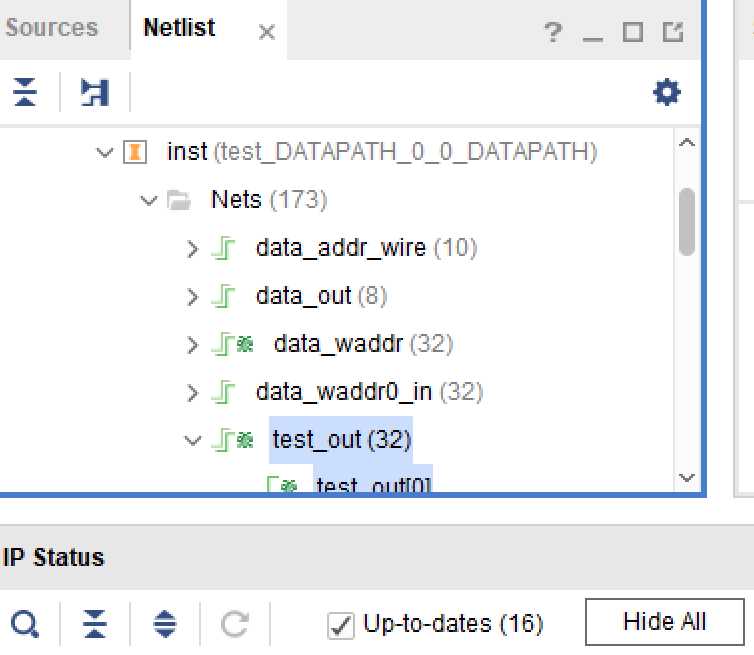

9.可以直接在netlist里面mark debug,要是写(**)没加进去的话

选上线右键mark debug就行。

选上线右键mark debug就行。

标签:教程 调试 向量 www. 开始 负数 文件 进制 状态机

原文地址:https://www.cnblogs.com/iwanna/p/10119221.html