标签:通用 时序 没有 其他 ios 51单片机 tor 驱动程序 tool

SOC固件(BIOS)开发:

1.熟悉硬件原理图:只要弄清楚pin脚的功能;

2.配置GPIO引脚,配置成Native功能还是GPIO功能(如果是配置成GPIO,需要在code里面显式的使用);

3.硬件驱动是通过controller的寄存器来访问device的:以IIC为例,如果SOC有IIC的controller,固件程序只需要配置IIC的GPIO为native功能,然后code里面通过读写IIC controller的寄存器就可以完成对IIC device的访问(IIC的硬件时序由硬件controller完成);如果没有IIC controller,则需要通过GPIO来模拟IIC的总线时序来实现对IIC device的访问(51单片机模拟IIC时序为例))

硬件编程需要掌握的规范(USB为例):

1.通用的工业规范,比如USB总线协议,USB Host controller协议:前者规定了比如时序的定义,后者定义了寄存器接口(可以理解为硬件厂商在实现USB controller的功能时需要提供给软件的接口,软件只需要按spec操作寄存器就行了,而时序是由硬件自动实现的);

2.硬件厂商的datasheet,除了上面的寄存器,厂商可能还会有其他的寄存器来实现自家特有的功能;

3.使用的系统软件的相关API与接口要求:比如UDK里面的硬件驱动实现的接口以PROTOCOL的形式提供给上层调用,而Linux下的驱动程序实现的接口表现为某种结构体。

从驱动程序的角度看硬件控制器,控制器就是一组寄存器:

1.驱动程序通过读写寄存器来初始化硬件控制器;

2.提供符合系统规范的接口(系统通过统一的接口访问不同的硬件):

在不同的软件系统里面写硬件驱动,需要熟悉软件系统的接口,比如软件系统提供的API,软件系统规定的驱动程序需要实现的接口。比如UDK里面的硬件驱动实现的接口以PROTOCOL的形式提供给上层调用,而Linux下的驱动程序实现的接口表现为某种结构体。

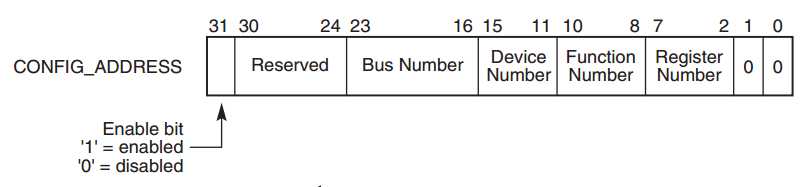

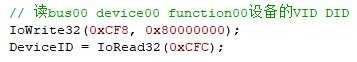

PCIe配置寄存器:通过IO CF8/CFC来访问。

Controller寄存器:Controller定义的寄存器,如果Controller是挂在pcie总线上,则controller寄存器的内存基地址由pcie的BAR寄存器指定。

其他寄存器:一般来说,有固定的内存地址(比如如果我们需要在系统下面查看某个GPIO的输出状态,可以通过查看code或者spec来计算出该GPIO的内存地址,在系统用tool查看该内存地址的值,看描述GPIO输出状态的那个个bit位就行了)。

CF8/CFC:访问PCIe配置空间(寄存器)

CF9:Reset Generator

IoWrite8(CF9, 0x6); //系统重启,不掉电 IoWrite8(CF9, 0xe); //系统重启,掉电

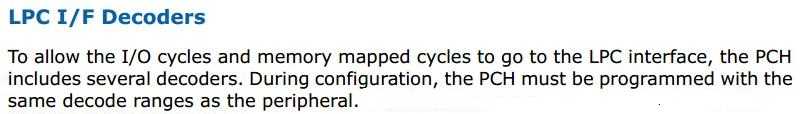

有些IO的操作是与EC通信的,这时需要map到LPC总线上:

80:一般来说,BIOS可以通过往port80写值来记录代码的运行,往port80写的值会通过LPC总线写到EC的RAM区域:

![]()

比如现在想要通过68/6c与EC通信:

1.配置LPC的68/6c的decode,这样对68/6c的访问就会map到LPC总线上;

2.EC需要配置,这样才能响应LPC总线上的68/6c的操作

标签:通用 时序 没有 其他 ios 51单片机 tor 驱动程序 tool

原文地址:https://www.cnblogs.com/nju347/p/10548289.html