标签:case pre mod reg 代码 xxxxxx input code ima

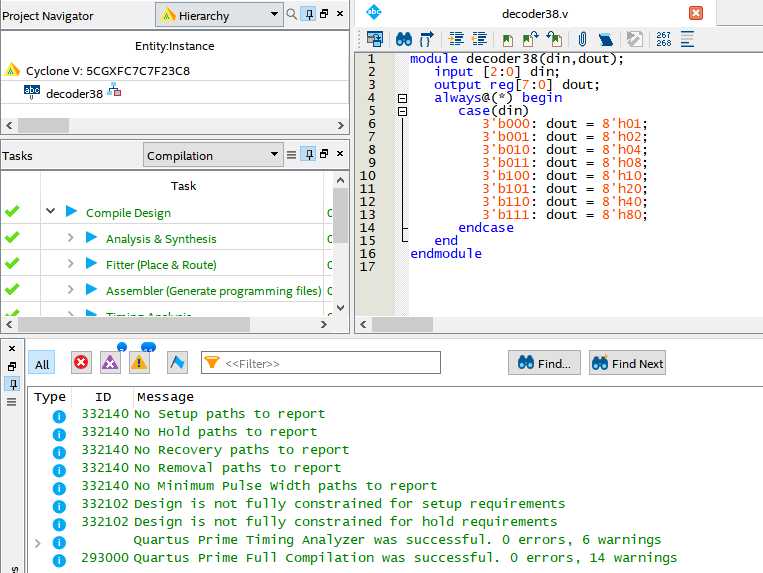

// case语句

module decoder38(din,dout);

input [2:0] din;

output reg[7:0] dout;

always@(*) begin

case(din)

3'b000: dout = 8'h01;

3'b001: dout = 8'h02;

3'b010: dout = 8'h04;

3'b011: dout = 8'h08;

3'b100: dout = 8'h10;

3'b101: dout = 8'h20;

3'b110: dout = 8'h40;

3'b111: dout = 8'h80;

endcase

end

endmodule

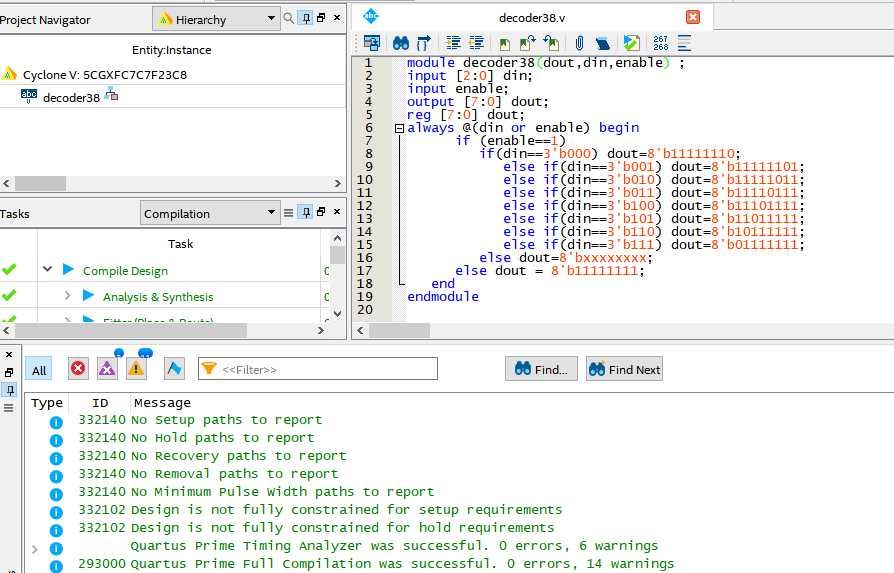

// if_case语句

module decoder38(dout,din,enable) ;

input [2:0] din;

input enable;

output [7:0] dout;

reg [7:0] dout;

always @(din or enable) begin

if (enable==1)

if(din==3'b000) dout=8'b11111110;

else if(din==3'b001) dout=8'b11111101;

else if(din==3'b010) dout=8'b11111011;

else if(din==3'b011) dout=8'b11110111;

else if(din==3'b100) dout=8'b11101111;

else if(din==3'b101) dout=8'b11011111;

else if(din==3'b110) dout=8'b10111111;

else if(din==3'b111) dout=8'b01111111;

else dout=8'bxxxxxxxx;

else dout = 8'b11111111;

end

endmodule

标签:case pre mod reg 代码 xxxxxx input code ima

原文地址:https://www.cnblogs.com/toooney/p/10667082.html