标签:导致 width 操作 sig 问题 虚拟 http 回写 str

高速缓存:为了平衡计算机的存储设备与处理器的运算速度之间几个数量级的差距,引入一层高速缓存(Cache)来作为内存与处理器之间的缓冲。

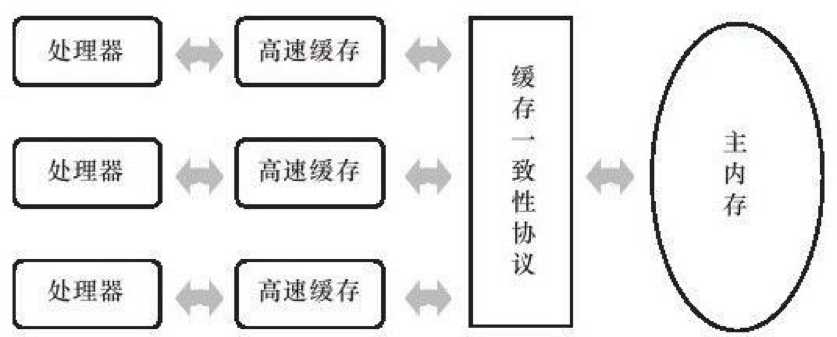

缓存一致性(Cache Coherence)的问题:每个处理器都有自己的高速缓存,而它们又共享同一主内存(Main Memory),当多个处理器的运算任务都涉及同一块主内存区域时,就可能导致各自的缓存数据不一致。解决办法就是需要各个处理器访问缓存时都遵循一些协议,在读写时要根据协议来进行操作。

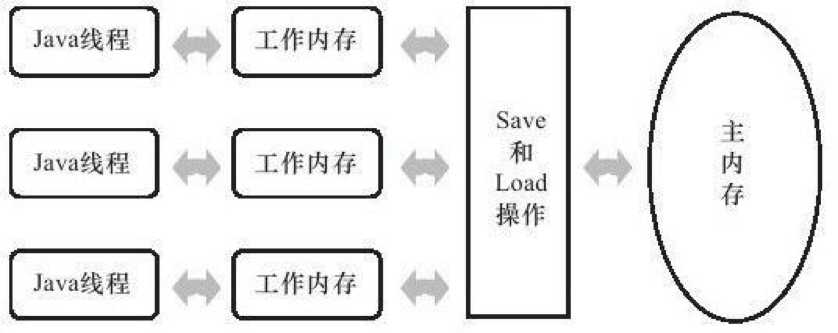

同理,为了屏蔽各种硬件和操作系统的内存访问差异,Java内存模型(Java Memory Model,JMM)如下:

lock)、解锁(unlock)、读取(read)、载入(load)、使用(use)、赋值(assign)、存储(store)、写入(write)***read操作读取变量到线程以便随后load,load操作将工作读取的变量载入内存的变量副本中;store对应read,write对应loadread和load、store和write操作之一单独出现,即不允许一个变量从主内存读取了但工作内存不接受,或者从工作内存发起回写了但主内存不接受的情况出现。assign操作,即变量在工作内存中改变了之后必须把该变化同步回主内存。assign操作就把数据从线程的工作内存同步回主内存中。load或assign)的变量,即对一个变量实施use、store操作之前必须先执行过了assign和load操作。标签:导致 width 操作 sig 问题 虚拟 http 回写 str

原文地址:https://www.cnblogs.com/qionglouyuyu/p/10874636.html