标签:intro imp param status microsoft eal wrap top sha

功能:将长度为100的整形数组的所有成员乘以2。

source:

arry_multi.h

#ifndef _ADD_AXI_H_

#define _ADD_AXI_H_

#include "ap_axi_sdata.h"

void multi_test1(ap_axis<32, 1, 1, 1> data_in[100], ap_axis<32, 1, 1, 1> data_out[100]);

#endif

arry_multi.cpp

#include "arry_multi.h"

void multi_test1(ap_axis<32, 1, 1, 1> data_in[100], ap_axis<32, 1, 1, 1> data_out[100])

{

#pragma HLS INTERFACE s_axilite port=return

#pragma HLS INTERFACE axis register both port=data_out

#pragma HLS INTERFACE axis register both port=data_in

int i;

for (i = 0; i < 100; i++)

{

data_out[i].data = data_in[i].data * 2;

data_out[i].keep = data_in[i].keep;

data_out[i].strb = data_in[i].strb;

data_out[i].user = data_in[i].user;

data_out[i].last = data_in[i].last;

data_out[i].id = data_in[i].id;

data_out[i].dest = data_in[i].dest;

}

}

testbench测试正常后,export RTL,导出IP核。

三种类型的AXI总线:

AXI4

面向高性能地址映射通信的需求;

AXI-Lite

适用于吞吐量较小的地址映射通信总线;

AXI4-Stream

面向高速数据流。

(一)里数组成员乘2的IP核所用的接口约束是stream类型的,所以这里用AXI4-Stream接口。

几种常用的AXI-Stream接口:

AXI DMA

PS memory 到 PL外设高速传输通道,AXI-HP(high performance)<-->AXI-Stream;

AXI DataMover

PS memory到PL外设高速传输通道,AXI-HP<-->AXI-Stream,只不过这次是完全由PL控制的,PS是完全被动的;

AXI Video DMA

PS memory到PL外设高速传输通道,AXI-HP<-->AXI-Stream,针对于视频、图片等二维数据。

这里选择AXIDMA。

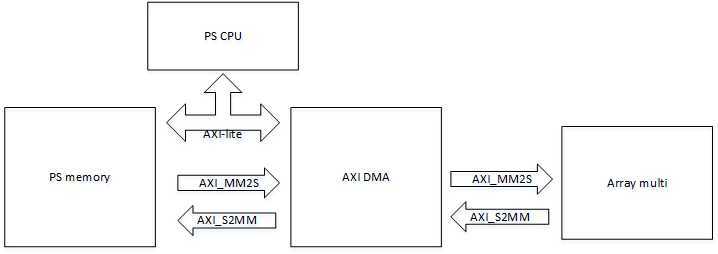

环路:

PS通过AXI-lite向DMA发送指令,AXIDMA通过HP通路和DDR交换数据,PL通过AXI-S读写DMA的数据

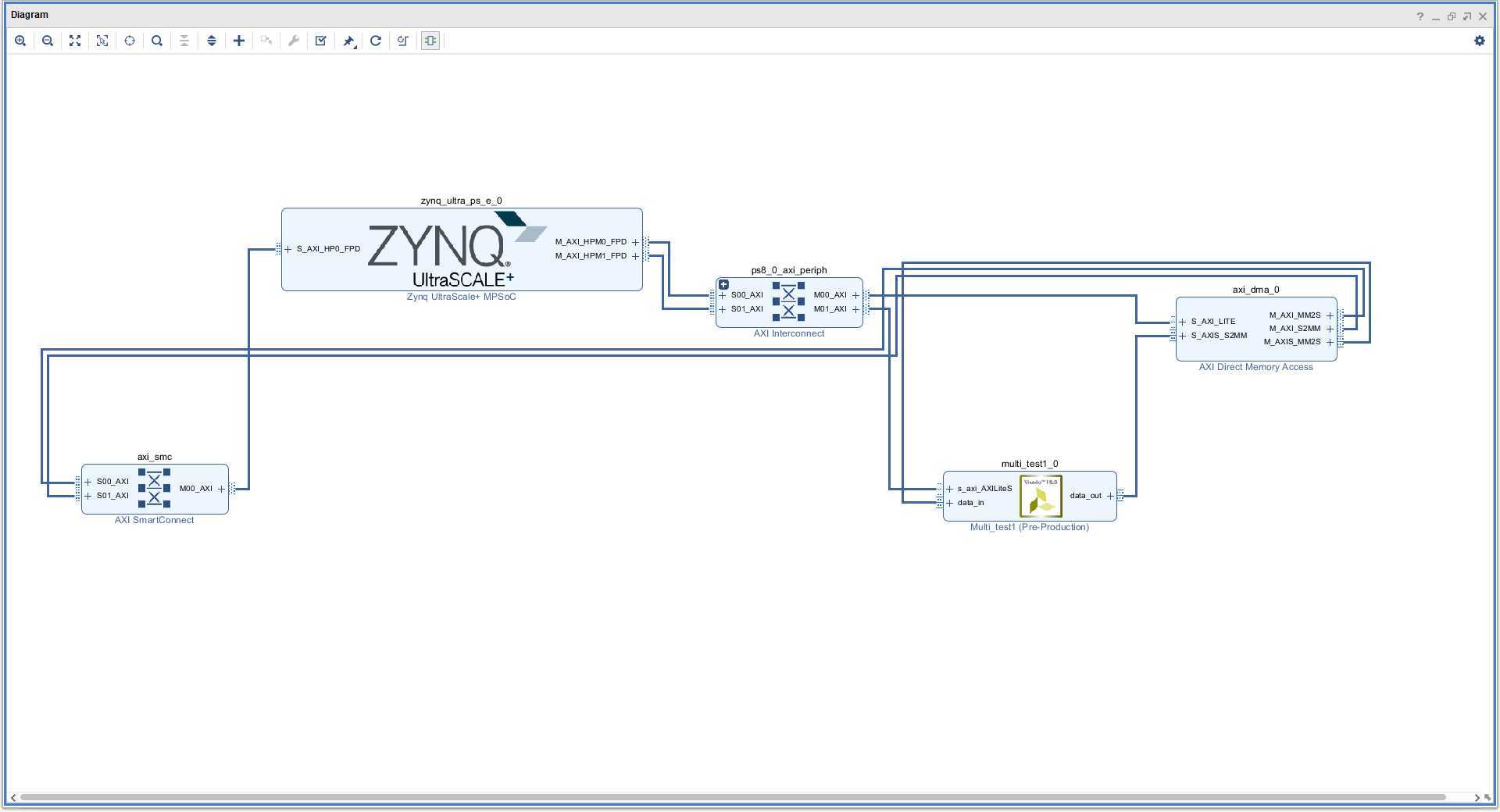

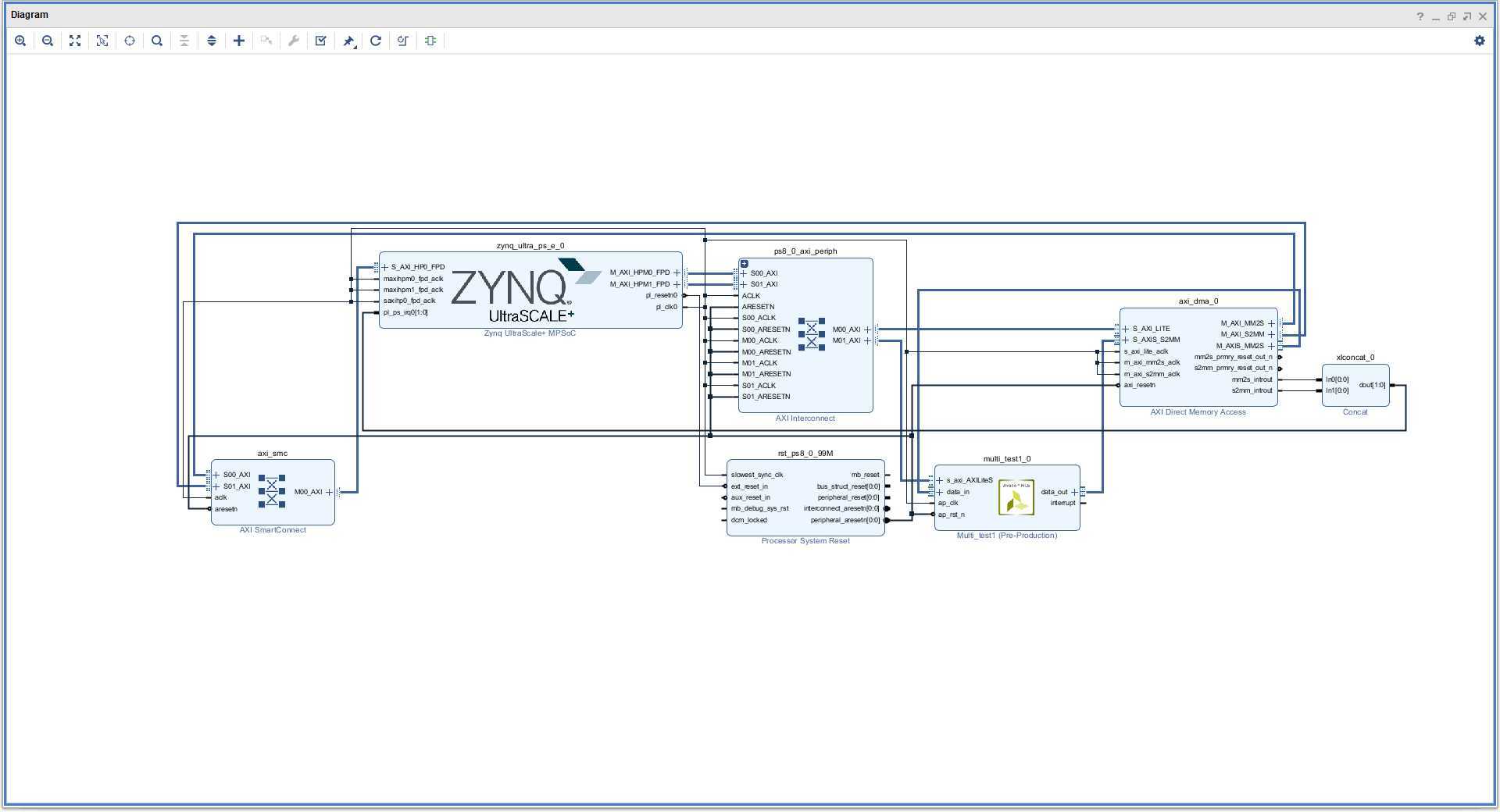

环路图:

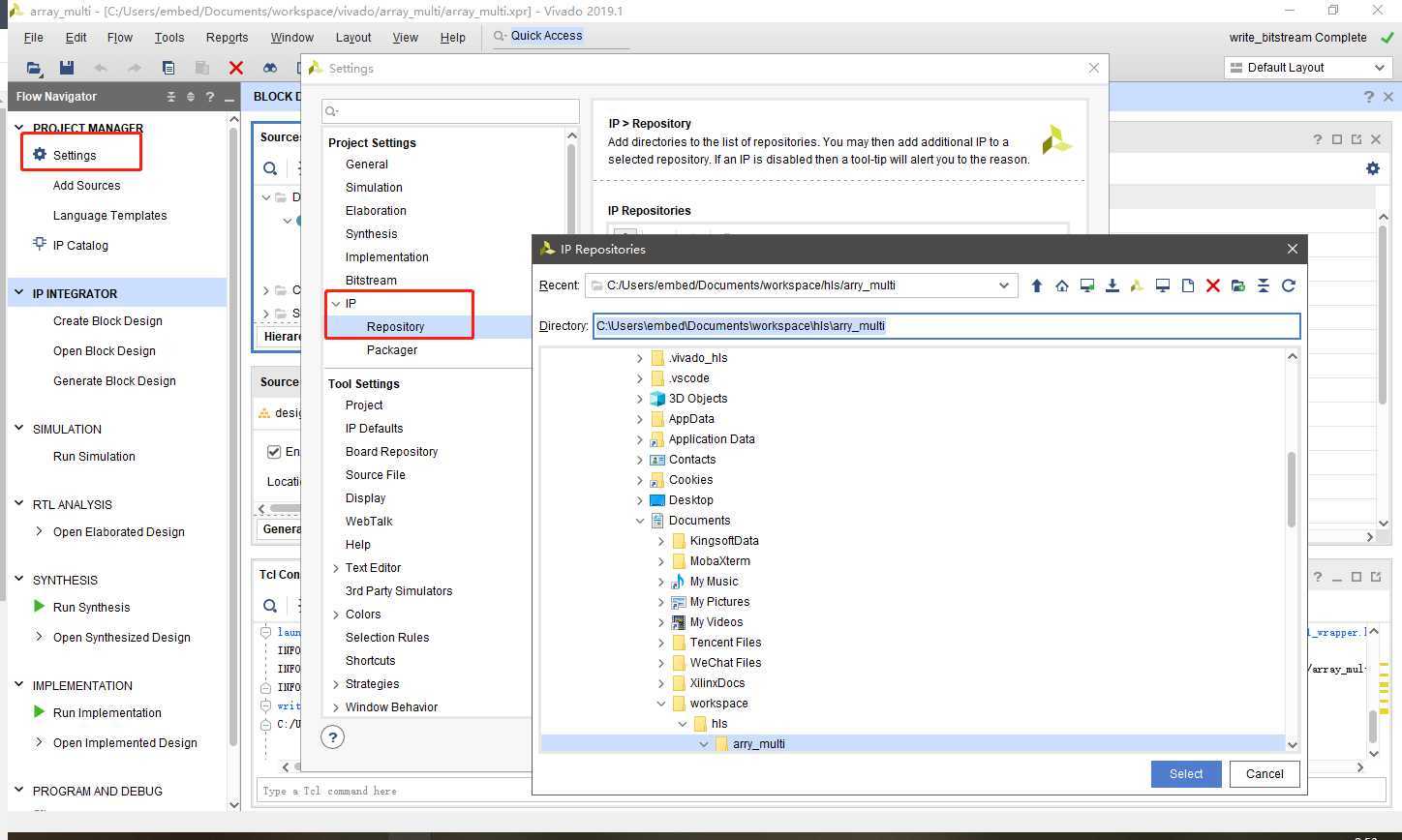

在setting->IP->repository中导入HLS生成的IP核

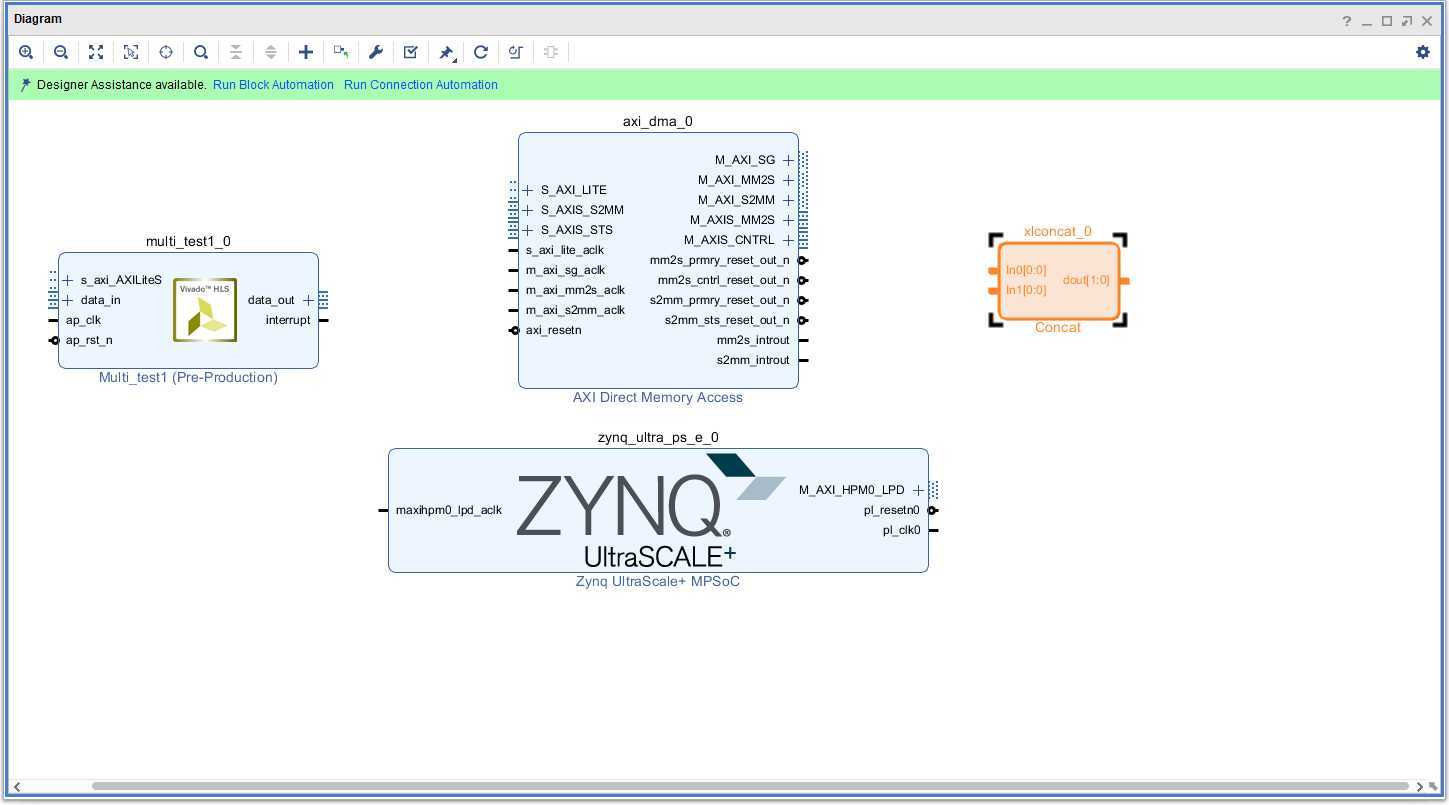

在Block Design里添加如图所示的IP核

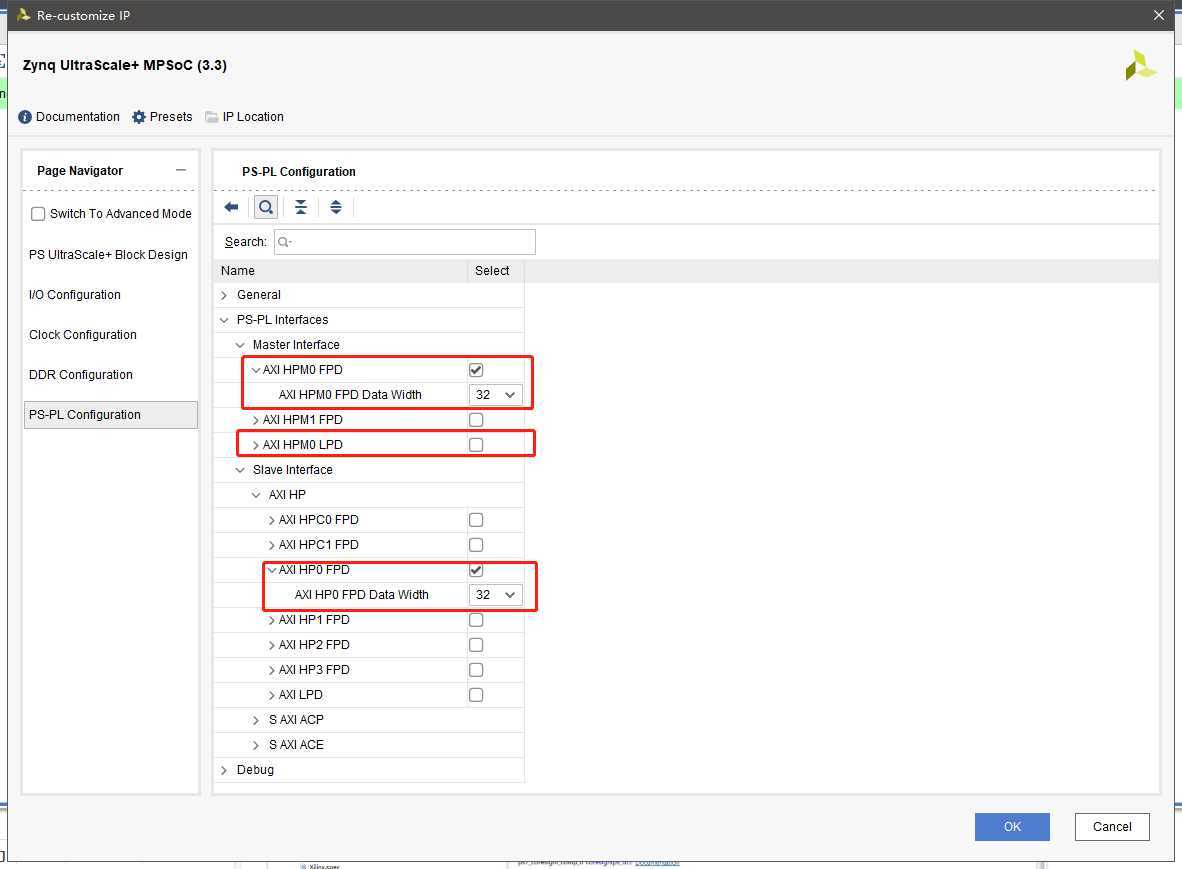

配置PS参数

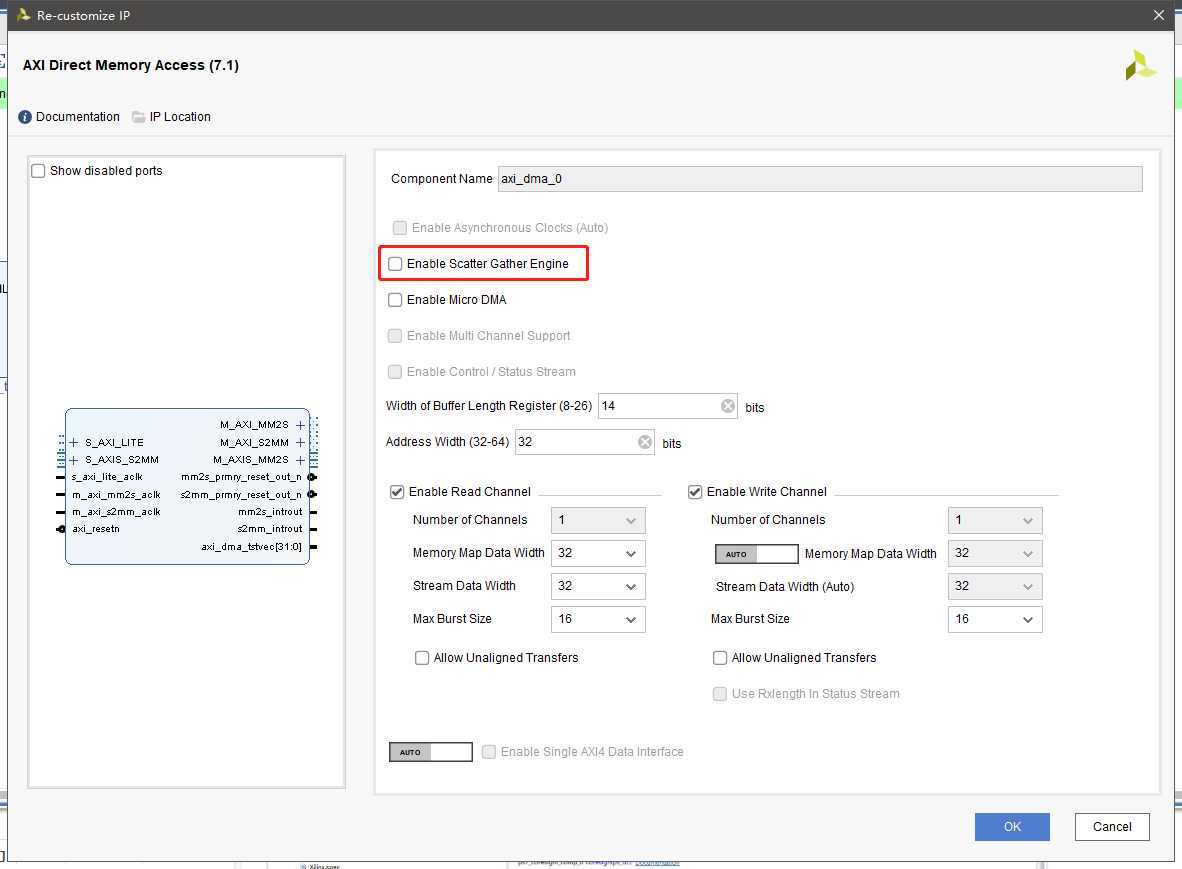

配置DMA参数

自动布局、手动连线

按照流程:generate output product、create HDL wrapper、generate bitstream、launch SDK

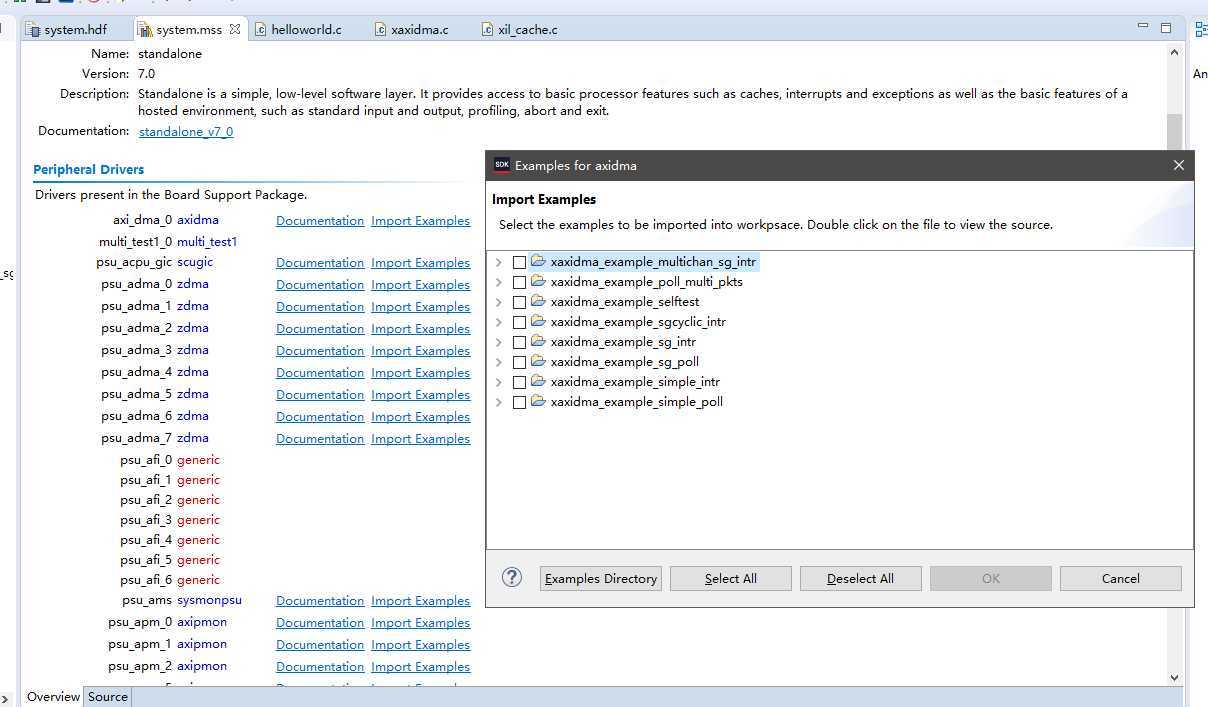

可以在system.mss里导入几个dma的demo,先看下官方的示例。

新建helloword工程,helloworld.c改写如下:

/******************************************************************************

*

* Copyright (C) 2009 - 2014 Xilinx, Inc. All rights reserved.

*

* Permission is hereby granted, free of charge, to any person obtaining a copy

* of this software and associated documentation files (the "Software"), to deal

* in the Software without restriction, including without limitation the rights

* to use, copy, modify, merge, publish, distribute, sublicense, and/or sell

* copies of the Software, and to permit persons to whom the Software is

* furnished to do so, subject to the following conditions:

*

* The above copyright notice and this permission notice shall be included in

* all copies or substantial portions of the Software.

*

* Use of the Software is limited solely to applications:

* (a) running on a Xilinx device, or

* (b) that interact with a Xilinx device through a bus or interconnect.

*

* THE SOFTWARE IS PROVIDED "AS IS", WITHOUT WARRANTY OF ANY KIND, EXPRESS OR

* IMPLIED, INCLUDING BUT NOT LIMITED TO THE WARRANTIES OF MERCHANTABILITY,

* FITNESS FOR A PARTICULAR PURPOSE AND NONINFRINGEMENT. IN NO EVENT SHALL

* XILINX BE LIABLE FOR ANY CLAIM, DAMAGES OR OTHER LIABILITY,

* WHETHER IN AN ACTION OF CONTRACT, TORT OR OTHERWISE, ARISING FROM, OUT OF

* OR IN CONNECTION WITH THE SOFTWARE OR THE USE OR OTHER DEALINGS IN THE

* SOFTWARE.

*

* Except as contained in this notice, the name of the Xilinx shall not be used

* in advertising or otherwise to promote the sale, use or other dealings in

* this Software without prior written authorization from Xilinx.

*

******************************************************************************/

/*

* helloworld.c: simple test application

*

* This application configures UART 16550 to baud rate 9600.

* PS7 UART (Zynq) is not initialized by this application, since

* bootrom/bsp configures it to baud rate 115200

*

* ------------------------------------------------

* | UART TYPE BAUD RATE |

* ------------------------------------------------

* uartns550 9600

* uartlite Configurable only in HW design

* ps7_uart 115200 (configured by bootrom/bsp)

*/

#include

#include "platform.h"

#include "xil_printf.h"

#include "xaxidma.h"

#include "xmulti_test1.h"

#include "xparameters.h"

#include "xil_exception.h"

#include "xscugic.h"

#include "xil_cache.h"

#include "xdebug.h"

XAxiDma dma;

XMulti_test1 multi;

XScuGic gic;

int tx_done;

int rx_done;

int Error;

#define RESET_TIMEOUT_COUNTER 10000

#define MAX_PKT_LEN 100

#define MEM_BASE_ADDR 0x01000000

#define TX_BUFFER_BASE (MEM_BASE_ADDR + 0x00300000)

#define RX_BUFFER_BASE (MEM_BASE_ADDR + 0x00500000)

u32 *TxBufferPtr = (u32*)TX_BUFFER_BASE;

u32 *RxBufferPtr = (u32*)RX_BUFFER_BASE;

int init_dma(void);

void init_HLS_multi(void);

int init_gic(void);

void init_exception(void);

int init_dma_intr(void);

void dma_tx_intr_handler(void *Callback);

void dma_rx_intr_handler(void *Callback);

int dma_test(void);

int main()

{

//Xil_DCacheDisable();

//Xil_ICacheDisable();

init_dma();

init_HLS_multi();

init_gic();

init_exception();

init_dma_intr();

dma_test();

return 0;

}

int init_dma(void)

{

int status;

XAxiDma_Config *dma_cfg = NULL;

dma_cfg = XAxiDma_LookupConfig(XPAR_AXIDMA_0_DEVICE_ID);

status = XAxiDma_CfgInitialize(&dma, dma_cfg);

if (status != XST_SUCCESS)

{

print("init dma failed\n\r");

return XST_FAILURE;

}

// print("init dma succeed\n\r");

return XST_SUCCESS;

}

void init_HLS_multi(void)

{

XMulti_test1_Config *multi_cfg;

XMulti_test1_Initialize(&multi, XPAR_XMULTI_TEST1_0_DEVICE_ID);

multi_cfg = XMulti_test1_LookupConfig(XPAR_XMULTI_TEST1_0_DEVICE_ID);

XMulti_test1_CfgInitialize(&multi, multi_cfg);

XMulti_test1_Start(&multi);

// print("init HLS multi succeed\n\r");

}

int init_gic(void)

{

int status;

XScuGic_Config *gic_cfg = NULL;

gic_cfg = XScuGic_LookupConfig(XPAR_SCUGIC_0_DEVICE_ID);

status = XScuGic_CfgInitialize(&gic, gic_cfg, gic_cfg->CpuBaseAddress);

if (status != XST_SUCCESS)

{

print("init gic failed\n\r");

return XST_FAILURE;

}

// print("init gic succeed\n\r");

return XST_SUCCESS;

}

void init_exception(void)

{

Xil_ExceptionInit();

Xil_ExceptionRegisterHandler(XIL_EXCEPTION_ID_INT, (Xil_ExceptionHandler)XScuGic_InterruptHandler, &gic);

Xil_ExceptionEnable();

// print("init exception succeed\n\r");

}

int init_dma_intr(void)

{

int status;

XScuGic_SetPriorityTriggerType(&gic, XPAR_FABRIC_AXI_DMA_0_MM2S_INTROUT_INTR, 0xA0, 0x3);

XScuGic_SetPriorityTriggerType(&gic, XPAR_FABRIC_AXI_DMA_0_S2MM_INTROUT_INTR, 0xA0, 0x3);

status = XScuGic_Connect(&gic, XPAR_FABRIC_AXI_DMA_0_MM2S_INTROUT_INTR, (Xil_InterruptHandler)dma_tx_intr_handler, &dma);

if (status != XST_SUCCESS)

{

return status;

}

status = XScuGic_Connect(&gic, XPAR_FABRIC_AXI_DMA_0_S2MM_INTROUT_INTR, (Xil_InterruptHandler)dma_rx_intr_handler, &dma);

if (status != XST_SUCCESS)

{

return status;

}

XScuGic_Enable(&gic, XPAR_FABRIC_AXI_DMA_0_MM2S_INTROUT_INTR);

XScuGic_Enable(&gic, XPAR_FABRIC_AXI_DMA_0_S2MM_INTROUT_INTR);

XAxiDma_IntrEnable(&dma, XAXIDMA_IRQ_ALL_MASK, XAXIDMA_DMA_TO_DEVICE);

XAxiDma_IntrEnable(&dma, XAXIDMA_IRQ_ALL_MASK, XAXIDMA_DEVICE_TO_DMA);

// print("init dma intr succeed\n\r");

return XST_SUCCESS;

}

void dma_rx_intr_handler(void *Callback)

{

u32 IrqStatus;

int TimeOut;

UINTPTR RxPacket;

RxPacket = (u32*)RxBufferPtr;

Xil_DCacheInvalidateRange((UINTPTR)RxPacket, 100);

XAxiDma *AxiDmaInst = (XAxiDma *)Callback;

/* Read pending interrupts */

IrqStatus = XAxiDma_IntrGetIrq(AxiDmaInst, XAXIDMA_DEVICE_TO_DMA);

/* Acknowledge pending interrupts */

XAxiDma_IntrAckIrq(AxiDmaInst, IrqStatus, XAXIDMA_DEVICE_TO_DMA);

/*

* If no interrupt is asserted, we do not do anything

*/

if (!(IrqStatus & XAXIDMA_IRQ_ALL_MASK))

{

return;

}

/*

* If error interrupt is asserted, raise error flag, reset the

* hardware to recover from the error, and return with no further

* processing.

*/

if ((IrqStatus & XAXIDMA_IRQ_ERROR_MASK))

{

Error = 1;

/* Reset could fail and hang

* NEED a way to handle this or do not call it??

*/

XAxiDma_Reset(AxiDmaInst);

TimeOut = RESET_TIMEOUT_COUNTER;

while (TimeOut)

{

if (XAxiDma_ResetIsDone(AxiDmaInst))

{

break;

}

TimeOut -= 1;

}

return;

}

/*

* If completion interrupt is asserted, then set RxDone flag

*/

if ((IrqStatus & XAXIDMA_IRQ_IOC_MASK))

{

rx_done = 1;

}

}

void dma_tx_intr_handler(void *Callback)

{

u32 IrqStatus;

int TimeOut;

XAxiDma *AxiDmaInst = (XAxiDma *)Callback;

/* Read pending interrupts */

IrqStatus = XAxiDma_IntrGetIrq(AxiDmaInst, XAXIDMA_DMA_TO_DEVICE);

/* Acknowledge pending interrupts */

XAxiDma_IntrAckIrq(AxiDmaInst, IrqStatus, XAXIDMA_DMA_TO_DEVICE);

/*

* If no interrupt is asserted, we do not do anything

*/

if (!(IrqStatus & XAXIDMA_IRQ_ALL_MASK))

{

return;

}

/*

* If error interrupt is asserted, raise error flag, reset the

* hardware to recover from the error, and return with no further

* processing.

*/

if ((IrqStatus & XAXIDMA_IRQ_ERROR_MASK))

{

Error = 1;

/*

* Reset should never fail for transmit channel

*/

XAxiDma_Reset(AxiDmaInst);

TimeOut = RESET_TIMEOUT_COUNTER;

while (TimeOut)

{

if (XAxiDma_ResetIsDone(AxiDmaInst))

{

break;

}

TimeOut -= 1;

}

return;

}

/*

* If Completion interrupt is asserted, then set the TxDone flag

*/

if ((IrqStatus & XAXIDMA_IRQ_IOC_MASK))

{

tx_done = 1;

}

}

int dma_test(void)

{

int status;

tx_done = 0;

rx_done = 0;

Error = 0;

u32 value = 0x00000000;

int index;

for (index = 0; index < MAX_PKT_LEN; index++)

{

TxBufferPtr[index] = value;

value = (value + 1) & 0xFFFFFFFF;

}

printf("data_in:\n\r");

int y;

for (y = 0; y < 100; y++)

{

printf("%03d ", TxBufferPtr[y]);

if (y % 10 == 9)

{

printf("\n\r");

}

}

Xil_DCacheFlushRange((INTPTR)TxBufferPtr, MAX_PKT_LEN * sizeof(u32));

status = XAxiDma_SimpleTransfer(&dma, (UINTPTR)TxBufferPtr, MAX_PKT_LEN * sizeof(u32), XAXIDMA_DMA_TO_DEVICE);

if (status != XST_SUCCESS)

{

printf("XAxiDma_SimpleTransfer dma to device failed.\n\r");

return XST_FAILURE;

}

status = XAxiDma_SimpleTransfer(&dma, (UINTPTR)RxBufferPtr, MAX_PKT_LEN * sizeof(u32), XAXIDMA_DEVICE_TO_DMA);

if (status != XST_SUCCESS)

{

printf("XAxiDma_SimpleTransfer device to dma failed.\n\r");

return XST_FAILURE;

}

while (!tx_done || !rx_done)

{

}

tx_done = 0;

rx_done = 0;

printf("data_out:\n\r");

for (y = 0; y < 100; y++)

{

printf("%03d ", RxBufferPtr[y]);

if (y % 10 == 9)

{

printf("\n\r");

}

}

if (Error)

{

printf("failed.\n\r");

}

if (status != XST_SUCCESS)

{

return XST_FAILURE;

}

return XST_SUCCESS;

}

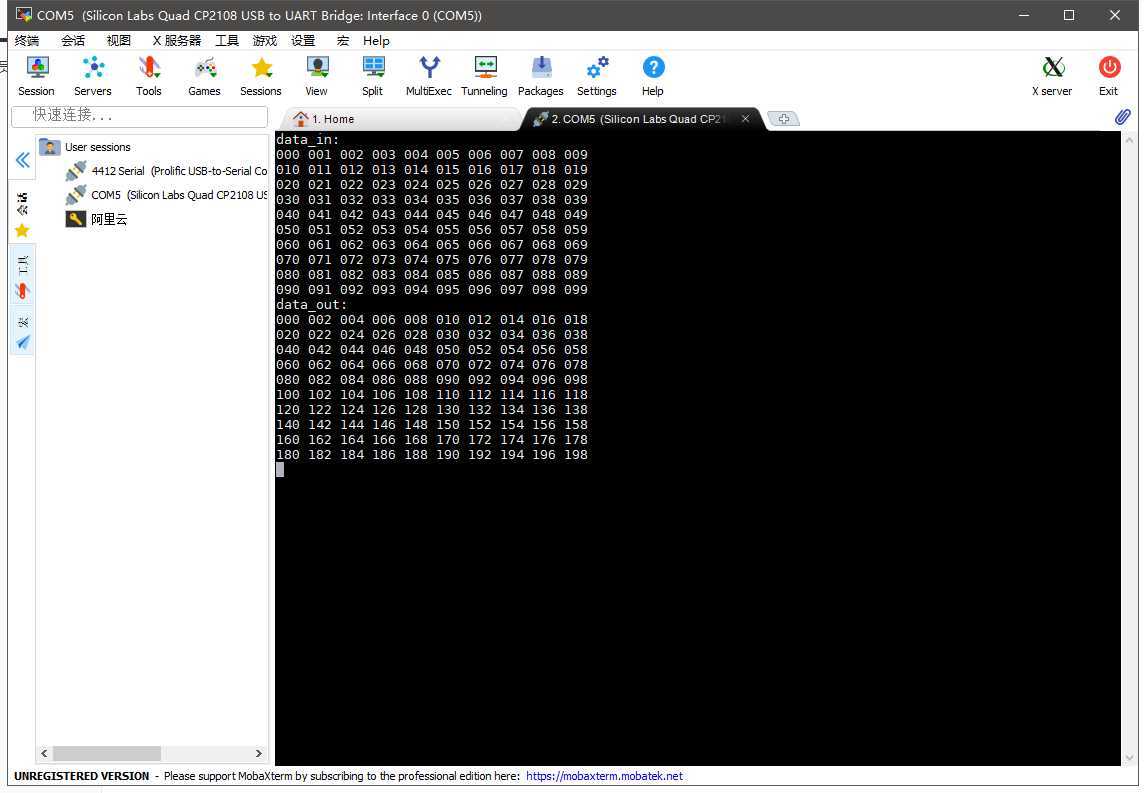

运行结果:

标签:intro imp param status microsoft eal wrap top sha

原文地址:https://www.cnblogs.com/guangnianxd/p/11521166.html