标签:img nice comm compute developer ice net lazy shadow

搬运自我的CSDN https://blog.csdn.net/u013213111/article/details/107031986

最近在多核ARM芯片上搞并行计算,涉及到核间数据交互,因此对多核cache coherence稍作探究。想解决的疑问是:各个核之间是否“知道”内存中的数据被其他核进行了改动?有何机制来保障cache coherence?

CSAPP中似乎没有具体谈到多核之间cache是如何配合的(我看的是2ed,不知道3rd中是否有增加),但是在CMU Introduction to Computer Systems (ICS)课程中,最后一课正好讲的是Multi-core architectures,Slide十分NICE!

Slide中提到了两种基础的solutions for cache coherence:

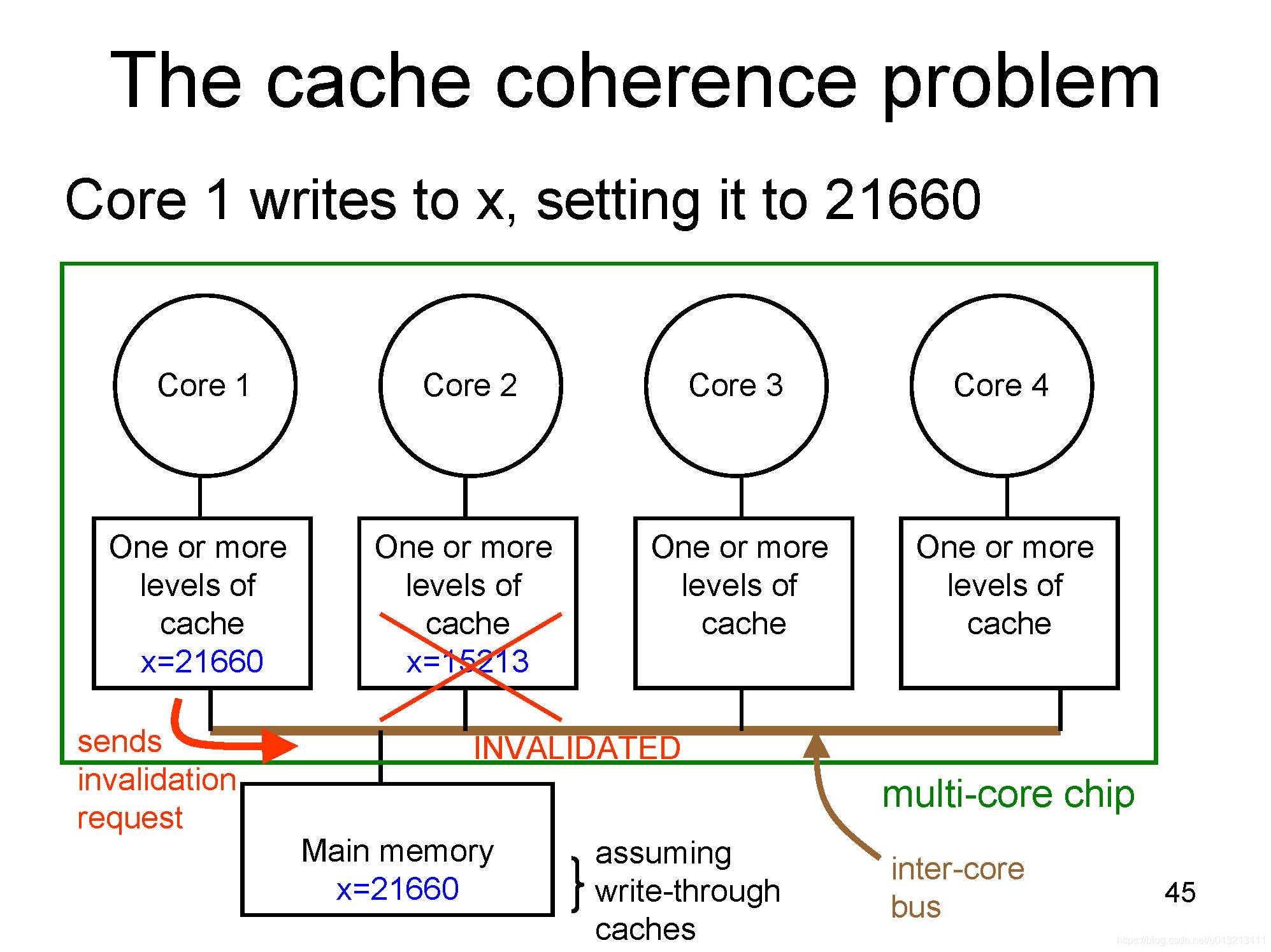

1.Invalidation protocol with snooping

每个core都在监听inter-core bus的消息,假如其他的某个core更改了内存的数据,就及时地无效掉本地core相应的cache。

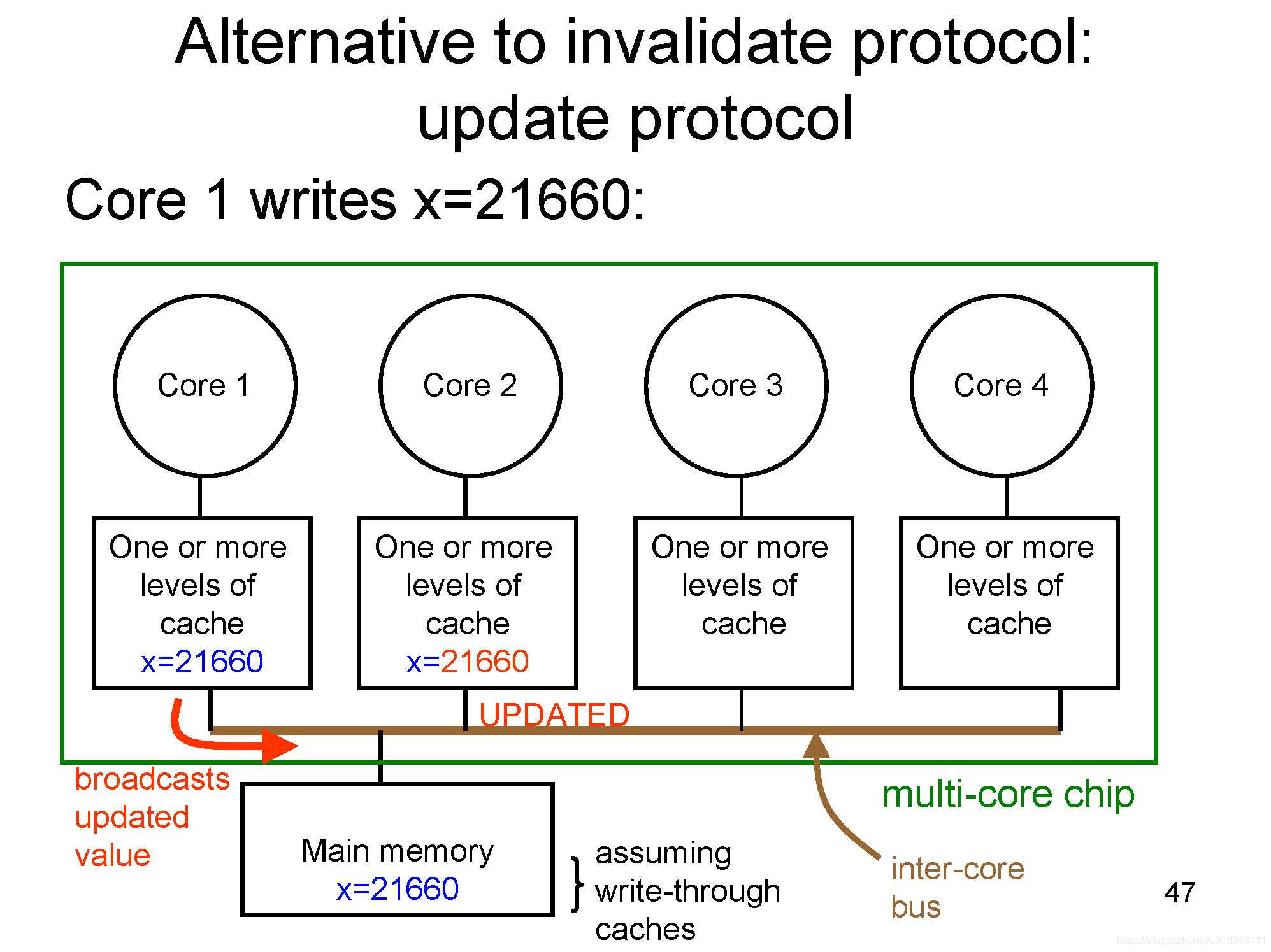

2.update protocol

2.update protocol

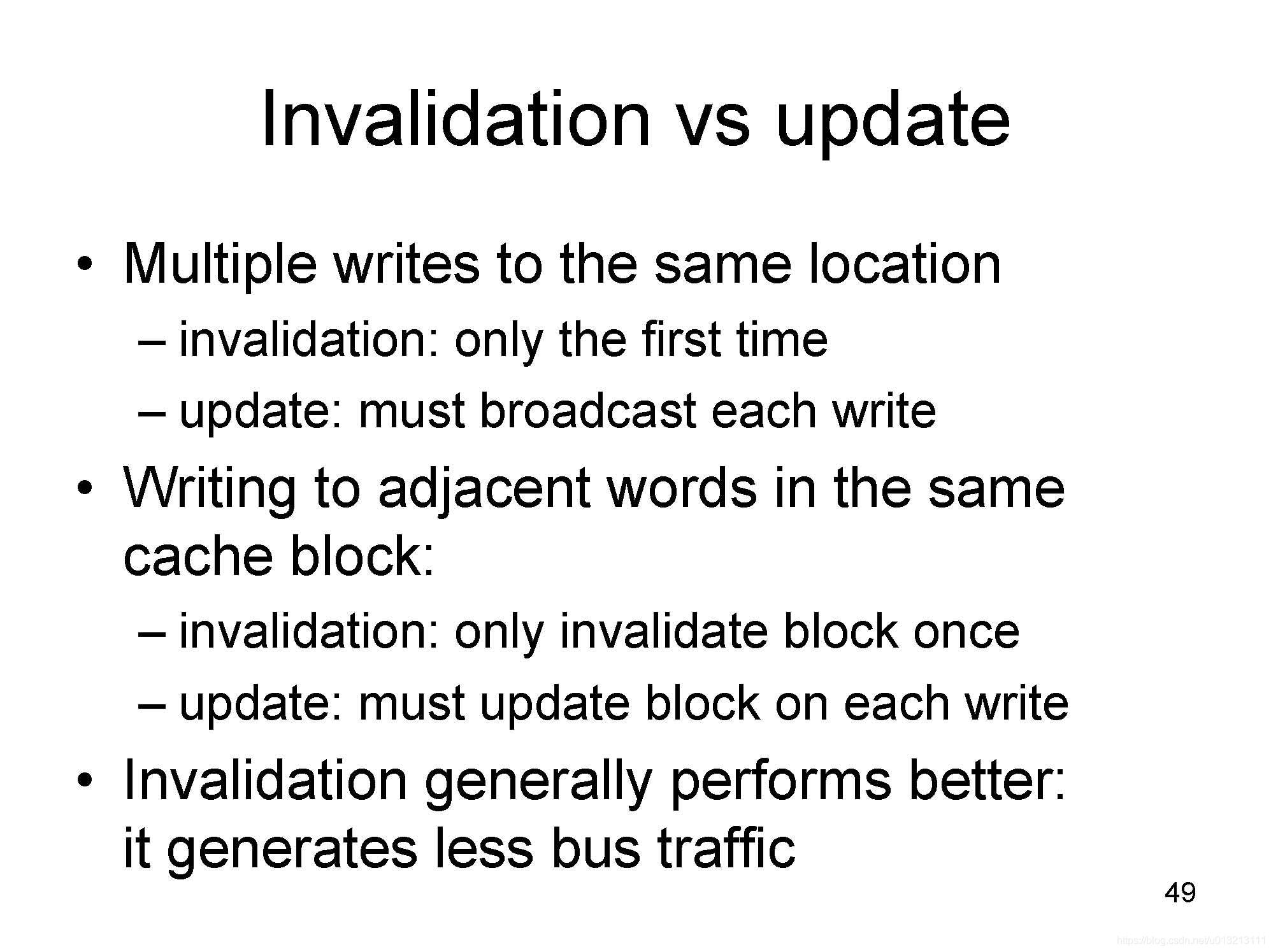

二者对比,通常来说Invalidation protocol会表现得更好,比如当对某一块内存进行多次更改时,只需要在第一次时进行无效操作。

二者对比,通常来说Invalidation protocol会表现得更好,比如当对某一块内存进行多次更改时,只需要在第一次时进行无效操作。

更深入的讲解,见Computer Architecture: A Quantitative Approach之5.2节。分享一份觉得不错的Slide,From https://www.csd.uoc.gr/~hy425/2016f/lectures/Lec15_snoop_coherence.pdf,用其中的两张图说明一下MESI协议。

更深入的讲解,见Computer Architecture: A Quantitative Approach之5.2节。分享一份觉得不错的Slide,From https://www.csd.uoc.gr/~hy425/2016f/lectures/Lec15_snoop_coherence.pdf,用其中的两张图说明一下MESI协议。

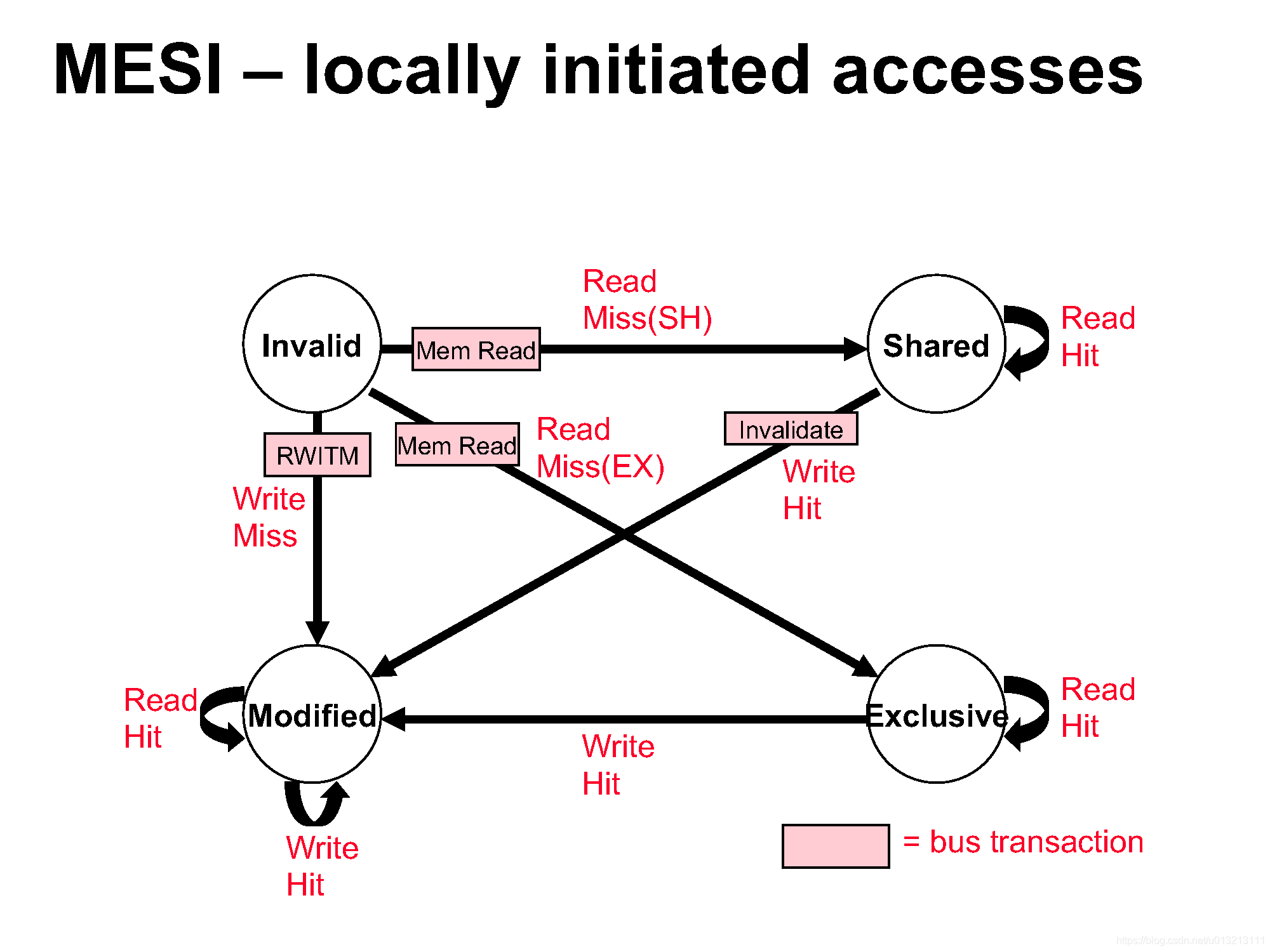

对于本地的cache:

以Invalid状态下的Read Miss为例,假如其他的cache中存在状态为Exclusive或者为Share的,那么本地的cache会转换为Share状态;否则转换为Exclusive状态。

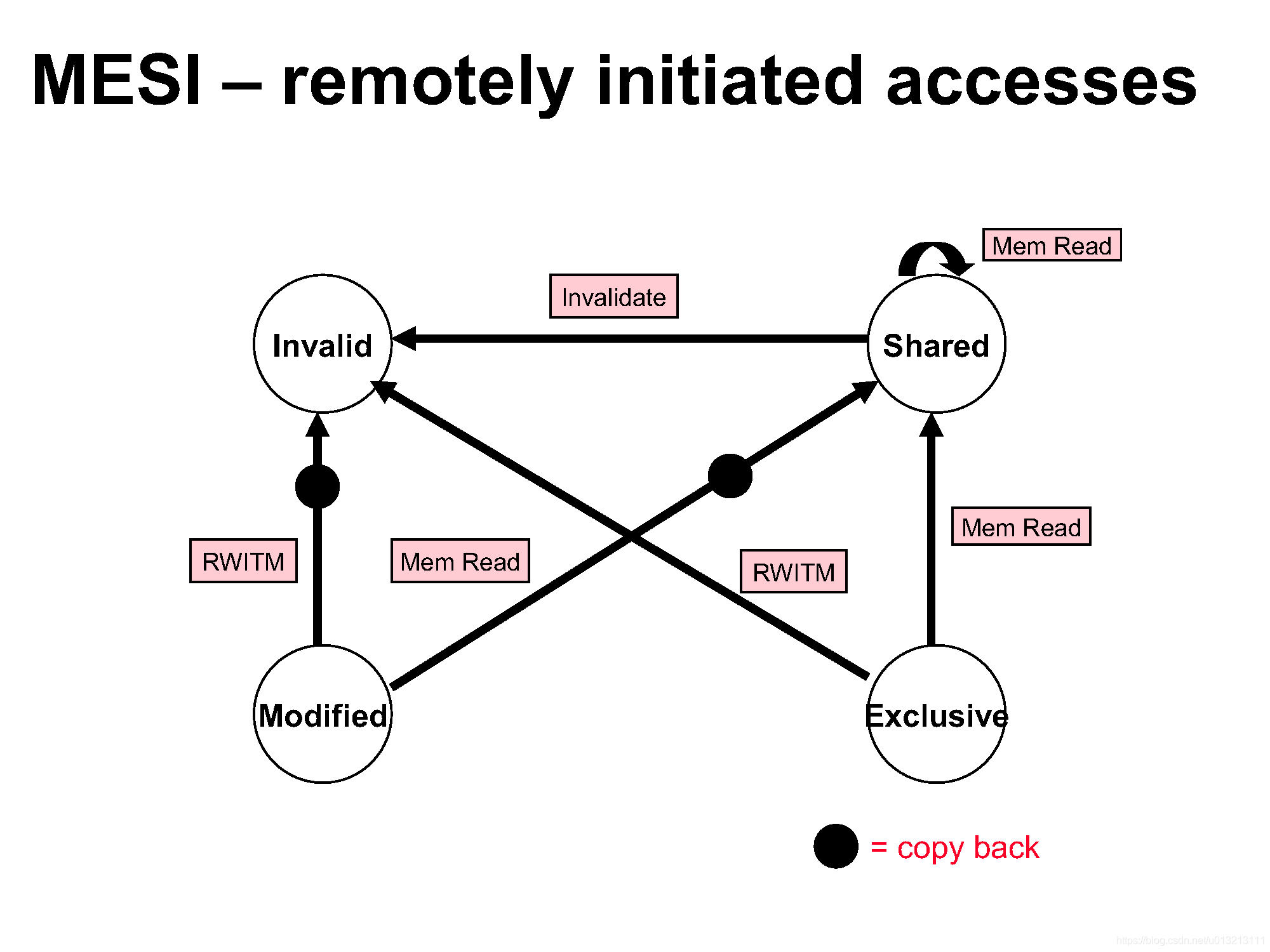

对于非本地的cache:

对于非本地的cache:

例如在Modified状态下,发现bus transaction为Memory Read,那么说明其他core在读取,此时当然是先把最新的cache中的数据copy back,之后相当于不止一块cache中存有这个内存数据,所以状态会转换为Share。

具体到ARM芯片,

具体到ARM芯片,

DAI0425_migrating_an_application_from_ARMv5_to_ARMv7_AR这份文档的3.12中提到,大多数ARM芯片使用的是Modified Owner Exclusive Shared Invalid (MOESI) protocol,而Cortex-A9则使用Modified Exclusive Shared Invalid (MESI) protocol。此外还可参考具体IP核的Technial Reference Manual。

最后的感想:关于计算机体系结构,没有什么是CSAPP不能解决的,如果有,那就再加上一本Computer Architecture: A Quantitative Approach。

标签:img nice comm compute developer ice net lazy shadow

原文地址:https://www.cnblogs.com/lyrich/p/13339352.html