| 作者: 德州仪器技术应用工程师 冯华亮/ Brighton Feng/ bf@ti.com

摘要

串行RapidIO针对高性能嵌入式系统芯片间和板间互连而设计,它将是未来十几年中嵌入式系统互连的最佳选择。

本文比较RapidIO和传统互连技术的优点;介绍RapidIO协议架构,包格式,互连拓扑结构以及串行RapidIO物理层规范。介绍串行RapidIO在无线基础设施方面的应用。

RapidIO 与传统嵌入互连方式的比较

随着高性能嵌入式系统的不断发展,芯片间及板间互连对带宽、成本、灵活性及可靠性的要求越来越高,传统的互连方式,如处理器总线、PCI总线和以太网,都难以满足新的需求 。

处理器总线主要用作外部存储器接口,如德州仪器(TI) C6000系列DSP的外部存储器接口,可支持外接同步SDRAM、SBSRAM及FIFO,也可支持异步SRAM、FLASH等。外部存储器接口也可用作与板内FPGA或ASIC芯片互连,这种情况下,FPGA或ASIC模拟一个DSP支持的存储器接口,DSP则把FPGA或ASIC当作存储器来访问。这类同步接口带宽可达10Gbps,如德州仪器TMS320C6455 DSP的DDR2接口最大带宽为17.066Gbps,SBSRAM接口最大带宽为8.533Gbps。然而,这种接口也存在一些局限性:

- 接口管脚多,硬件设计困难。常见的DDR2接口有70~80个管脚;

- 只能用于板内互连,无法用于板间互连;

- 不是点对点的对等互连,DSP始终是主设备,其它器件只能做从设备。

PCI是广泛用于计算机内器件互连的技术。传统PCI技术也采样类似于上述存储器接口的并行总线方式,如TMS320C6455 DSP的PCI接口,有32bits数据总线,最高时钟速度为66MHz,共有42个管脚。最新的串行PCI Express技术采用与串行RapidIO(SRIO, Serial RapidIO)类似的物理层传输技术,使得带宽达到10Gbps左右。但由于其主要的应用仍是计算机,而且为了兼容传统PCI技术,使得它在嵌入式设备方面的应用具有一定的局限性,如不支持点对点对等通信等。

众所周知,以太网是使用最广泛的局域网互连技术,它也被扩展应用到嵌入式设备互连,但它的局限性也是显而易见的:

- 不支持硬件纠错,软件协议栈开销较大;

- 打包效率低,有效传输带宽因此而减小;

- 只支持消息传输模式,不支持对对端设备的直接存储器访问(DMA, Direct Memory Access)。

针对嵌入式系统的需求以及传统互连方式的局限性,RapidIO标准按如下目标被制定:

- 针对嵌入式系统机框内高速互连应用而设计。

- 简化协议及流控机制,限制软件复杂度,使得纠错重传机制乃至整个协议栈易于用硬件实现。

- 提高打包效率,减小传输时延。

- 减少管脚,降低成本。

- 简化交换芯片的实现,避免交换芯片中的包类型解析。

- 分层协议结构,支持多种传输模式,支持多种物理层技术,灵活且易于扩展。

图1展示了RapidIO互连在嵌入式系统中的应用。

图1 RapidIO在嵌入式系统中的应用

表1总结比较了的三种带宽能达到10Gbps的互连技术:以太网,PCI Express和串行RapidIO,从中可以看出串行RapidIO是最适合高性能嵌入式系统互连的技术。

表1 10G级互连技术比较

| |

软件实现TCP/IP 协议栈的以太网 |

4x PCI Express |

4x SRIO |

备注 |

| 软件开销 |

高 |

中 |

低 |

SRIO 协议栈简单,一般都由硬件实现,软件开销很小 |

| 硬件纠错重传 |

不支持 |

支持 |

支持 |

|

| 传输模式 |

消息 |

DMA |

DMA,消息 |

|

| 拓扑结构 |

任意 |

PCI树 |

任意 |

SRIO支持直接点对点或通过交换器件实现的各种拓扑结构 |

| 直接点对点对等互连 |

支持 |

不支持 |

支持 |

SRIO互连双方可对等的发起传输。 |

| 传输距离 |

长 |

中 |

中 |

SRIO针对嵌入式设备内部互连,传输距离一般小于1米 |

| 数据包最大有效载荷长度 |

1500字节 |

4096字节 |

256字节 |

嵌入式通信系统对实时性要求高,SRIO小包传输可减少传输时延 |

| 打包效率 (以传输256字节数据为例) |

79% (TCP包) |

82% |

92~94% |

打包效率是有效载荷长度与总包长的比率。SRIO支持多种高效包格式。 |

串行RapidIO协议

RapidIO行业协会成立于2000年,其宗旨是为嵌入式系统开发可靠的,高性能,基于包交换的互连技术。RapidIO协议的简要发展历史是:

- 2001年初,最初的标准被发布

- 2002年6月,1.2版标准发布

- 2005年6月,1.3版标注发布

串行RapidIO是物理层采用串行差分模拟信号传输的RapidIO标准。SRIO 1.x 标准支持的信号速度为1.25GHz、2.5GHz、3.125GHz;正在制定的RapidIO 2.0标准将支持5GHz、6.25GHz.

目前,几乎所有的嵌入式系统芯片及设备供应商都加入了RapidIO行业协会。德州仪器(TI) 2001年加入该组织,2003年成为领导委员会成员。2005年底,德州仪器(TI)推出第一个集成SRIO(Serial RapidIO)的DSP,后来又陆续推出共5款支持SRIO的DSP,这使得RapidIO的应用全面启动。

RapidIO协议结构及包格式

为了满足灵活性和可扩展性的要求,RapidIO协议分为三层:逻辑层、传输层和物理层。图2说明了RapidIO协议的分层结构。

图2 RapidIO协议分层结构

逻辑层定义了操作协议; 传输层定义了包交换、路由和寻址机制;物理层定义了电气特性、链路控制和纠错重传等。

象以太网一样,RapidIO也是基于包交换的互连技术。如图3所示,RapidIO包由包头、可选的载荷数据和16bits CRC校验组成。包头的长度因为包类型不同可能是十几到二十几个字节。每包的载荷数据长度不超过256字节,这有利于减少传输时延,简化硬件实现。

图3 RapidIO包格式

上述包格式定义兼顾了包效率及组包/解包的简单性。RapidIO交换器件仅需解析前后16bits,以及源/目地器件ID,这简化了交换器件的实现。

逻辑层协议

逻辑层定义了操作协议和相应的包格式。RapidIO支持的逻辑层业务主要是:直接IO/DMA (Direct IO/Direct Memory Access)和消息传递(Message Passing)。

直接IO/DMA模式是最简单实用的传输方式,其前提是主设备知道被访问端的存储器映射。在这种模式下,主设备可以直接读写从设备的存储器。直接IO/DMA在被访问端的功能往往完全由硬件实现,所以被访问的器件不会有任何软件负担。从功能上讲,这一特点和德州仪器DSP的传统的主机接口(HPI, Host Port Interface)类似。但和HPI口相比,SRIO(Serial RapidIO)带宽大,管脚少,传输方式更灵活。

对上层应用来说,发起直接IO/DMA传输主要需提供以下参数:目地器件ID、数据长度、数据在目地器件存储器中的地址。

直接IO/DMA模式又可进一步分为以下几种传输格式:

- NWRITE: 写操作,不要求接收端响应。

- NWRITE_R: 带响应的NWRITE(NWRITE with Response),要求接收端响应。

- SWRITE:流写(Stream Write),数据长度必须是8字节的整数倍,不要求接收端响应。

- NREAD: 读操作。

SWRITE是最高效的传输格式;带响应的写操作或读操作效率则较低,一般只能达到不带响应的传输的效率的一半。

消息传递(Message Passing)模式则类似于以太网的传输方式,它不要求主设备知道被访问设备的存储器状况。数据在被访问设备中的位置则由邮箱号(类似于以太网协议中的端口号)确定。从设备根据接收到的包的邮箱号把数据保存到对应的缓冲区,这一过程往往无法完全由硬件实现,而需要软件协助,所以会带来一些软件负担。

对上层应用来说,发起消息传递主要需提供以下参数:目地器件ID、数据长度、邮箱号。

表2比较了直接IO/DMA和消息传递模式。

表2 直接IO/DMA和消息传递的对比

| |

直接IO/DMA |

消息传递 |

| 主机可直接访问从机存储器? |

可以 |

不可以 |

| 主机需要知道从机存储器映射? |

需要 |

不需要 |

| 数据寻址方式 |

存储器地址 |

邮箱号 |

| 支持的数据访问方式 |

读/写 |

写 |

| 从机软件负担 |

无 |

有 |

传输层协议

RapidIO是基于包交换的互连技术,传输层定义了包交换的路由和寻址机制。

RapidIO网络主要由两种器件,终端器件(End Point)和交换器件(Switch)组成。终端器件是数据包的源或目的地,不同的终端器件以器件ID来区分。RapidIO支持8 bits 或 16 bits器件ID,因此一个RapidIO网络最多可容纳256或65536个终端器件。与以太网类似,RapidIO也支持广播或组播,每个终端器件除了独有的器件ID外,还可配置广播或组播ID。交换器件根据包的目地器件ID进行包的转发,交换器件本身没有器件ID。

RapidIO的互连拓扑结构非常灵活,除了通过交换器件外,两个终端器件也可直接互连。以德州仪器(TI)的TMS320C6455 DSP为例,它有4个3.125G的SRIO口,它可支持的拓扑结构如图4所示。

图4 RapidIO支持灵活多样的拓扑结构

物理层协议

RapidIO 1.x 协议定义了以下两种物理层接口标准:

- 8/16 并行LVDS协议

- 1x/4x 串行协议 (SRIO)

并行RapidIO由于信号线较多(40~76)难以得到广泛的应用,而1x/4x串行RapidIO仅4或16个信号线,逐渐成为主流,所以本文仅介绍串行RapidIO。

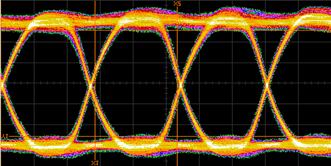

串行RapidIO基于现在已广泛用于背板互连的SerDes(Serialize Deserialize)技术,它采用差分交流耦合信号。差分交流耦合信号具有抗干扰强、速率高、传输距离较远等优点。差分交流耦合信号的质量不是由传统的时序参数来衡量,而是通过眼图来衡量,眼图中的“眼睛”张得越开则信号质量越好。图5是一个典型的串行RapidIO信号的眼图。

图5 串行RapidIO信号眼图

差分信号的强弱由一对信号线的电压差值表示,串行RapidIO协议规定信号峰-峰值的范围是200mV-2000mV。信号幅度越大,则传输距离越远,RapidIO协议按信号传输距离定义两种传输指标:

- 短距离传输(Short Run),<=50厘米,主要用于板内互连,推荐的发送端信号峰-峰值为500mV-1000mV

- 长距离传输(Long Run),>50厘米,主要用于板间或背板互连,推荐的发送端信号峰-峰值为800mV-1600mV

为了支持全双工传输,串行RapidIO收发信号是独立的,所以每一个串行RapidIO口由4根信号线组成。标准的1x/4x 串行RapidIO接口,支持四个口,共16根信号线。这四个口可被用作独立的接口传输不同的数据;也可合并在一起当作一个接口使用,以提高单一接口的吞吐量。

德州仪器TMS320C6455 DSP上集成了标准的1x/4x串行RapidIO接口,如图6所示。

图6德州仪器TMS320C6455 DSP 1x/4x 串行RapidIO接口框图

发送时,逻辑层和传输层将组好的包经过CRC编码后被送到物理层的FIFO中,“8b/10b编码”模块将每8bit数据编码成10bits数据,“并/串转换”模块将10bits并行数据转换成串行bits,发送模块把数字bit转换成差分交流耦合信号在信号线上发送出去。这里的8b/10编码的主要作用是:

- 保证信号有足够的跳变,以便于接收方恢复时钟。串行RapidIO没有专门的时钟信号线,接收端靠数据信号的跳变恢复时钟。所以需要把信号跳变少的8bits数据(如全0或全1)编码成有一定跳变的10bits数据。另外,也使得总体数据中0和1的个数均衡,以消除直流分量,保证交流耦合特性;

- 8b/10编码可扩大符号空间,以承载带内控制符号。10bits能表示1024个符号,其中256个表示有效的8bits数据,剩下的符号中的几十个被用作控制符号。控制符号可被用作包分隔符,响应标志,或用于链路初始化,链路控制等功能;

- 8b/10编码能实现一定的检错功能。1024个符号中,除了256个有效数据符号和几十个控制符号外,其它符号都是非法的,接收方收到非法符号则表示链路传输出错。

接收的过程则正好相反,首先接收方需要根据数据信号的跳变恢复出时钟,用这个时钟采样串行信号,将串行信号转换为10bits的并行信号,再按8b/10b编码规则解码得到8bits数据,最后做CRC校验并送上层处理。

数据被正确的接收时,接收端会发送一个ACK响应包给发送端;如果数据不正确(CRC错或非法的10bits符号),则会送NACK包,要求发送方重传。这种重传纠错的功能由物理层完成,而物理层功能往往由硬件实现,所以不需要软件干预。

串行RapidIO支持的信号速率有三种:1.25GHz,2.5GHz,3.125GHz。但由于8b/10b编码,其有效数据速率分别为:1Gbps, 2Gbps, 2.5Gbps。 4个1x端口或一个4x端口支持的最高速率为10Gbps。

串行RapidIO在无线基础设施上的应用

无线基础设施如基站、媒体网关等,是典型的高性能嵌入式通信系统,它们对互连的带宽、时延、复杂度、灵活性、可靠性都有非常高的要求。而串行RapidIO正是满足这些要求的最佳选择。

以无线基站为例,在SRIO出现之前,无线基站的基带处理的典型框图如图7所示。

图7 传统无线基站基带处理框图

在传统的基站中,DSP与ASIC或FPGA之间的互连一般用外部存储器接口EMIF(External Memory Interface);DSP之间或DSP与主机之间一般用HPI(Host Port Interface)或PCI互连。它们的主要缺点是:带宽小;信号线多;主从模式接口,不支持对等传输。另外,DSP不能直接进行背板传输。

使用SRIO(Serial RapidIO)则可有效的解决这些问题,大大提高无线基站的互连性能。图8显示了一种无线基站基带互连框图。在这里,SRIO实现了大部分器件之间的互连,甚至可支持DSP进行直接背板传输。

图8 SRIO提高无线基站互连性能

通过SRIO交换器件互连可以进一步提高基带处理的灵活性,图9显示了一种基带SRIO交换互连的框图。这种互连有利于实现先进的基带处理资源池架构,数据可被送到任何一个通过SRIO交换器互连的处理器中,从而达到各个处理器的负载均衡,更加有效的利用系统的整体处理能力。

图9 SRIO交换为无线基站基带处理提供更大的灵活性

综上所述,对嵌入式系统尤其是无线基础设施,串行RapidIO是最佳的互连技术。高达10Gbps的带宽、低时延和低软件复杂度满足了飞速发展的通信技术对性能的苛刻需求;串行差分模拟信号技术满足了系统对管脚数量的限制,及对背板传输的需求;灵活的点对点对等互连、交换互连,和可选的1.25G/2.5G/3.125G三种速度能满足多种不同应用的需求。

随着串行RapidIO技术的发展成熟,以及越来越多的厂商的支持,串行RapidIO技术必将成为高性能嵌入式互连的主流技术。

|