标签:

1 新建工程

在quartus ii 中新建一个工程(hello.Prj)

2 Qsys硬件系统搭建

在quartus ii中开启Qsys:

打开Qsys界面发现System Contents下已经有了一个clk_0,如下图所示。为搭建一个最小系统还必须添加一些必要组件,比如NIOS II 处理器、JTAG、onchip_ram、systemID等。

添加JTAG:

添加NIOS II 处理器

添加onchip_ram

添加pio

添加system ID

在system contents 的connections进行连接,时钟clk和reset与所有组件的clk和reset连接,nios2_qsys的data_master和instruction_master 均与

代表onchip_memory2_0 的从机总线s1 连接上。而其他作为总线slave 的外设均连接到nios2_qsys_0的data_master上

将需要与外部连接的接口属性设置为export,这里将pio设置为输出如图所示:

这里NIOS II 处理器还要设置一下,将其Reset Vector和Exception Vector均设为onchip_mem:

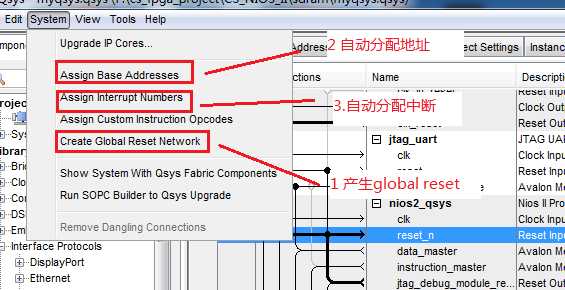

让后进行create globle reset,自动分配地址和中断操作:

很多外设都有中断信号,在我们的Qsys中也需要将对应的IRQ一列中的外设和NIOS II处理器连接上。在没有连接是,对应外设上有一个空心的小点,如果点上去,则不是实心的

小圆,而是可以填写数字的一个空心大圆,对应可以写上它的中断优先级。

最后在generation中进行相关设置,13.0 simulation和testbench处都设置为none ,否则容易报错。

点击generation 进行系统生成。

3 例化Qsys

回到Quartus II,我们新建一个名为hello.v的verilog源代码文件。然后输入以下代码;

module hello(clk,rst_n,led); input clk; input rst_n; output led; myqsys u0 ( .clk_clk (clk), // clk.clk .reset_reset_n (rst_n), // reset.reset_n .pio_external_connection_export (led) // pio_external_connection.export ); endmodule

然后将myqsys.Qsys和ex2.v文件添加到工程中

对工程进行综合编译。

进行引脚分配,然后再最终综合,布局布线。。。。。

4 EDS中建立软件工程

打开EDS软件。首先弹出如下的workspace路径设置对话框,采用默认设置并点击OK进入软件。

进入EDS软件界面

菜单栏点击File?New?Nios II Application and BSP from Template新建一个模板工程。

如图加载系统硬件,即sopcinfo文件,

选择好SOPC文件后,默认选中CPU为nios2_qsys,给软件工程命名为ex3swprj,最后

再选择空白工程模板,然后点击Finish完成工程的创建。

在ex2工程中新建一个main.c文件

打开main.c文件进行软件编程

/* * main.c * * Created on: 2015-3-30 * Author: Administrator */ #include "alt_types.h" #include "altera_avalon_pio_regs.h" #include "sys/alt_irq.h" #include "system.h" #include <stdio.h> #include <unistd.h> void delay(void); int main(void) { alt_u8 timer = 0; while(1) { printf("Hello CS!I am NIOS II! %d\n",timer); delay(); timer++; } return 0; } //延时函 void delay(void) { alt_u32 i=0; while(i < 4000000) { i++; } }

先不要对工程进行编译,首先对BSP Editor进行一定的设置。

进入BSP Editor,需要按照后面一个表格做设置,完成后点击Generate按钮完成后Exit即可。

前面的BSP Editor中按照如下要求做设置。另外提醒大家注意的是,每次硬件工程(在Quartus II中)的任何更改,建议在编译软件工程前逗号重新在BSP Editor中Generate一次,

这是为了保证软硬件的一致性,否则编译将出错。

接着回到EDS中,分别选中ex2swprj_bsp和ex2swprj,然后右键点击选中Build Project。这就完成了软件平台的搭建

5 板级调试

首先下载sof文件到FPGA中

在EDS里,选中应用工程,右键点击并选择Rus as?Niso II Hardware。第一次操作通常会弹出Run Configuration界面,首先在Project一栏中选择好当前工程和当前的软件下载文

件(在应用工程目录下的elf文件 )。

在Target Connection页面,需要检测下载硬件信息。可以多次点击右侧的Refresh Connections按钮,直到左侧的Connections下出现我们的下载线信息,此外,我们还需要让左下角的Run按钮有效(即变亮可以点击)。点击Run开始软件的在线运行。

观察Nios II Console窗口:

至此已完成了一个hello cs的NIOS II 例程。

2015 3月30日

CSLegened

标签:

原文地址:http://www.cnblogs.com/CSLegend/p/4379155.html