标签:

文章来源 http://blog.chinaaet.com/detail/34609

熟悉了xps的操作,IP添加,总线连接设置,图形化方法检查(open graphical design view),检查总线及端口连接。

在file下面的图标中,打开导出到SDK并启动,完成程序编写。

参考超群天晴的博客http://www.cnblogs.com/surpassal/,使用XPS为PS 处理系统 添加额外的IP。从IP Catalog 标签添加GPIO,并与ZedBoard板子上的8个LED灯相连。当系统建立完后,产生bitstream,并对外设进行测试。以后还有一个很重要的自定义用户Ipcore设计,下个实验来做下这个(一开始以简单的led和sw为例)。这个实验就使用呢自带外设IP。

使用的平台是XPS 14.2+SDK 14.2

一 硬件配置

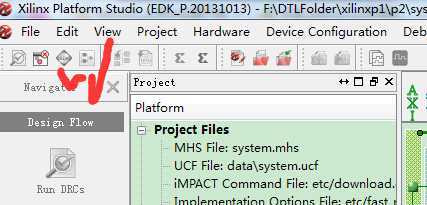

1、启动xps创建工程Create New Project Using BaseSystem Builder

创建工程。因为PS系统和FPGA连接是采用AXI接口,因而选择内部互联类型(Interconnect Type) 为AXI。

选择设计平台为ZynqZC702

到外设配置界面,系统会默认有GPIO_SW和 LEDs_4bits 这两个外设,我们不需要,remove

2、添加AXI GPIO外设

进入主界面

工程建立后,在IPCatalog中,找到GeneralPurpose IO,找到 AXI GPIO,双击添加到系统中。

修改元件实例化名称为axi_LED,这个名称就是将要实例化连接到PS的元件。将长度改为8,其他默认。

Ok后出现

点击ok,

点开BusInterfaces标签,可以看到系统汇总现在有PS(这里是processing_systems7_0) 、添加的外设axi_LDs 和AXI内部互联总线axi_interconnet_1。可以看到对于 axi_interconnet_1来说,PS是AXI主设备,外设是AXI从设备。

在Port标签,将IO_IF中的GPIO_IO设置为External Ports,将Port名称改为LED。LED就是顶层对外的引脚名称,注意这里和参考博客不同。按照参考博客中的不能成功。

0521注:此处名字试过了,改不了,所以ucf文件与此同名。

3、设定引脚约束

在project标签中,找到system.ucf约束文件,

4、点击Generate BitStream,生成bitstream

5、将硬件配置导入到SDK,启动SDK。这里需要将bitstream和BMM文件同时包括到SDK中。

二、创建软件程序

使用新建工程向导。注意,这里使用工程模板为Memory Tests。

新建工程后,会有几个存储空间测试的文件,我们不需要,删掉。

修改main文件,内容如下

//@超群天晴 http://www.cnblogs.com/surpassal/ #include <stdio.h>

#include "xparameters.h"

#include "xil_types.h"

#include "xstatus.h"

#include "xil_testmem.h"

#include "xgpio.h"

#include "platform.h"

void print(char *ptr);

int main()

{

static XGpio LED_Ptr;//定义GPIO指针

int XStatus;//函数返回状态

init_platform();

print("ZedBoard project_7: PS_AXI_LED\n\r");

print("xzy 2013年09月18日18:12:31\n\r");

注意下面一定要改名字哦,以前XPAR_AXI_LDS_DEVICE_ID

XStatus = XGpio_Initialize(&LED_Ptr,XPAR_AXI_LED_DEVICE_ID);

if(XST_SUCCESS != XStatus)

print("GPIO INIT FAILED\n\r");

XGpio_SetDataDirection(&LED_Ptr, 1,0x00);//通道1;设置方向 0 输出 1输入

XGpio_DiscreteWrite(&LED_Ptr, 1,0xaa);

cleanup_platform();

}

在下载软件程序前,需要将bitstream文件烧如FPGA,对FPGA进行配置。在工具栏中Xilinx tools->Program FPGA,也可以使用XPS中的Device Configuration->Download Bitstream等其他配置FPGA的方式。

配置完FPGA后,下载软件程序,可以看到超级终端显示调试信息:

注明:helloworld工程也是可以的,不一定非要是memory test工程。

zedboard--zynq使用自带外设IP让ARM PS访问FPGA(八) 转载

标签:

原文地址:http://www.cnblogs.com/dujianzw/p/4521275.html