标签:

前提:前段时间搞过Plan Ahead 、XPS 、SDK下搭建xilinx 的zynq 7000(zerdboard)的PS和PL联机试验,尝试定义平台、搭建总线和DMA,见之前的博客。

趁热打铁,最后一遍过一下altera的Nios II 在3c120片上ram流水灯试验。

平台:quartus 10 + NIOS II EDK 10,3c120+EPCS16(64)+CFI Flash + Sdram(Sram),这是标配。

1、搭建quartus的硬件平台:

PLL+LE模块(FPGA 本体逻辑模块)+NIOS核(nios),相当于SOPC + FPGA 设计了。

1、1 打开quartus:

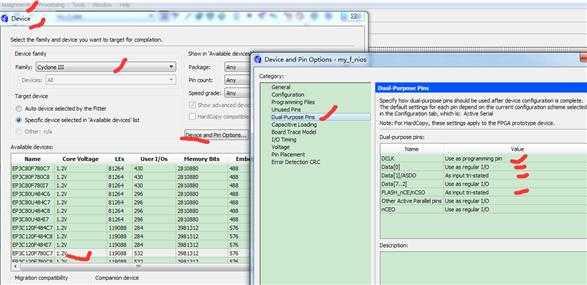

设置芯片、配置EPCS——falsh的引脚:

(不使用epcs的跳过,此处是 cyclone 3环境,要把epcs falsh 的四个引脚设为常规IO,配置完FPGA后当做常规flash来存储nios的程序用)。

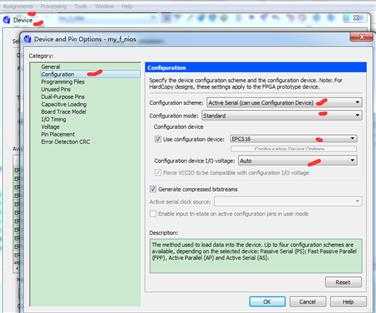

1、2 配置生成sof 、pof文件:

同样是在assigned、device、下:

1、3新建图形化设计文件 bolck digama/schematic 文件:

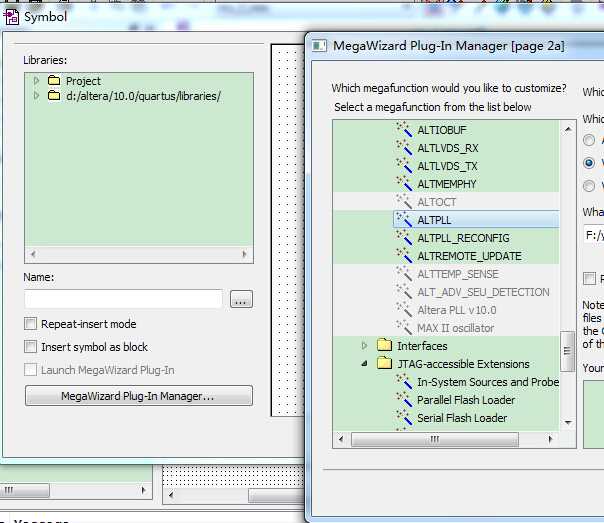

双击空白处,添加PLL模块:

1、4 自检一个LED点亮的文件,然后编译、导航栏右键文件生成 creat synbom 文件,加入到设计文件中:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_signed.all;

entity my_f_led is

port

(

clk: in std_logic;

rst: in std_logic;

f_usr_led : out std_logic_vector(1 downto 0)

);

end ;

architecture arch_my_f_led of my_f_led is

signal clk_5m:std_logic;

begin

proc1_car_calcu:process(clk,rst)

variable proc1_state : std_logic_vector(7 downto 0);

variable proc1_i : integer range 0 to 15;

variable proc1_cnt : std_logic_vector(23 downto 0);

begin

if rst = ‘0‘ then

proc1_state := (others=>‘0‘) ;

proc1_i := 0 ;

proc1_cnt := (others=>‘0‘) ;

elsif rising_edge(clk) then

proc1_cnt := proc1_cnt + x"000001";

f_usr_led(0) <= proc1_cnt(22);

f_usr_led(1) <= proc1_cnt(23);

end if ;

end process ;

end arch_my_f_led;

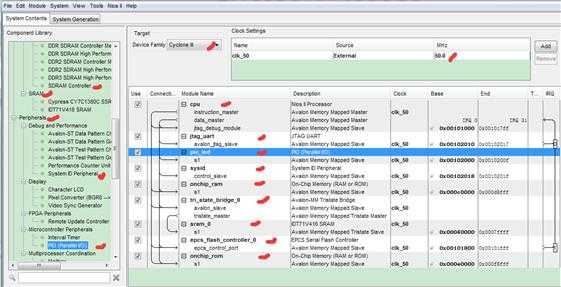

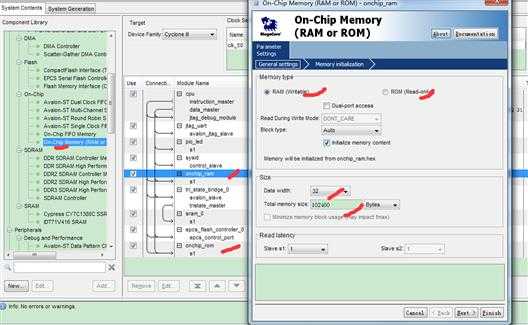

1、5 菜单上选择 tool sopc builder,生成一个sopc,名字自己起,添加nios 免费核、添加jtag uart、PIO、epcs flash、sdram、system id等

对照图上添加,开始的打算是:

nios核程序存在epcs flash(或者CFI falsh)上(reset vector 选择),运行在onchip ram 或者SDRAM(sram,下拉选择)上(exception vector 选择)。

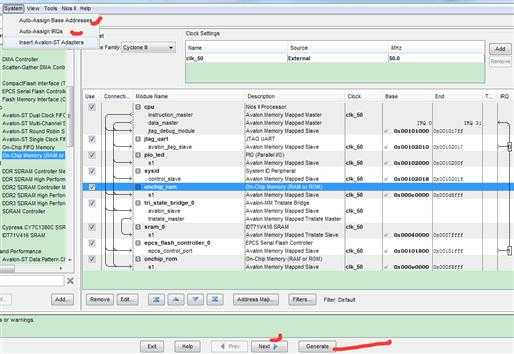

1、6 接下来菜单、system-》auto——assgin 中断及基地址、然后下一步、生成sopc文件及模块,要等很久才完成保存退出。

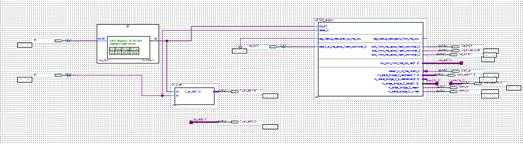

1、7 加入project下的nios 核。配上引脚。如图pll+PL+nios:

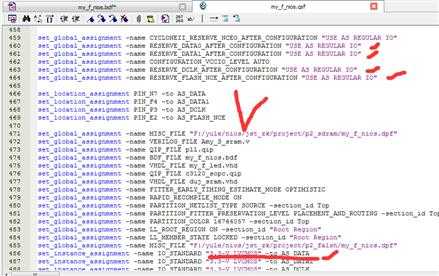

1、8编译前打开qsf文件,把epcs的regular io 配置一下:

注意前后顺序(设置regular IO 在引脚分配之前),IO的电压在pin planer里面就该设置为3.3V,因为epcs 配置电压就是3.3V。

接下来保存该文件,编译生成sof 及pof,占用资源是2000 多个LE。

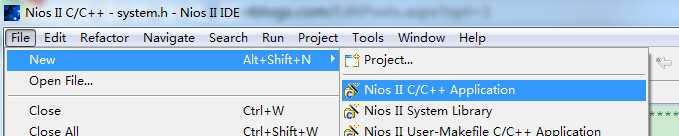

2、接下来打开nios IDE,建立nios 的软件

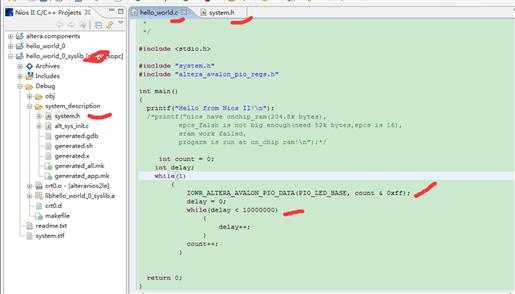

2、1 新建application c/C++ 项目,选择helloword模板,改一下成led的程序。

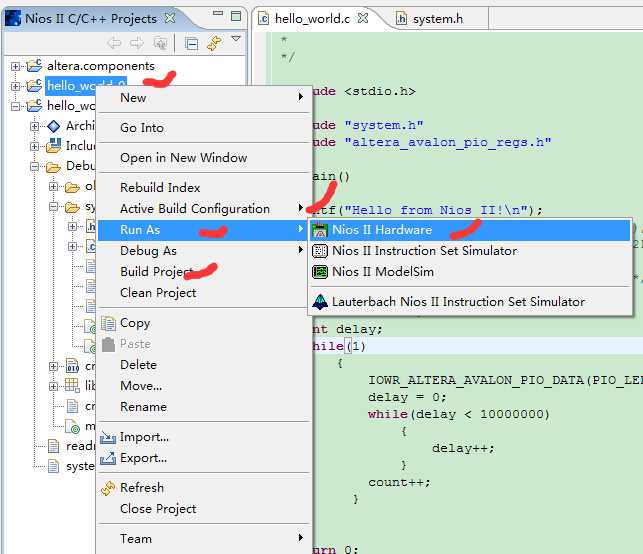

2、2 选中导航栏中的hello word 0 项目,右键 build project(注意调试就是debug ,完了之后是release版)。

编译完成后调试是quartus 下载 sof 文件,即jtag 接口 ,然后选中项目 run as nios hardware;

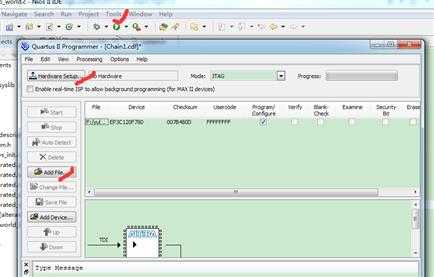

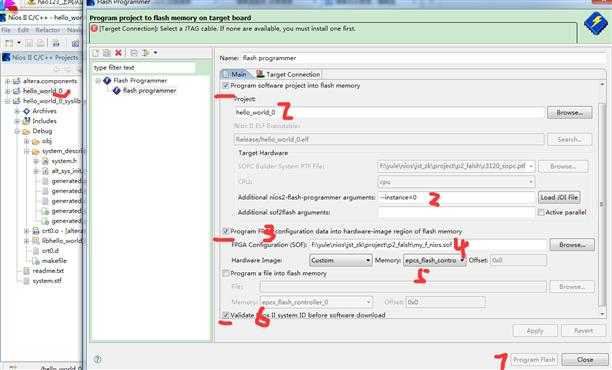

运行就是flash program,Cable 也是接在jtag上。下面是两个对应的图。

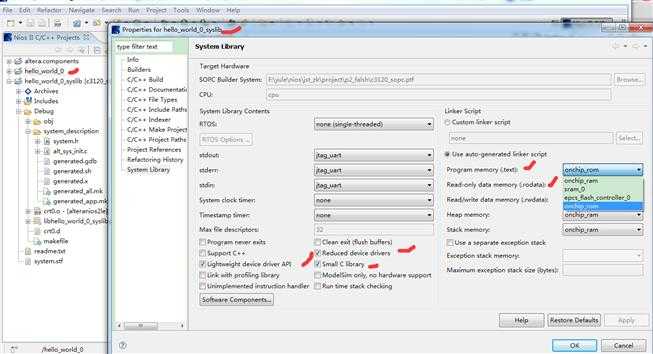

2、3 库文件及编译减小体积,这里程序的。text 及 rodata在 cfi falsh 运行模式下选择cfi flash ;

我想选择epcs falsh,编译总是提示epcs满了不能放下,导致这个地方卡死了无法继续进行。

调试模式下(在ram里运行,掉电消失),都选择sdram 或者ram。

总结:nios我目前只实现在run as hardware 调试模式(库文件都选择ram);

程序段放在epcs flsh上编译老出错,无法进行下一步;

程序段放在ram上能progarm 到epcs flash,但是掉电后ple部分ok,nios根本跑步起来。

先到这里吧,毕竟不是标配的运行环境。

标签:

原文地址:http://www.cnblogs.com/dujianzw/p/4553049.html