标签:style blog http color 使用 strong

转载自:http://blog.chinaunix.net/uid-20543672-id-3018233.html

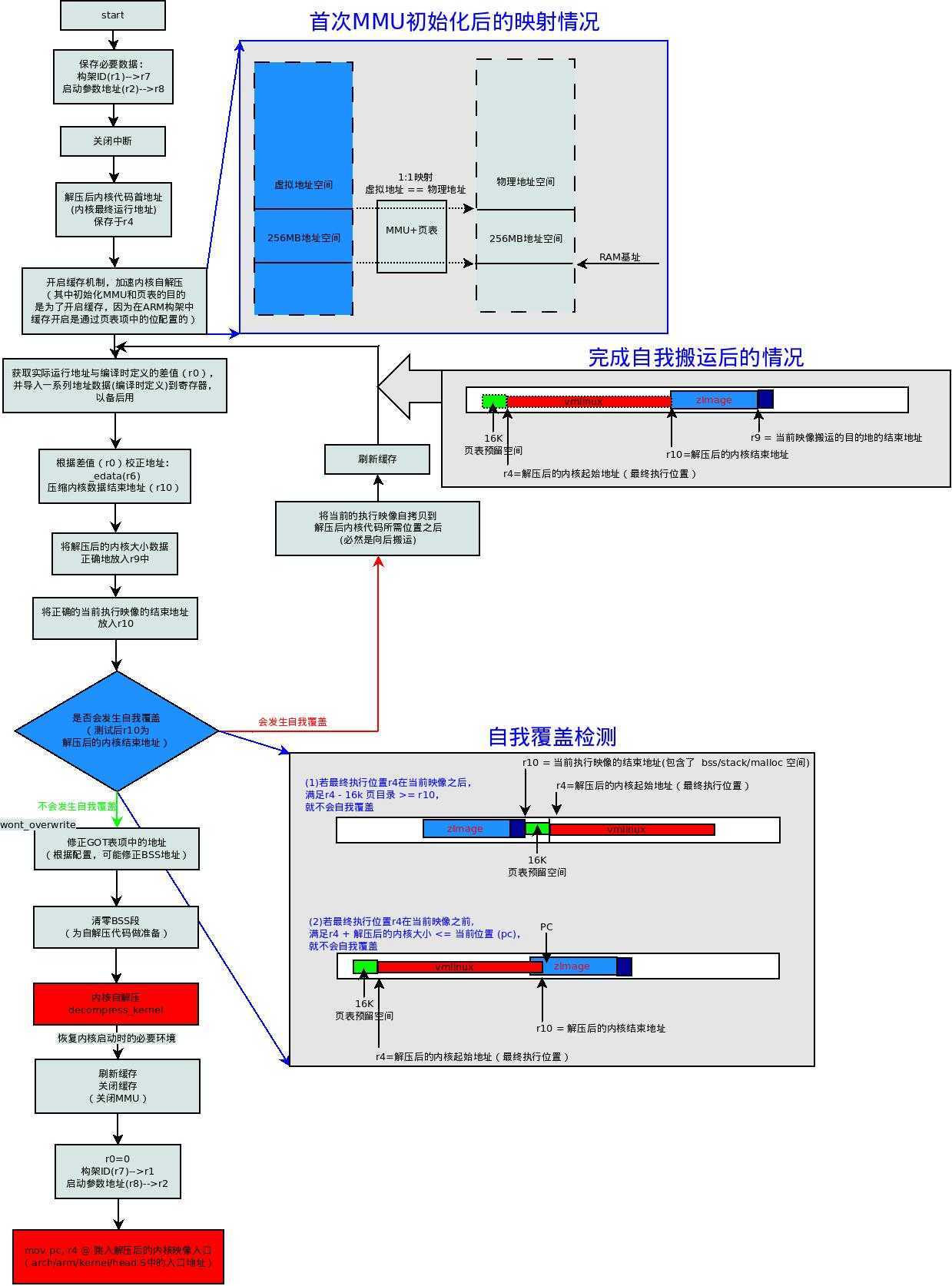

研究内核源码和内核运行原理的时候,很总要的一点是要了解内核的初始情况,也就是要了解内核启动过程。我在研究内核的内存管理的时候,想知道内核启动后的页表的放置,页表的初始化等信息,这促使我这次仔细地研究内核的启动代码。

| 1. CPU 寄存器的设置: | R0=0; R1=Machine ID(即Machine Type Number,定义在linux/arch/arm/tools/mach-types); R2=内核启动参数在 RAM 中起始基地址; |

| 2. CPU 模式: | 必须禁止中断(IRQs和FIQs); CPU 必须 SVC 模式; |

| 3. Cache 和 MMU 的设置: | MMU 必须关闭; 指令 Cache 可以打开也可以关闭; 数据 Cache 必须关闭; |

Linux内核源码分析--内核启动之(1)zImage自解压过程(Linux-3.0 ARMv7),布布扣,bubuko.com

Linux内核源码分析--内核启动之(1)zImage自解压过程(Linux-3.0 ARMv7)

标签:style blog http color 使用 strong

原文地址:http://www.cnblogs.com/pengdonglin137/p/3812485.html