标签:style blog http color os 2014

分频器还是比较简单的,一般的思路是:每数几个时钟就输出一个时钟。最简单的当数二分频器了,每当时钟上升沿(或下降沿)就把输出翻转一下。

这样就刚好实现了二分频器了。

网上也搜到了最简实现”二分频最简单了,一句话就可以了: always @ (negedge clk) clk_2<=~clk_2;“

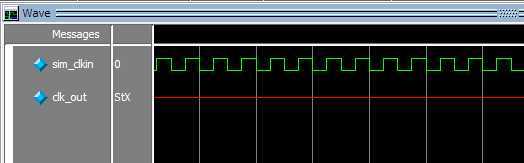

但仿真时却发现无法输出

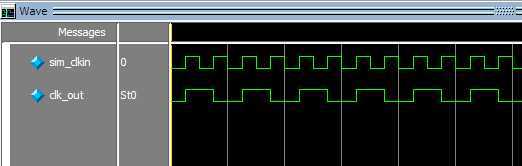

分析是因为输出信号的初始状态不确定造成的,于是加了一句初始化,就可以正常分频了

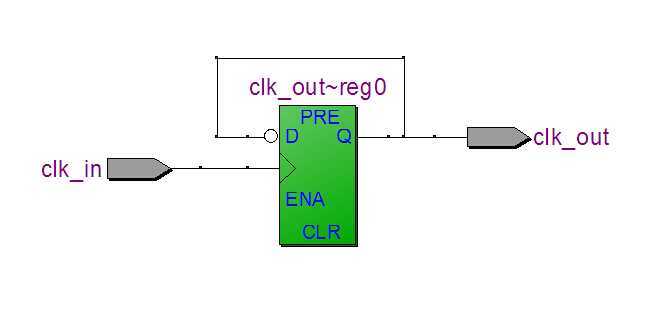

但观察他们生成的逻辑结构图是一样的

完整代码如下:

module divider2(clk_in, clk_out); input clk_in; output clk_out; reg clk_out; initial clk_out <= 1‘b0; always@(posedge clk_in) clk_out <= ~clk_out; endmodule

FPGA入门学习第一课:二分频器,布布扣,bubuko.com

标签:style blog http color os 2014

原文地址:http://www.cnblogs.com/aozima/p/3840634.html