标签:

总结:

简单来说,因为flip-flop 端口到 gate 有一段delay,如果clock 那段delay明显要大,setup就可能是负值了;如果flip-flop端口gata那段delay明显太大,hold就可能取负值了。在我看来,二者的作用都是用来微调数据和时钟经过filp-flop传输时的同异步问题,避免数据和时钟发生大的出入从而无法正常经过过Flip-flop传输信号。

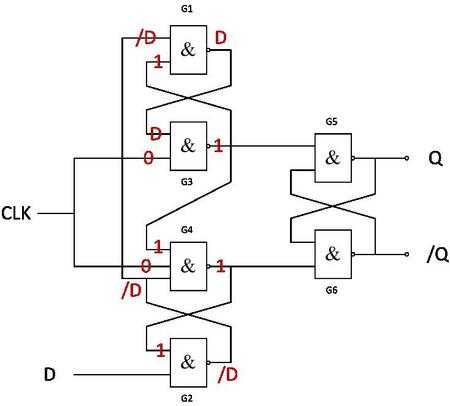

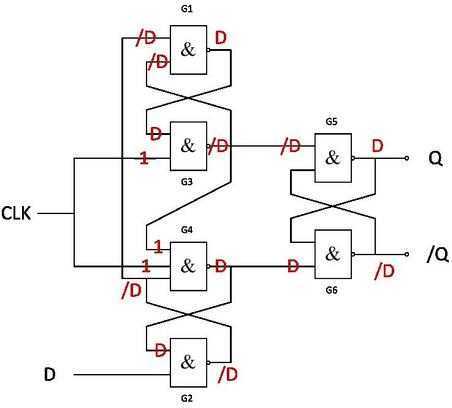

如下所示Edge-Triggered(rise)D Flip-flop ,在针对单个Flip-flop而言,建立时间Tsu一般对应G1和G2与非门的延迟,保持时间Thold一般对应G3和G4的延迟。图1中,CLK从0至1,D从d1到d2,必须提前一个Tsu使G1/G2 输出端转变成d2。图2中,CLK保持1,D 从d2到d3,必须推迟一个Thold使G3/G4输出端已经为d2。对应Timing Library中setup和hold time应该是指,如图1 ,CLK到G3/G4的Delay太大,为了保证数据能“按时”到达G3/G4输入端使信号D正常输入,所以setup time取负值;如图2,D到G2的Delay太大,D到G1/G2 与非门的delay太大,可能会影响数据传输速率等因素,则hold 取负值。

1.边沿D触发器(上升沿)与其setup time和hold time原理

当CLK=0时,与非门G3和G4的输出均为1,输出的1反馈到G1和G2作为输入,导致G1和G2的输出分别为D和/D,输出的D和/D又反馈到G3和G4;而G5和G6在此期间一直锁存着之前的数据, 不受输入影响。

2,当CLK=1时,与非门G3和G4的输出变为/D和D,输出到G5和G6作为输入,根据锁存器的原理,G5和G6最终会稳定的输出Q和/Q

再考虑与非门的延时。

设G2和G1 的延迟为T1,当CLK=0时,如果D在时钟跳变前的T(T<T1)时间才从d1更新为d2,那么G1和G2在时钟跳变时刻的输出值肯定是d1和/d1,而不是d2和/d2,进而影响到G3和G4的输出。如果要使得G1和G2的输出为d2和/d2,就必须要求D起码在时钟跳变之前的T1时间内维持d2稳定不变。这个T1就是建立时间Tsu。这个还可以理解。

当CLK=1时,G3和G4的延迟为T2,当CLK=1时,如果D在时钟跳变之后的T(T<T2)时间从d2更新为d3,由于G3和G4的输入在T的时间内还保持为1,所以D的更新会影响G2和G1的输出,进而影响G3和G4的输出,进而影响G5和G6的输出,造成输出Q和/Q发生震荡或者亚稳态。T2为保持时间Thold。

2.Setup和Hold为负值的原理

由上面的的原理可看出:Tsu和Thold根本不能为负值。TLF文件中setup time和hold time应该取的是一个同步传输时序电路的参考时间段,以使数据通路和时钟通路在穿越Flip-flop时不会出现异步现象从而导致数据传输出现震荡或者亚稳态。

图1中,CLK从0至1,D从d1到d2,必须提前一个Tsu使G1/G2 输出端转变成d2。图2中,CLK保持1,D 从d2到d3,必须推迟一个Thold使G3/G4输出端已经为d2。对应Timing Library中setup和hold time应该是指,如图1 ,CLK到G3/G4的Delay太大,为了保证数据能“按时”到达G3/G4输入端使信号D正常输入,所以setup time取负值;如图2,D到G2的Delay太大,D到G1/G2 与非门的delay太大,可能会影响数据传输速率等因素,则hold 取负值。

标签:

原文地址:http://www.cnblogs.com/kylechiang/p/4773215.html