标签:

作者:MiS603开发团队

日期:20150911

公司:南京米联电子科技有限公司

论坛:www.osrc.cn

EAT博客:http://blog.chinaaet.com/whilebreak

博客园:http://www.cnblogs.com/milinker/

本实验将实现FPGA 芯片和PC 之间进行千兆以太网数据通信, 通信协议采用Ethernet UDP 通信协议。 FPGA 通过RGMII 总线和开发板上的RGMII PHY 芯片通信,RGMII PHY 芯片把数据通过网线发给PC。以太网数据通信的示意图如下:

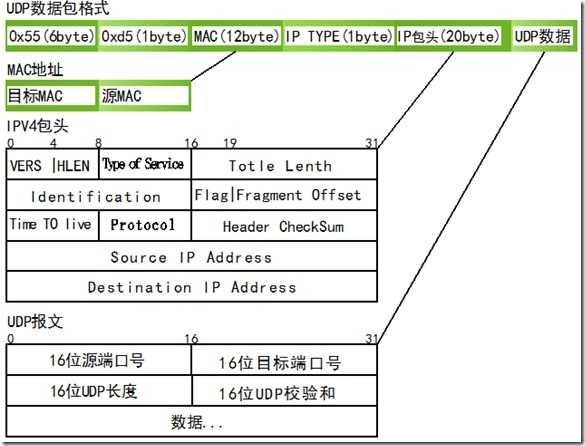

1)UDP报文在IP数据包中的位置:

2)UDP报头:

3)本设计完整的UDP数据结构:

PV4报头长度为20字节,并且本次测试程序接收后没有做任何处理。

UDP报头8字节

2字节源端口号,2字节目标端口号,2字节UDP长度,2字节UDP校验,本次程序中,校验和没有使用。

下载程序05_RGMII_UDP_TEST到开发板。并且采用XCAP软件进行测试 软件下载地址:http://pan.baidu.com/s/1dD0gwP7

Step1:打开XCAP软件,新建报文组和报文

Step2:双击报文,设置链路层参数

Step3:点击下一步,设置IP网络层参数。

Step4:下一步,设置UDP端口。

Step5下一步,设置UDP发送数据。

Step6:保存,回到首页,勾选要发送的报文,选择千兆网网卡和发送间隔。

RGMII_UDP_TEST 顶层文件负责调用子程序,并且在RGMII_UDP_TEST中初始化RAM数据。

rgmii_rx 为PHY部分RGMII转GMII驱动文件

rgmii_tx 为PHY部分GMII转RGMII驱动文件

iprecieve 实现UDP协议的解码,并且把数据缓存到RAM中

insend 实现UDP协议的编码,并且从RAM读取数据发送出去

详细代码请参考源码。

1)、抓取数据 UDP数据接收

图5.2.4.1

图5.2.4.2

(1)图5.2.4.1中,可以看见每一个data_o_valid脉冲,都对应着一个32位的UDP接收数据ram_wr_data。

(2)图5.2.4.2 图中,接收了5个32位数据,最后1个数据不足4字节进行补0处理,第一个脉冲存06000000,第二个脉冲存12345678,第三个脉冲存00000000,第四个脉冲存00000000,第五个脉冲存00000000,(补齐了0),该接收与PC测试发送数据一致。

(3)由测试可以看出,在接收数据的同时,UDP数据即被存入RAM中,不耽误下一帧的接收,实现带宽最大化。

2)、Chipscope抓取数据 UDP数据发送

从图5.2.4.3中可以看出当txen为1的时候程序正确发送了接收到的数据。

3)、PC端数据检测

对照XCAP接收到的数据,可以看出,发送结果和接收结果一致,另外可以通过观察数据包的结构核对UDP数据包结构。

详细参考:05_RGMII_UDP_TEST

本节通过一个简单的UDP协议解码和编码,并且调用RGMII底层驱动,实现了PC和开发板之间的通信。详细讲解了XCAP网络抓包软件的使用,为今后对网络协议的分析打好了基础。通过本节的学习,小白们瞬间成为了千兆网通信高手。

标签:

原文地址:http://www.cnblogs.com/milinker/p/4804899.html