标签:

I ‘m looking for the best RC time constant and its reason in a PWM to convert digital signal to analog based

on duty-cycle and frequency and other parameters.

PWM frequency is 10 kHz.

The best RC is infinite, then you have a perfectly ripple-less DC output.

Problem is that it also takes forever to respond to changes in the duty cycle.

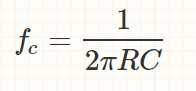

So it‘s always a tradeoff. A first-order RC filter has a cutoff frequency of

and a roll-off of 6 dB/octave = 20 dB/decade.

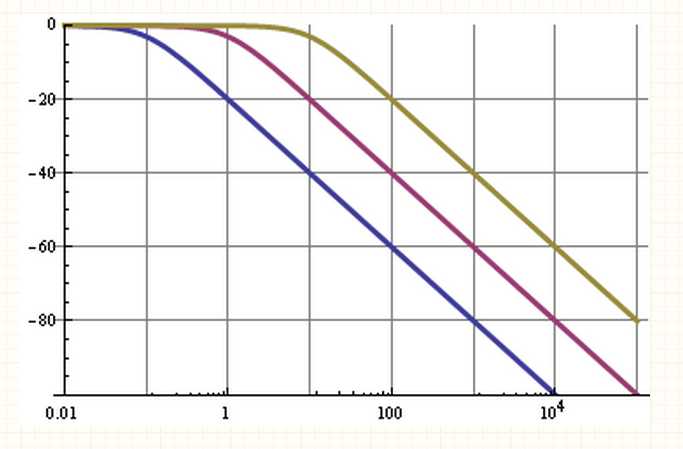

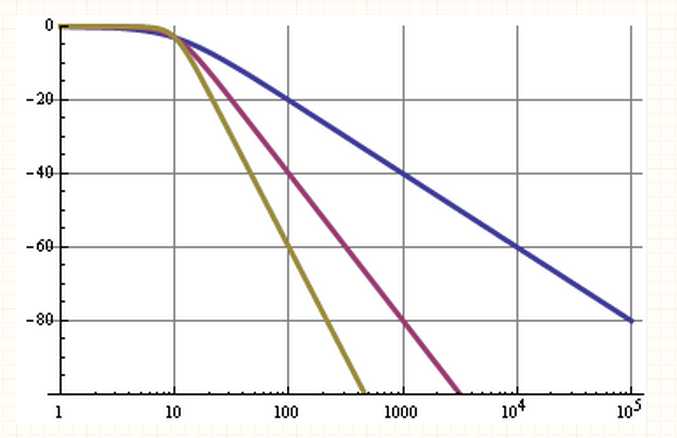

The graph shows the frequency characteristic for a

0.1 Hz (blue), a 1 Hz (purple) and a 10 Hz (the other color) cutoff frequency.

So we can see that for the 0.1 Hz filter the 10 kHz fundamental of the PWM signal is suppressed by 100 dB, that‘s not bad;

this will give very low ripple. But!

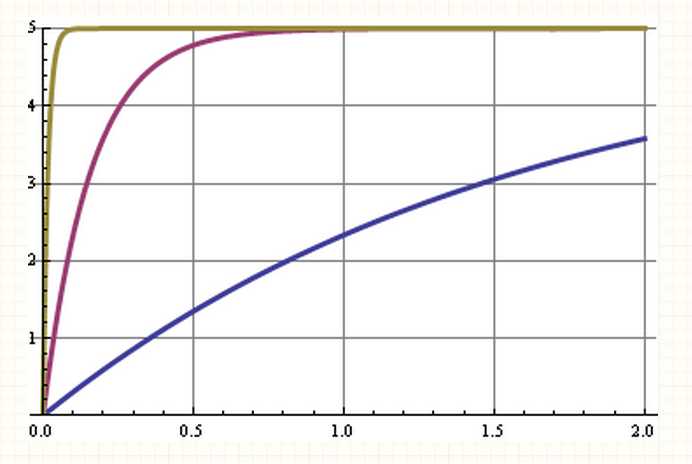

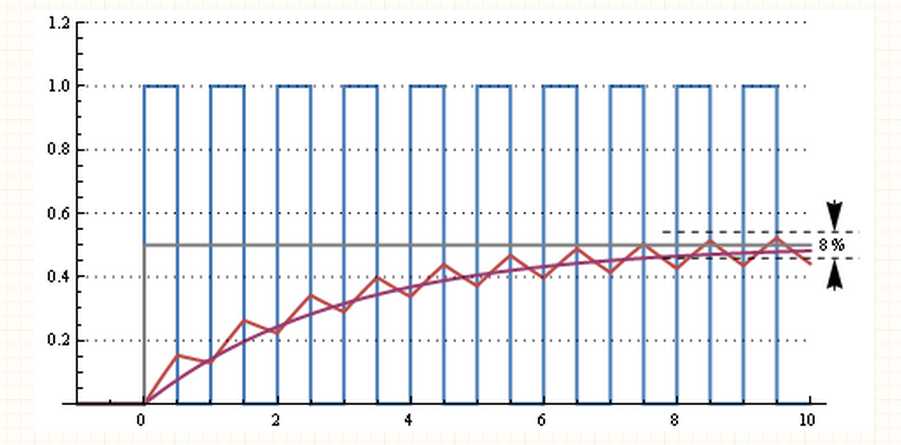

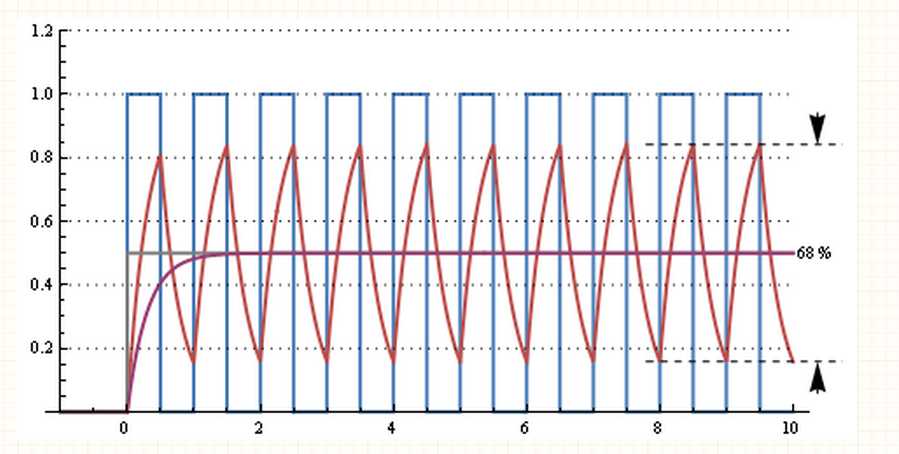

This graph shows the step response for the three cutoff frequencies.

A change in duty cycle is a step in the DC level, and some shifts in the harmonics of the 10 kHz signal.

The curve with the best 10 kHz suppression is the slowest to respond, the x-axis is seconds.

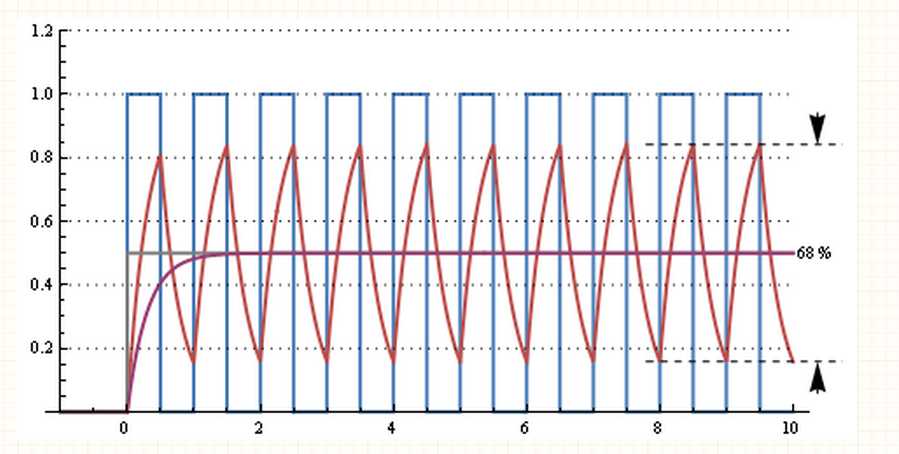

This graph shows the response of a 30 µs RC time (cutoff frequency 5 kHz) for a 50 % duty cycle 10 kHz signal.

There‘s an enormous ripple, but it responds to the change from 0 % duty cycle in 2 periods, or 200 µs.

This one is a 300 µs RC time (cutoff frequency 500 Hz).

Still some ripple, but going from 0 % to 50 % duty cycle takes about 10 periods, or 1 ms.

Further increasing RC to milliseconds will decrease ripple further and increase reaction time.

It all depends on how much ripple you can afford and how fast you want the filter to react to duty cycle changes.

This web page calculates that for R = 16 kΩ and C = 1 µF

we have a cutoff frequency of 10 Hz,

a settling time to 90 % of 37 ms for a peak-to-peak ripple of 8 mV at 5 V maximum.

You can improve your filter by going to higher orders:

The blue curve was or simple RC filter with a 20 dB/decade roll-off.

A second order filter (purple) has a 40 dB/decade roll-off,

so for the same cutoff frequency will have 120 dB suppression at 10 kHz instead of 60 dB.

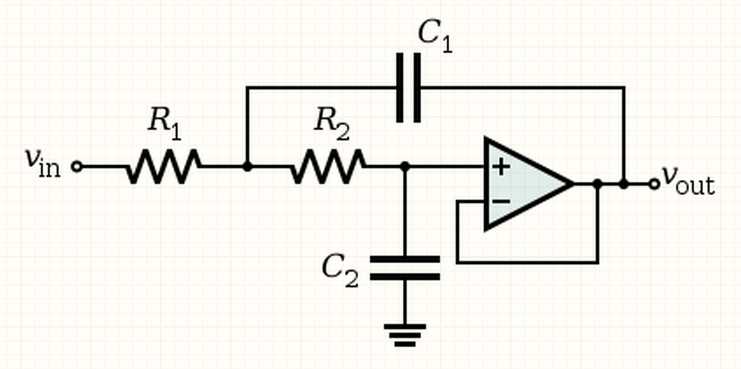

These graphs are pretty ideal and can be best attained with active filters, like a Sallen-Key.

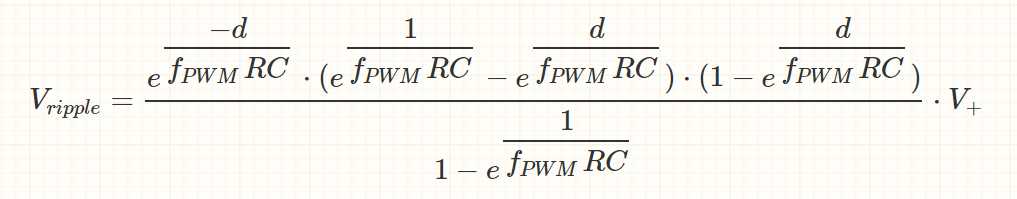

Equations

Peak-to-peak ripple voltage for a first order RC filter as a function of PWM frequency and RC time constant:

"d" is the duty cycle, 0..1.

Ripple is the largest for d = 0.5

Step response to 99 % of end value is 5 x RC.

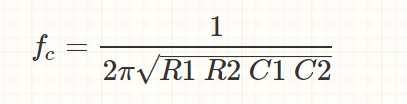

Cutoff frequency for the Sallen-Key filter:

For a Butterworth filter (maximum flat):

R1 =R2, C1 = C2

Fc = 1 / ( 2 * pi * sqrt( R1 * R1 * C1 * C1 ) ) = 1 / ( 2 * pi * R1 * C1 ) ) = 1/ ( 6.3 * ( R1 * C1 ) ) = 0.16 / ( R1 * C1 )

As Steven said, it‘s a tradeoff between attenuating the PWM frequency versus response time.

This is why any such decision has to start with a spec of what you want from the resulting analog signal.

What signal to noise ratio does it need to be, or at least how much noise at the PWM frequency can you tolerate?

How fast does it have to settle to the noise floor level?

Or conversely, what is the upper frequency you care about?

Note that it may not be possible to meet a particular set of criteria with a particular PWM output.

Let‘s say you wanted good quality voice output.

We‘ll say that‘s up to 8 kHz and 60 dB signal to noise.

That isn‘t going to happen with any reasonably tractable analog filter with 20 kHz PWM,

and certainly not with anything as simple as a single R and C.

As a example, let‘s work backwards and see what the PWM characterstics would have to be

to support the above voice example with a single R,C filter.

We‘ve already said the -3 dB rolloff frequency is 8 kHz,

so that‘s what we set the R and C to.

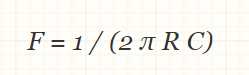

The rolloff frequency of a single R,C filter is:

When R is in Ohms, C in Farads, then F is in Hertz.

It should be obvious this equation can be rearranged to solve for any of R, C, or F given the other two.

I keep 1/(2 π) = .15915 always in a register in my calculator

because this computation comes up regularly in electronics.

Then I simply divide that by two of R, C, or F to get the third.

We have two degrees of freedom and the above equation only nails down one of them.

The other can be thought of as the impedance you want the resulting signal to have.

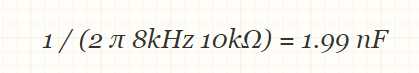

Let‘s shoot for around 10 kΩ, which is what we‘ll make R just to see what C comes out to:

That‘s basically the standard capacitor value of 2 nF, so we‘ll just go with that.

If it hadn‘t come out to a common value, we‘d have picked a near one then gone back and adjusted R accordingly.

Resistors are available in much finer variations and at higher tolerances than ordinary capacitors,

so you usually find a close capacitor value, then let that drive the exact resistor value.

So we‘ve settled on R = 10 kΩ and C = 2 nF.

Note that this has come from the 8 kHz upper frequency requirement.

We have no more choices to make, so the settling time and signal to noise ratio will be what it will be.

All we can do now is determine whether it will be good enough, or conversely,

what PWM characteristics would be necessary to support the output signal specs.

Since the spec was a signal to noise ratio of 60 dB,

that means the noise must be less than 1 part in 1000 of the voltage,

which means the PWM frequency must be attenuated by that much.

A single R,C filter attenuates inversely proportional to frequency after the rolloff frequency.

This is a approximation that breaks near the rolloff frequency and below,

but it‘s good enough in most cases after a octave or two past the rollof frequency.

In other words, 16 kHz will be attenuated by 2 with some error, 32 kHz by 4 with less error,

and after that you can pretty much just divide the frequency of interest by the rolloff frequency to get attenuation.

We want the PWM frequency to be attenuated by 1000, which means it needs to be 8 MHz or higher.

That‘s high but doable with some processors.

For example, some of the PIC 24H and dsPIC line

have a special "power supply control" PWM module that operate at just under 1 GHz.

Now let‘s look at the PWM resolution.

Again, this is driven by the 60 dB signal to noise spec, which we know already means 1:1000.

That would require a PWM resolution of at least 999 (you always get one more output level than the PWM resolution).

That means the internal PWM slice clock needs to run 999 times the 8 MHz PWM output frequency, or basically 8 GHz.

Not gonna happen with reasonably available off the shelf parts.

However, there is a way to get around these limitations, and that is to use more than just a single R,C filter.

When I want a nice analog signal, I usually use two or three of them in succession.

Let‘s see how using three successive R,C filters changes things.

We originally said our upper frequency of interest was 8 kHz,

which implies we can tolerate that being 3 dB down unless we say otherwise.

A single R,C filter will attenuate by 3 dB at the rolloff frequency, so we put it at right at 8 kHz.

We can‘t have three filters at 8 kHz since they would attenuate by 9 dB there combined.

So, we move the filters out by the number of poles (separate R,C filters in this case).

The three R,C filters (three poles) are therefore at 24 kHz.

It seems like we lost ground doing this, but the big advantage is

that the frequencies above that are now attenuated by the ratio cubed instead of just the ratio as with a single pole.

Again we want the PWM frequency to be attenuated by 1000, which is 10^3,

so we only need to be 10x beyond the filter rolloff frequencies which means 240 kHz is high enough.

That‘s a big difference from 8 MHz.

Now the internal PWM clock or PWM slice frequency only needs to be 240 MHz.

That‘s still high but attainable.

Hopefully this has given you some insight into the issues.

If you provide concrete specs we can work thru specific values for your case.

It‘s possible to improve performance over a single RC by using cascaded RC stages.

One cannot get as good performance in a pure multi-stage RC passive filter as can be obtained from active filters,

but performance may nonetheless be better than with a single stage.

Unfortunately, I don‘t know any particular good methods for computing optimal RC values.

Another thing to note is that while pulse-width modulation is the most common form of duty-cycle modulation, it is not the only one.

One simple approach which can be very useful in cases where the target output voltage won‘t be changing too often,

and where the output is more likely to be near the center of the range than at the edges,

is to generate a set of signals by computing (current counter value "and not" previous counter value),

and ANDing that signal with the bits of desired data value,

in reverse order (so that the MSB of the data value gets AND‘ed with the xor of the present counter LSB and the previous one).

Using such an approach with e.g. six-bit duty cycle modulation would mean a 32/64 duty cycle wave

will be represented by a frequency of half the PWM clock, rather than square wave with a frequency 1/64 of the PWM clock.

A 33/64 duty cycle would be represented mostly by a frequency of half the PWM clock, but with some extra high pulses thrown in.

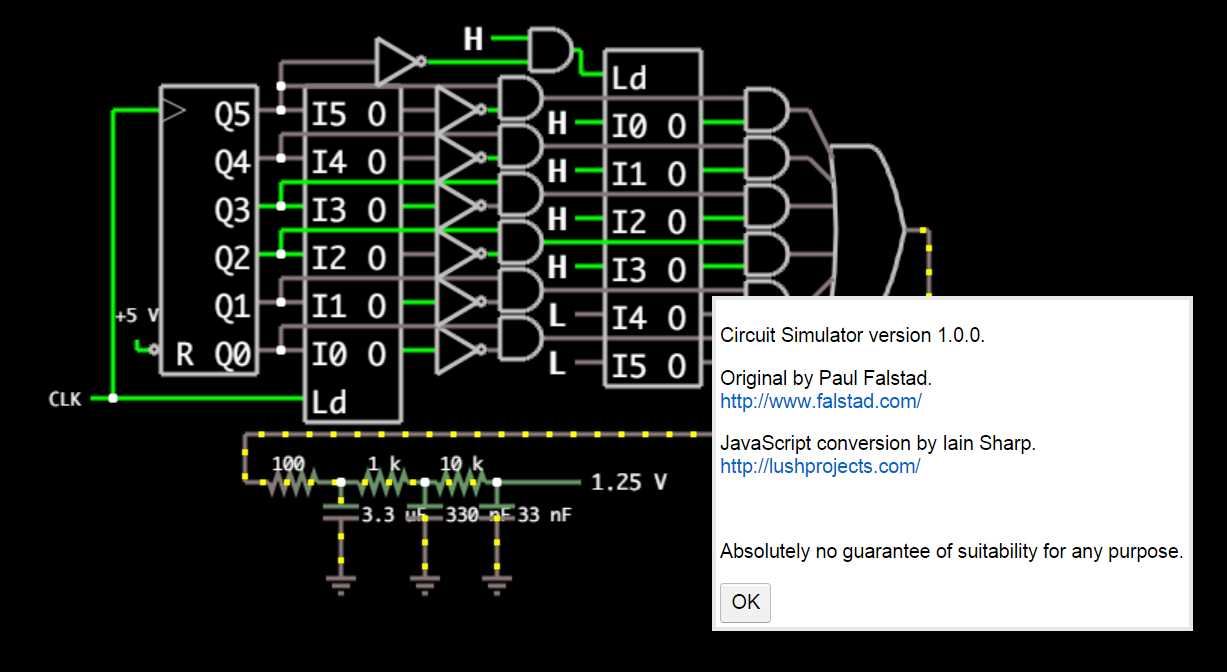

Here‘s a demo of what I‘m talking about.

All great answers given so far, well written and relevant,

but often the best answer needs a better question.

When you consider "best amount of RC?", what assumptions need to be considered for any design;

What is impedance of filter relative to impedance of source and load?

If not critical, choose R in between source and load. But say if CMOS driver is a value 10~100 Ω and say load is 100KΩ, but you want 0.3% accuracy on DC loss, then choose R << 0.3% of R-load, or as I call it "impedance ratio method" for loading considerations so here R < 0.003 * 1e5 = 300Ω. This choice of R is not critical, but you must take care not to load filter, so you may choose by impedance ratios for quick calculation on DC loss and AC rejection.

Assuming you know impedance of a capacitor impedance ratio criteria is a simple solution. Otherwise to find an impedance in the middle of source and load consider one method Rf = √(Rs*Rl), where Rf is filter RC value for source, Rs and load Rl as one method for middle range.

The nice thing about design, is depending on your criteria, there are often multiple "best" answers for RC value. :)

How determine the RC time constant in PWM DAC low-pass filter?

标签:

原文地址:http://www.cnblogs.com/shangdawei/p/4821764.html