标签:

定义一个指令集体系结构,例如Y86,包括定义各种状态元素、指令集和他们的编码、一组变成规范和异常事件处理。

①程序员可见的状态:Y86中每条指令都会读取或修改处理器状态的某些部分。这里的“程序员”既可以是用汇编代码写程序的人,也可以是产生机器代码的编译器。

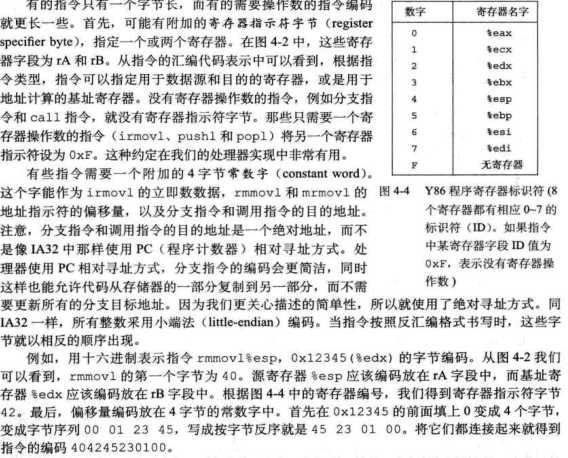

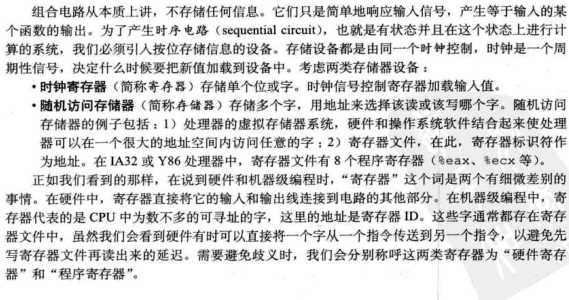

Y86的处理器状态类似IA32。有8个程序寄存器:%eax,%ecx,%edx,%ebx,%esi,%esp和%ebp。处理器的每个程序寄存器存储一个字。

②存储器,从概念上来说是一个很大的字节数组,保存着程序和数据。Y86程序用虚拟地址来引用存储器位置。硬件和操作系统软件联合起来将虚拟地址翻译成实际或物理地址,指明数据实际保存在存储器那个地方。

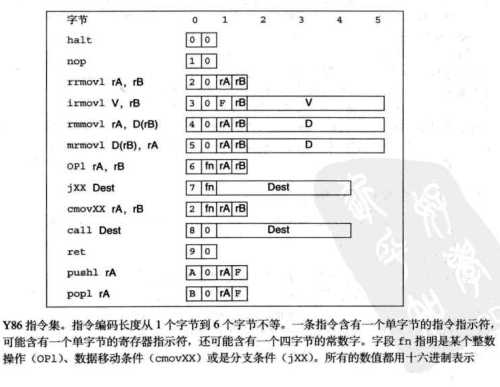

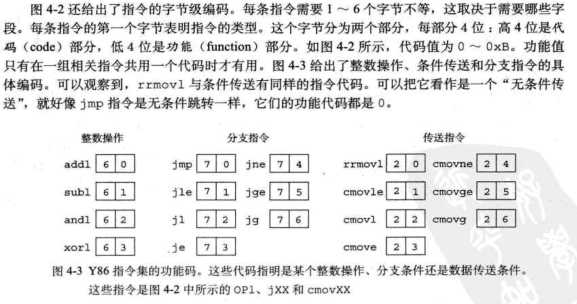

Y86指令集基本上是IA32指令集的一个子集。它只包括四字节整数操作、寻址方式比较少、操作也较少。因为只有四字节数据,所以称之为“字”不会有任何歧义。

左边是指令的汇编码表示,右边是字节编码。汇编码格式类似于IA32的ATT格式。

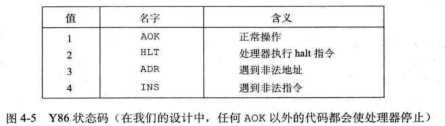

对于Y86,当遇到这些异常的时候,我们就简单的让处理器停业执行指令。

在更完整的设计中,处理器通常会调用一个异常处理程序,这个过程被指定用来处理遇到的某种类型的异常。

组合电路:讲很多的逻辑门组成一个网,就能构成计算块。

构建这些网有两条限制:①两个或多个逻辑门的输出不能连接在一起,否则他们可能会使线上的信号矛盾,可能会导致一个不合法的电压或电器故障。

②这个网必须是无环的。

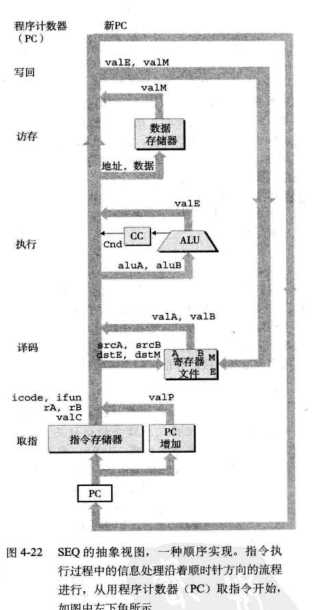

下面是关于各个阶段以及各阶段内执行操作的简略描述:

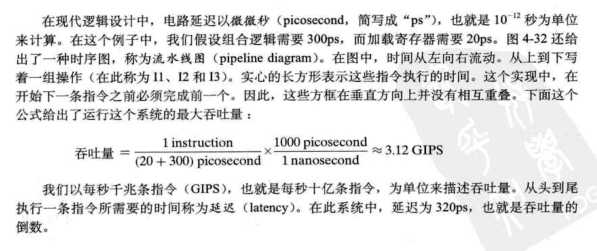

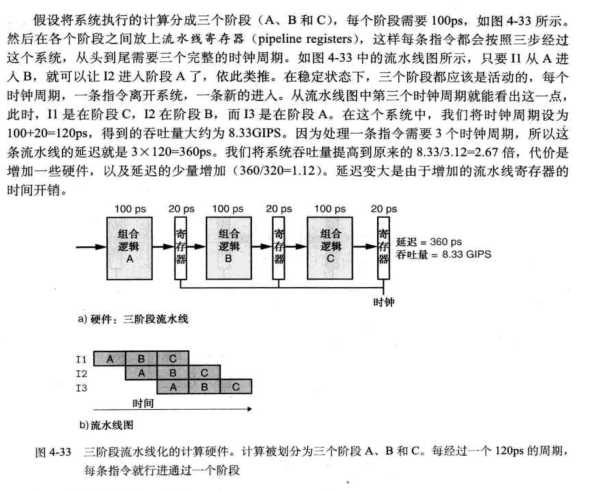

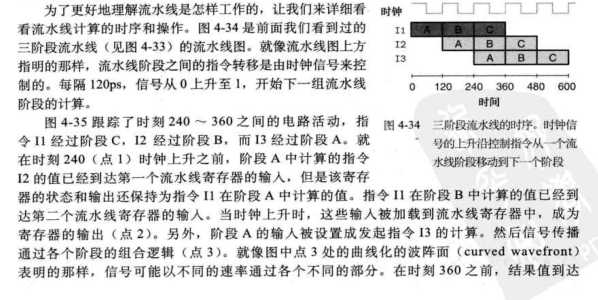

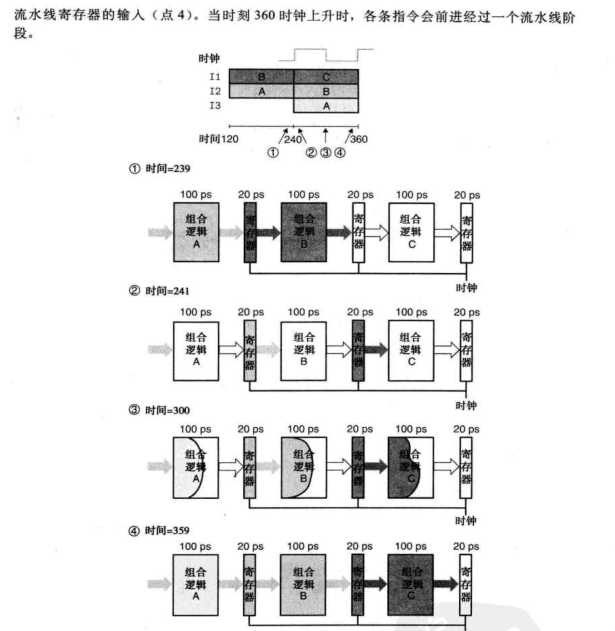

流水线化的一个重要特性就是增加了系统的吞吐量,也就是单位时间内服务的顾客总数,不过他也会轻微地增加延迟,也就是服务一个客户所需要的时间。

标签:

原文地址:http://www.cnblogs.com/disturbia/p/4888067.html