标签:

1、什么是流水线设计技术?

答:所谓流水线设计实际上是把规模较大、层次较多的组合逻辑电路分为几个级,在每一级插入寄存器组并暂存数据。

K级就是有K个寄存器组,从上到下没有反馈电路。

*********************************************************************************

2、流水线设计的深入讲解:

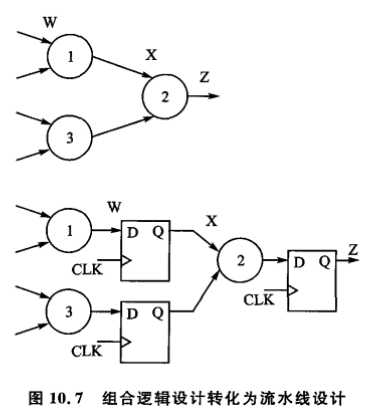

如图10.7 组合逻辑设计 ——> 流水线设计

纯组合逻辑需要时间:[max(T1,T3)+T2]

流水线设计首次需要时间:[max(T1,T3)+T2]+2TCO

流水线设计稳定后需要的时间:[ max( max(T1,T3)+TCO, (T2+TCO)) ]

流水线设计在首次虽然需要两个时钟周期来获取数据,但是在随后,只需要一个时钟周期就可以获取数据。

流水线设计能够提高吞吐量(throughput)。

流水线设计在性能上的提高是以消耗较多寄存器组的资源为代价的。

流水线设计对于简单的组合逻辑来说流水线设计占用资源较少,一般FPGA完全满足要求。

流水线设计对于复杂的组合逻辑设计来说,这是必须的,因为为了保证中间计算结果都在同一时钟周期内得到,必须在各级之间加入更多的寄存器。

********************************************************************

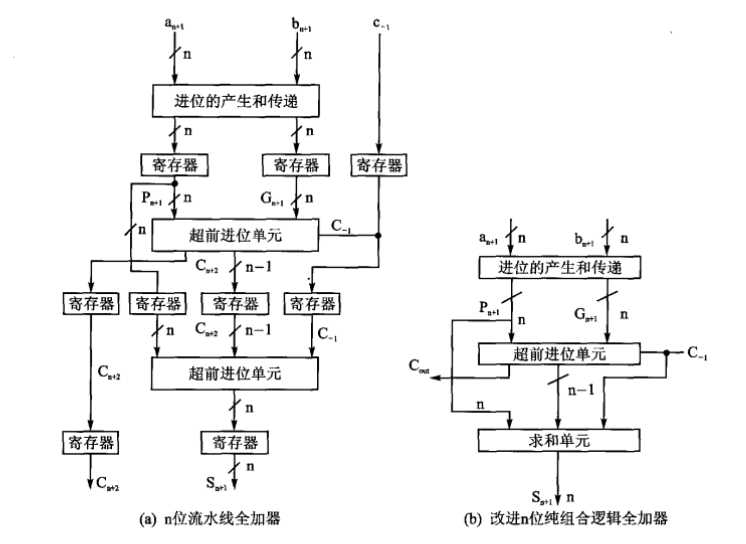

3、流水线加法器与组合逻辑加法器

由原理图可以看出,基本上每一个线上都加上了寄存器,但是我们最后的输出就是在一次次的clk信号到来时输出。保证了运行的连续性。

虽然逻辑门增加了,但是吞吐量和速度增加了。

*********************************************************************

4、流水线乘法器和组合逻辑乘法器

虽然看不懂书本上讲的什么,但是我们从结果中可以看到,流水线乘法器要比组合逻辑乘法器运行起来要快得多,可是它也占用了大量的资源。

正所谓消耗资源换取速度。。。。。。

***************************************************************************

made by qidaiYMM, your comment is appreciated.

email:1519882610@qq.com

标签:

原文地址:http://www.cnblogs.com/qidaiymm/p/4888173.html