标签:

引用自夏宇闻教授

是指表示状态的寄存器组的值只能在唯一确定的触发条件发生改变。

只能由时钟的正跳变沿或者负跳变沿触发的状态机就是一例,always@(posedge clk)。

同步时序逻辑比异步时序逻辑稳定简单好多,由此我们有一个规定:用verilog来设计可综合的状态机必须使用同步时序逻辑。

是指触发条件有多个控制因素组成,任何一个因素的跳变都可以引起触发。寄存器组的时钟输入端不是都连接在同一个时钟信号上。

例如用一个触发器的输出连接到另外一个触发器的时钟端去触发的就是异步时序逻辑。

1、因为异步时序逻辑的触发条件很随意,任何时刻都有可能发生

2、许多综合器不支持异步时序逻辑的综合

3、异步时序很难控制由组合逻辑和延迟产生的冒险和竞争。

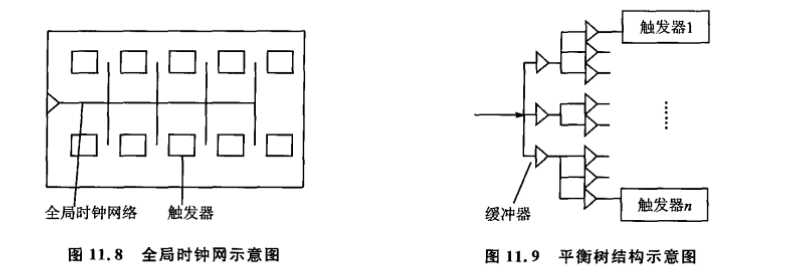

1)全局网络布线,如图

2)采用平衡树,并在每一级假如缓冲器,如图

3)后仿真时,降低时钟频率

made by qidaiYMM , your comment is appreciated.

email:1519882610@qq.com

标签:

原文地址:http://www.cnblogs.com/qidaiymm/p/4889540.html