标签:

ISA:一个处理器支持的指令和指令的字节级编码——指令集体系结构

ISA在编译器编写者和处理器设计人员之间提供了一个概念抽象层 与IA32相比Y86指令集的数据类型、指令和寻址方式都要少一些,它的字节级编码比较简单,不过它仍然足够完整

定义一个指令集体系结构,暴扣定义各种状态元素、指令集和它们的编码、一组编程规范和异常事件处理

1.程序员可见的状态

程序员可见状态:Y86程序中的每条指令都会读取或修改处理器状态的某些部分

Y86的处理器状态类似与IA32可以访问和修改程序寄存器、条件码、程序计数器(PC)和存储器

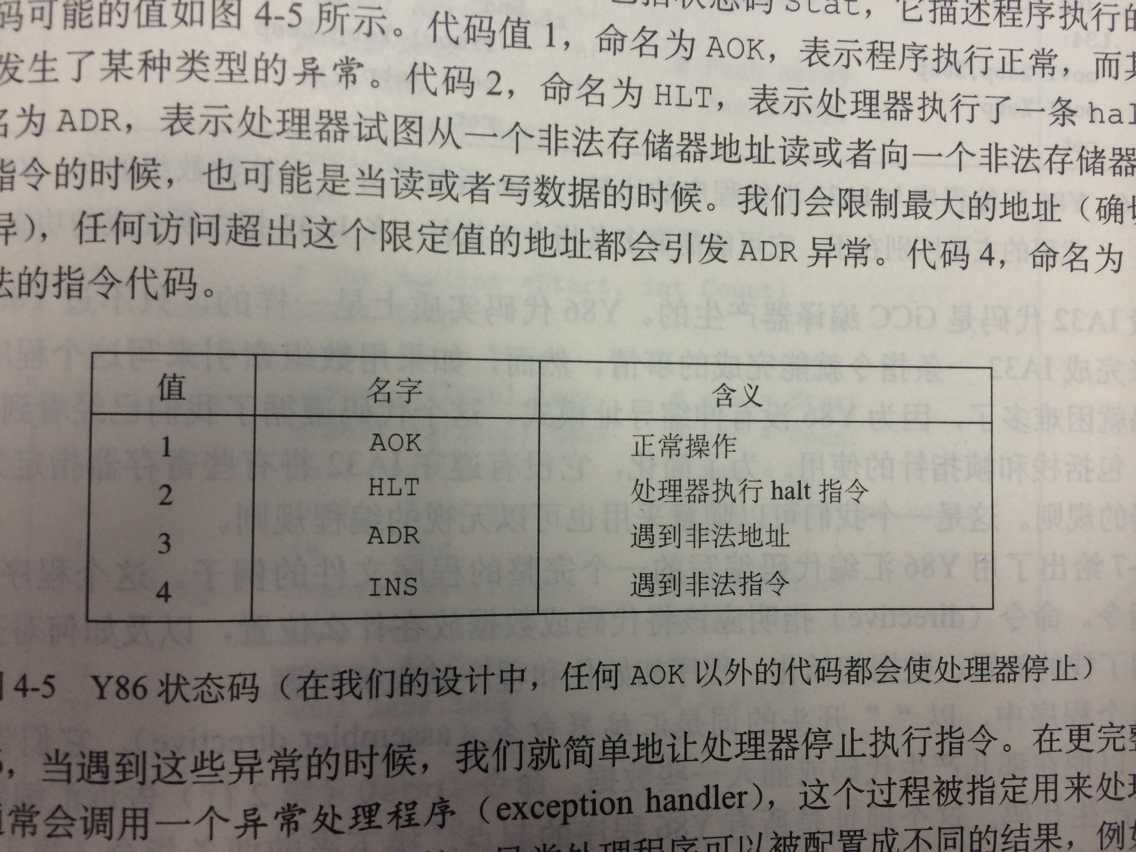

- 程序寄存器:%eax、%ecx、%edx、%ebx、%esi、 %edi、%esp和%ebp - 条件码:ZF、SF、OF,一位条件码,保存最近的算术 或 逻辑指令所造成的影响的信息 - 程序计数器:存放当前正在执行的指令的地址。 - 存储器:很大的字节数组,保存着程序和数据 - 状态码:指明程序是否运行正常,或者发生了某个特殊事件 2.Y86指令

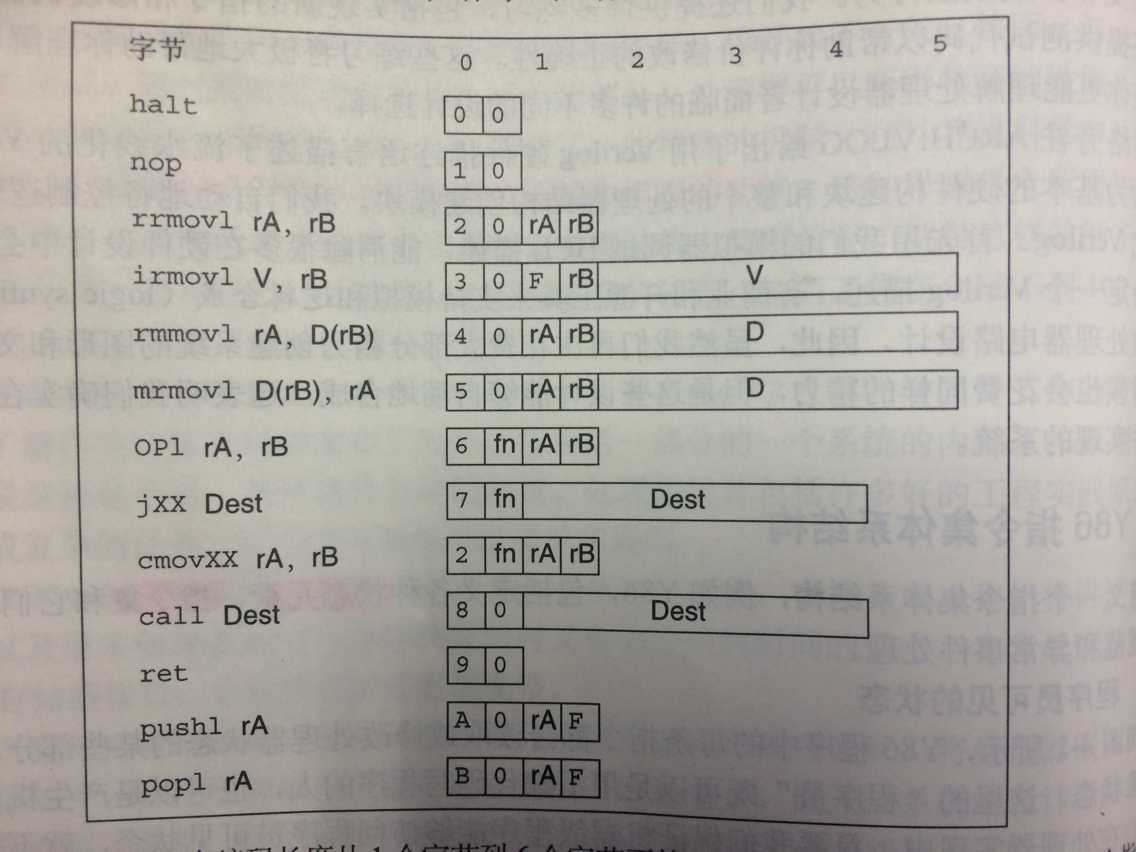

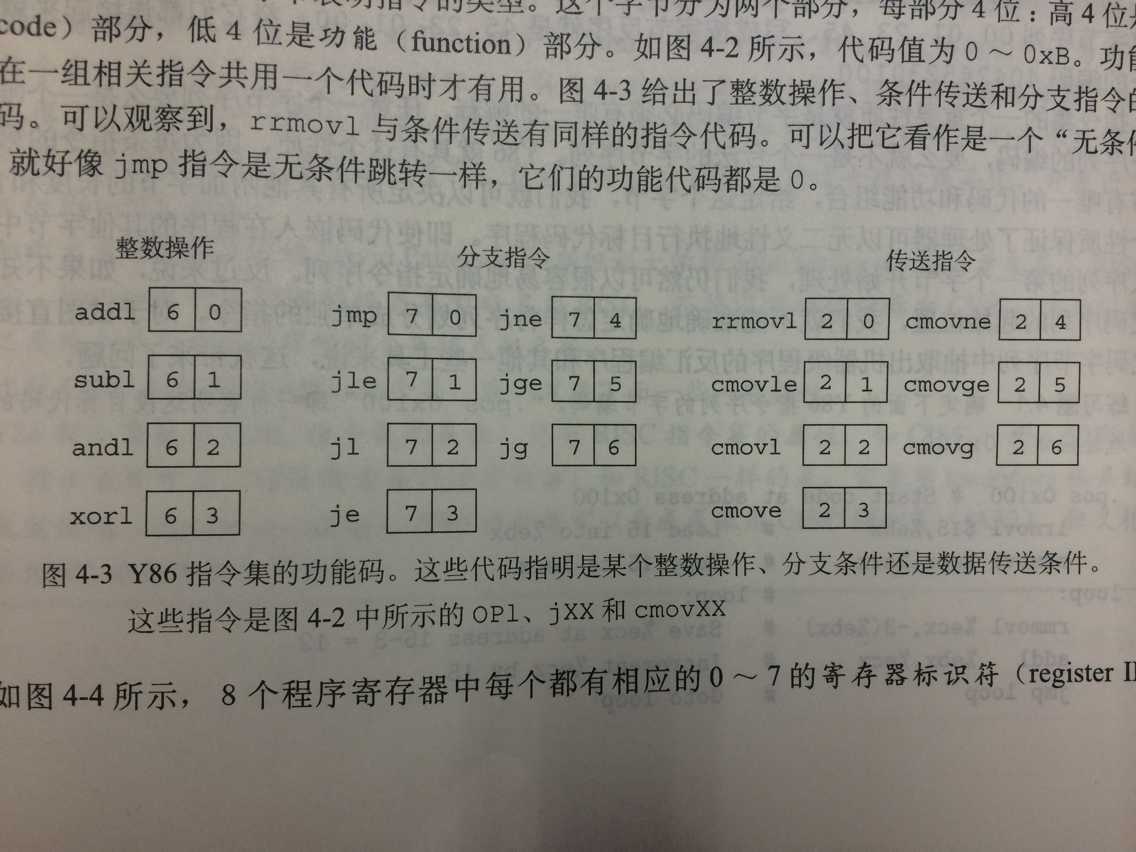

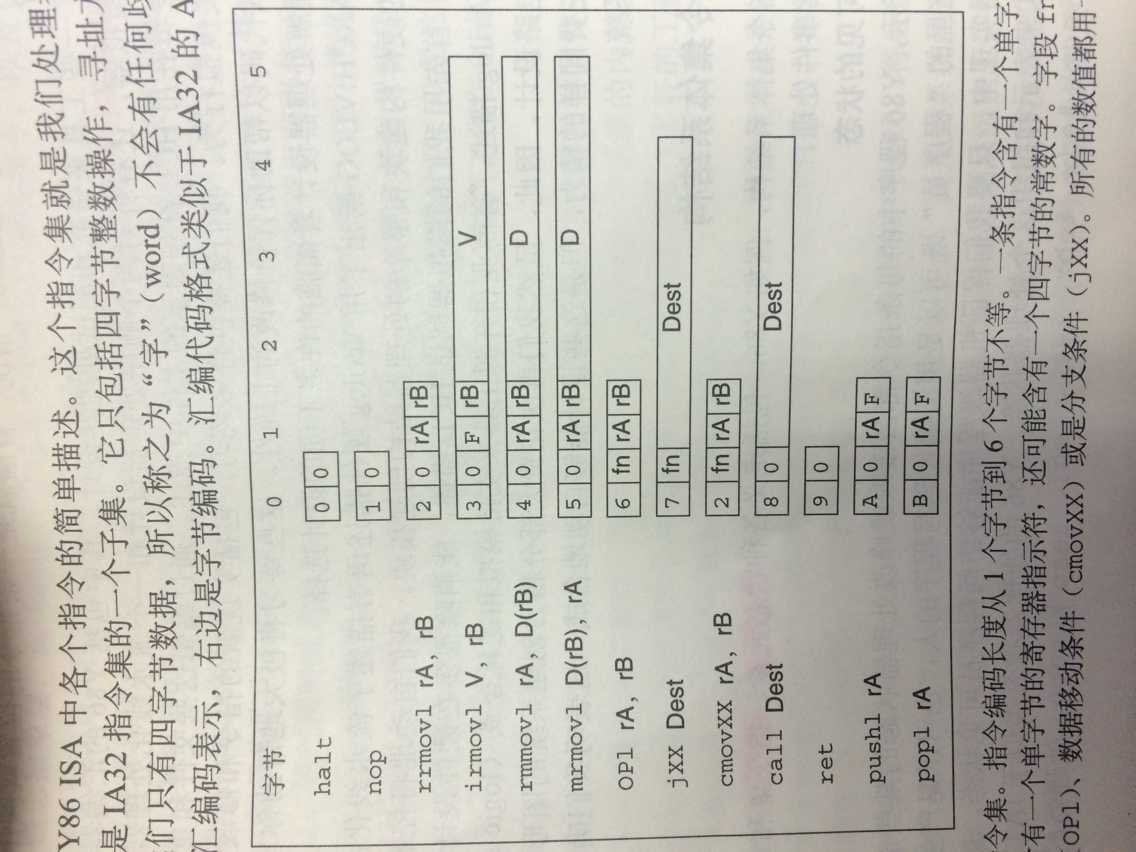

3.指令编码

每条指令的第一个字节表明指令的类型。这个字节分为两个部分, 每部分4位:高4位是代码部分,低4位是功能部分。功能值只有在一组相关指令共用一个代码时才有用。

8个程序寄存器各自有相应0-7的寄存器标识符。当需要指明不应访问任何寄存器时,有ID值0xF表示。

4.Y86异常

数字系统三部分组成:组合逻辑、存储器元素、时钟信号。 HCL:硬件控制语言,描述不同处理器设计的控制逻辑。 1.逻辑门

AND:&& OR:|| NOT:! 每个门产生的输出等于他输入的某个布尔函数 2.组合电路和HCL布尔表达式 组合逻辑电路和c语言中逻辑表达式都是用布尔操作来对输入进行计算的函数。 区别:

C的逻辑表达式可能被部分求值(第一个参数就能确定结果的就不会对第二个求值)

两个限制:1.两个及以上逻辑门的输出不能连接在一起(会产 生信号矛盾)。 2.网必须是无环的,不可以有路径经一系列门而形 成回路。 3.字级的组合电路和HCL整数表达式

同C语言的switch语句不同,我们不要求不同的选择表达式之间互斥。这些选择表达式顺序求值,且第一个求值为1的情况被选中

通用格式: [ select_1 :expr_1 select_2 :expr_2 ...... ...... select_k :expr_k ] 4.集合关系

bool s1= code==2||code==3; 等价于 bool s1 = code in {2,3}; 表示当code在集合{2,3}中s1为1。 5.存储器和时钟

时序电路:有状态,且在这个状态上进行计算的系统。 时序电路的两类存储器设备

1.将处理组织成阶段

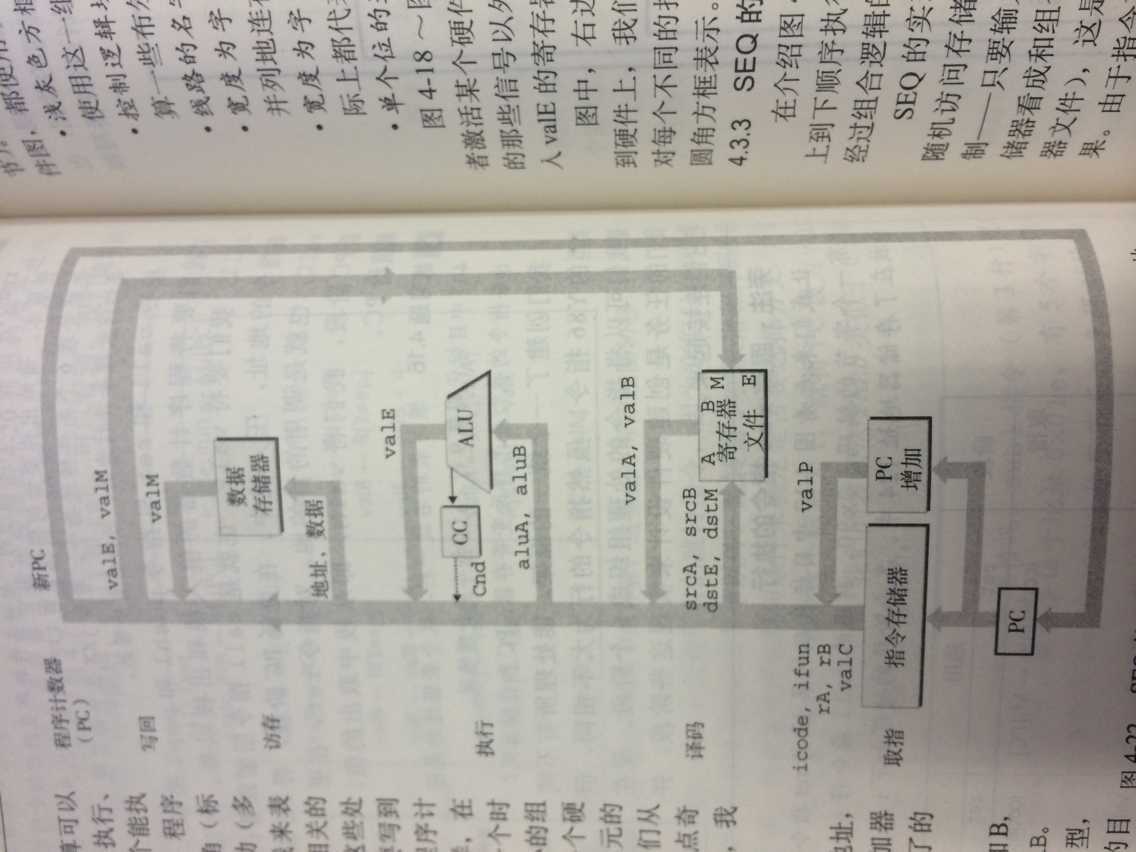

2.SEQ硬件结构

2.SEQ硬件结构

3.SEQ时序

4.SEQ阶段的实现

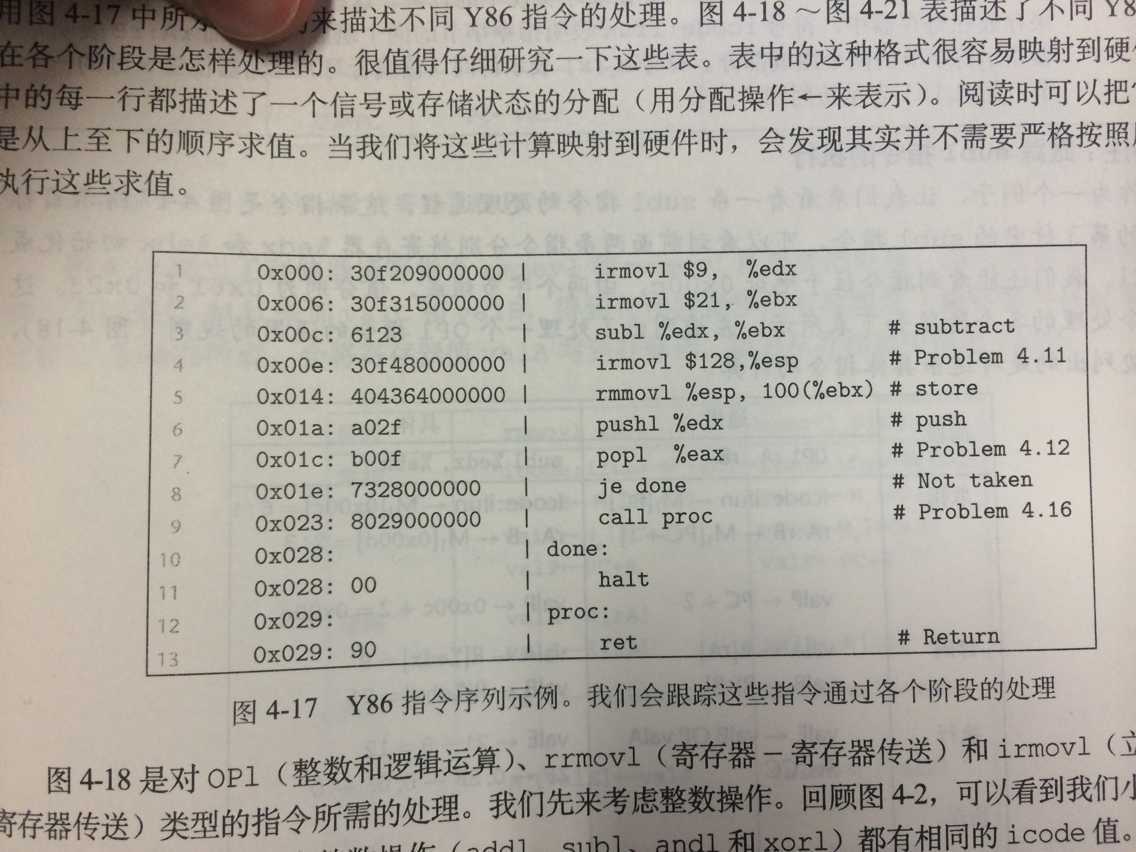

取指阶段

以PC为第一个字节的地址,一次读6个字节。

icode 控制逻辑块计算指令 ifun 功能码 三个一位的信号(根据icode值计算)

instr_valid 发现不合法的指令 need_regids 包含寄存器指示符字节吗 need_valC 包括常数字吗 后五个字节是寄存器指示符字节和常数字的组合编码。 译码和写回阶段

都需要访问寄存器文件,根据四个端口的情况,判断应该读哪个寄存器产生信号valA、valB。 寄存器文件,支持同时进行两个读和两个写,每个端口有一个地址连接(寄存器ID)和一个数据连接(32根线路),既可以作为寄存器文件的输出字,又可以作为他的输入字。 执行阶段

包括算数/逻辑单元(ALU),输出为valE信号。

ALU通常作为加法器使用 包括条件码寄存器

每次运行产生: 零、符号、溢出、产生信号set_cc 访存阶段

读或者写程序数据。 两个数据块产生存储器地址和存储器输入证据的值,两个产生控制信号表明应该是读还是写。当执行读操作时,数据存储器产生valM。 根据icode,imemerror,instrvalid,dmem_error,从指令执行的结果计算状态码Stat。

更新PC阶段

产生程序计数器的新值,依据指令的类型和是否要选择分支,新的PC可能是valC、valM或者valP。

不知道如何确定Y86指令序列的字节编码

解决方法,通过研究练习题4.1、4.2从答案入手并反复研读书中内容后领悟。

[1]《深入理解计算机系统》

[2]http://www.cnblogs.com/hyq20135317/p/4888744.html

[3]http://www.cnblogs.com/zzzz5/p/4889360.html

[4]百度百科

20135304刘世鹏——信息安全系统设计基础第五周学习总结

标签:

原文地址:http://www.cnblogs.com/L20135304/p/4890638.html