标签:

第四章,处理器体系结构

ISA:一个处理器支持的指令和指令的字节级编码,成为指令集体系结构。

不同的处理器家族都有不同的ISA。例如:Intel IA32、IBM Freescale PowerPC和ARM处理器家族。

本章将简要介绍处理器硬件的设计。

4.1Y86指令集体系结构

定义一个指令集体系结构,包括定义各种状态元素、指令集和他们的编码一组编程规范和异常事件的处理。

程序员是可以是用汇编代码写程序的人,也可以是产生机器级代码的编译器。

4.1.1程序员可见的状态

Y86的处理器状态类似于IA32。

八个程序寄存器:%eax、%ecx、%edx、%ebx、%esi、%edi、%esp和%ebp。

三个一位的条件码:ZF、SF和OF。

存储器:一个很大的字节数组,保存着程序和数据。

Y86程序用虚拟地址来引用存储器位置。

硬件和操作系统软件联合起来将虚拟地址翻译成实际或物理地址。

4.1.2 Y86指令

Y86指令集基本上是IA32指令集的一个子集。

halt

nop

rrmovl rA,rB

irmovl V,rB

rmmovl rA,D(rB)

mrmovl D(rB),rA

OPl rA,rB

jXX Dest

cmovXX rA,rB

call Dest

ret

pushl rA

popl rA

分别指明源和目的的格式。

源可以是立即数(i)、寄存器(r)或者存储器(m),指令的第一个字母就指明了源的类型。

目的类型可以是寄存器(r)或者存储器(m),指令的第二个字母就指明了目的类型。

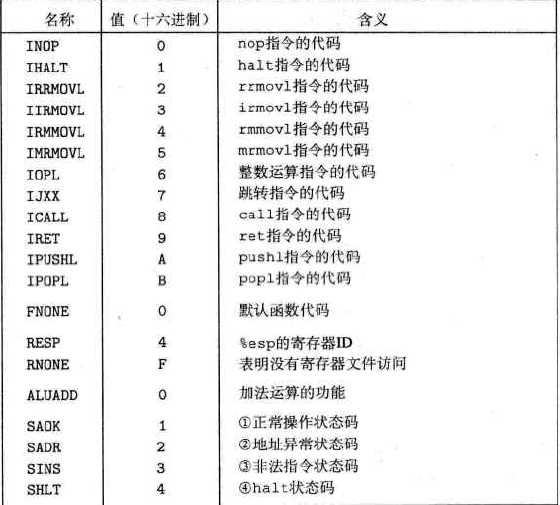

4.1.3 指令编码

每条指令需要1-6个字节不等,这取决于需要哪些字段。

一个字节分为两部分,每部分四位:高四位是代码部分,低四位是功能部分。

4.1.4 Y86异常

对于Y86,处理器通常会调用一个异常处理程序。

4.1.5 Y86程序

Y86代码与IA32代码的主要区别在于,需要更多条指令来执行一条IA32指令所完成的功能。

4.2 逻辑设计和硬件控制语言 HCL

现代逻辑设计,HDL是一种文本表示,看上去和编程语言类似,但是是用来描述硬件结构而不是程序行为的。

最常用的语言是Verilog,语法类似于C;另一种是VHDL,类似于ADa。

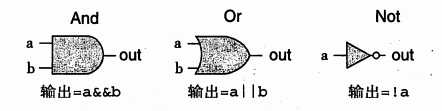

4.2.1 逻辑门

AND &&;OR ||;NOT !。

4.2.2组合电路和HCL布尔表达式

将很多逻辑门组合成一个网,就能构建计算块,成为组合电路。

构建限制:1,两个或多个逻辑门的输出不能连在一起

2,这个网必须是无环的。

4.2.3 字级的组合电路和HCL整数表达式

4.2.4 集合关系

4.2.5 存储器和时钟

时钟寄存器

随机访问存储器

4.3 Y86的顺序实现

4.3.1 将处理组织成阶段

取指

译码

执行

访存

写回

更新PC

4.3.2 SEQ硬件结构

同各个阶段相关的硬件单元负责执行这些处理。

4.3.3 SEQ时序

时钟寄存器

随机访问存储器

4.3.4 SEQ阶段的实现

取指阶段

译码和写回阶段

执行阶段

访存阶段

更新PC阶段

第四章参考资料 《深入了解计算机系统》 闫佳歆同学的博客

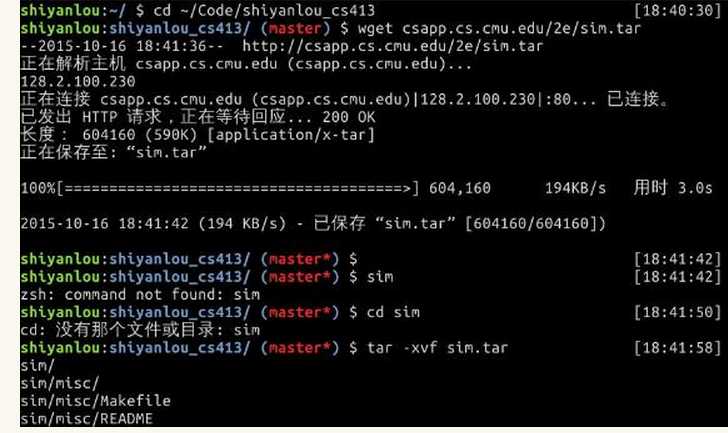

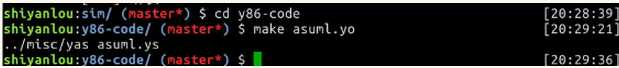

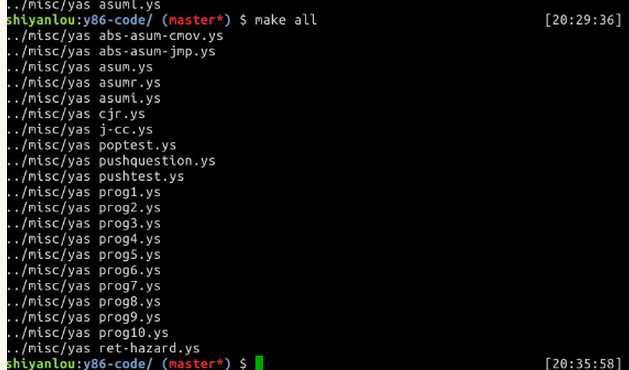

实验

标签:

原文地址:http://www.cnblogs.com/20135335hs/p/4890643.html