标签:

K9F2G08U0A是三星公司生产的总容量为256M的NandFlash,常用于手持设备等消费电子产品。还是那句话,搞底层就得会看datasheet,我们就从它的datasheet看起。

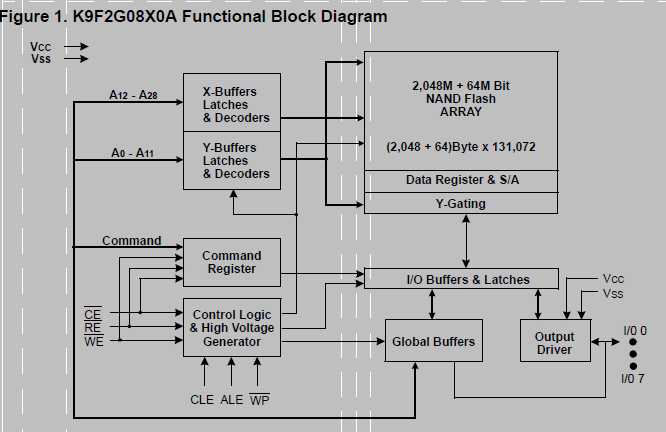

这就是 K9F2G08U0A的内部结构,具体的各个部件的介绍,就不详细介绍了,想了解的话可以参考伟东山的《嵌入式linux应用开发完全手册》。

现在就看一下重点的,NandFlash的存储单元的组织结构,K9F2G08U0A的存储单元的组织结构如下:

结合上面的图,我们现在来分析一下:

NandFlash的存储单元是由Block组成的,Block又是由Page组成的,数据就是存储在Page上。

K9F2G08U0A的总容量是256M,由图可以看出,它一共有2048块,每一块有64页,每一页有(2K+64)Bytes。每一页又分为main区和spare区,2K就是指main区,64就是指spare区。

2K是指每一页上存放数据的有效空间,64是指每一页附加的空间,它不能用来存放我们写入的数据,它主要是用来存放ECC校验和坏块标记的信息数据。

还有一个比较重要的知识就是对NandFlash的访问,你不会访问它,那你肯定不会用它!

首先要明白NandFlash是以页(Page)为最小单位进行读写的,以块(Block)为最小单位进行擦除的,也就是说当我们给定了读取的起始位置后,读操作将从该位置开始,连续读取到本Page的最后一个 Byte为止(可以包括Spare Field)。

在弄清楚怎么读写NandFlash之前,还有一个准备工作要做,那就是我们要告诉NandFlash,我要读写哪个地方的数据,如果我们不告诉它地址,那它就不知道我们到读哪些数据。那如何计算我们要传入的地址呢?以一个例子来说明

以K9F2G08U0A为例,此nand flash,一共有2048个块,每个块内有64页,每个页是2K+64 Bytes,假设,我们要访问其中的第1500个块中的第25页中的1208字节处的地址,此时,我们就要先把具体的地址算出来:

物理地址=块大小×块号+页大小×页号+页内地址=1500×128K+25×2K+1208=0xBB8CCB8(196660408),接下来,我们就看看,怎么才能把这个实际的物理地址,转化为nand Flash所要求的格式。在解释地址组成之前,先要来看看其datasheet中关于地址周期的介绍:

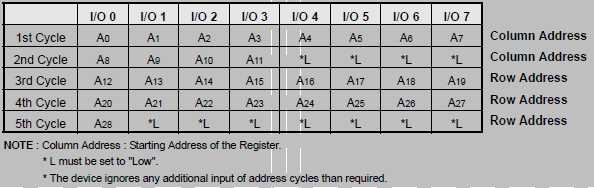

由上图可以看出,K9F2G08U0A是用5个周期来实现,由于NAND flash以页为单位读写数据,而以块为单位擦除数据。按照这样的组织方式可以形成所谓的三类地址:

Column Address:Starting Address of the Register. 翻成中文为列地址,地址的低8位 ,即页内偏移地址

Page Address :页地址

Block Address :块地址

我们知道K9F2G08U0A的每一页有(2K+64)=2112Byte,2112byte 需要12bit来表示,对于2112byte系列的NAND,这2112byte被分成1st half Page Register和2nd half Page Register,各自的访问由地址指针命令来选择,A[11:0]就是所谓的column address(列地址),在进行擦除操作时不需要它,因为以块为单位擦除。64个page需要6bit来表示,占用A[17:12],即该page在块内的相对地址,也就是确定位于哪一页。A11这一位地址被用来设置2048byte的1st half page还是2nd half page,0表示1st,1表示2nd。Block的地址是由A18以上的bit来表示,也就是确定位于哪一块。用A[0:28]这29位,就可以将K9F2G08U0A这256M的数据存储空间全部访问到。

2的29次方是2GBit,256MByte=2GBit。

NAND Flash 的地址表示为: Block Address|Page Address in block|Column Address 地址传送顺序是Column Address,Page Address,Block Address。

由于地址只能在I/O[7:0]上传递,因此,必须采用移位的方式进行。 以K9F2G08U0A 为例:

第1 步是传递column address,就是NAND_ADDR[7:0],不需移位即可传递到I/O[7:0]上。

第2 步就是将NAND_ADDR 右移8位,将NAND_ADDR[11:8]传到I/O[7:0]上;

第3 步将NAND_ADDR[19:12]放到I/O上;

第4步需要将NAND_ADDR[27:20]放到I/O上;

第5步需要将 NAND_ADDR[28]放到I/O上;

因此,整个地址传递过程需要5步才能完成,即5-step addressing。 如果NAND Flash 的容量是32MB(256Mbit)以下,那么,block adress最高位只到bit24,因此寻址只需要3步。

简单解释完了地址组成,那么就很容易分析上面例子中的地址了:

0xBB8CCB8 = 00001011 1011 1000 1100 1100 1011 1000,分别分配到5个地址周期就是:

B B 8 C C B 8

第一个周期:A[0:7] 也就是B8

第二个周期:A[8:11] 取四位 1100, 再添4位0,也就是0000 1100 即0C

第三个周期:A[12:19] 取八位 1000 1100 即8C

第四个周期:A[20:27] 取八位 1011 1011 即BB

第五个周期:A[28] 取一位 0,补齐八位 即 0000 0000 也就是00

再往回分析,NandFlash收到前两个周期的地址A[0:11] 也就是0CB8,即 1100 1011 1000,分析:A[10:0]= 100 1011 1000=1208, 表示第1208个Byte

收到后三个周期后,即 0000 0000 1011 1011 1000 1100,A[16:11]=011001=25,表示第25页

0000 0000 1011 1011 100 处理后为 0101 1101 1100 =1500,表示第1500块

原文地址:http://blog.csdn.net/it_114/article/details/6258509

【转】深度分析NandFlash—物理结构及地址传送(以TQ2440开发板上的K9F2G08U0A为例)

标签:

原文地址:http://www.cnblogs.com/losing-1216/p/4891988.html