标签:

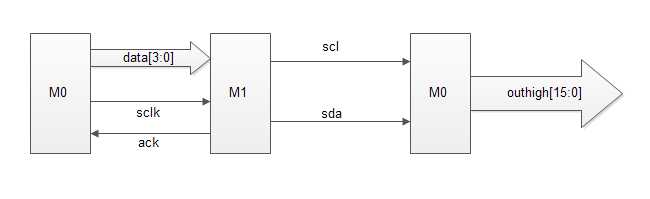

M0发送数据给M1,M1存取数据并赋给串行的sda,传给M0。

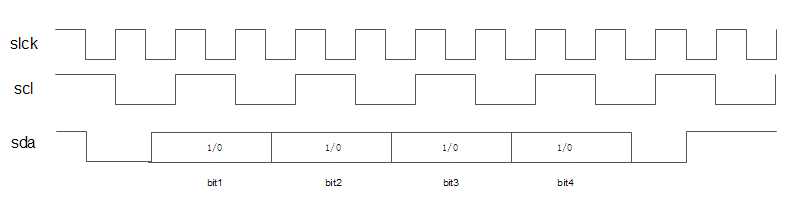

由时序图可以看出:说重点就是,这句最重点,理解哈,如果scl=1,那么sda由高变低时刻串行数据流开始;如果scl=1,那么sda由低变高时刻串行数据流结束,如果scl=0,那么我们的sda数据就可以变化了。

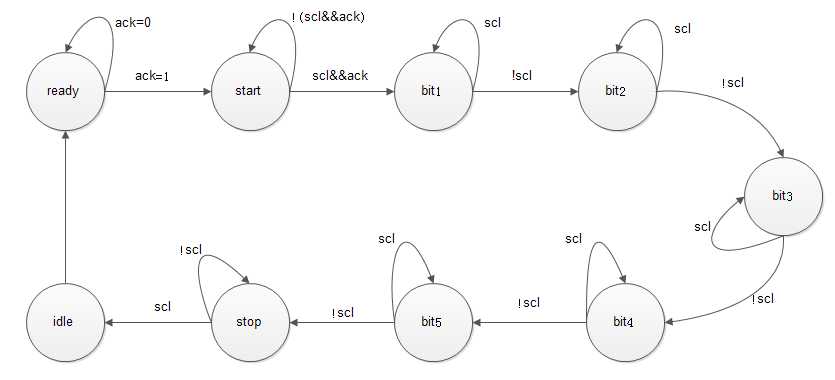

这是描述的时序状态图,我们可以看出,状态图就只是状态,这是时序的状态,注意clk的行为。从状态转换的条件来看,转换成功的关键在于看懂时序图,即:什么条件是代表开始,什么条件代表存数据??

1 //M1程序 2 module ptosda(rst,sclk,ack,scl,sda,data); 3 4 input sclk,rst;//外部时钟和复位 5 input[3:0] data;//外部数据 6 output ack;//请求 7 output scl;//m1的时钟 8 output sda;//M1数据线 9 10 reg scl,link_sda,ack,sdabuf;//总线开光,数据串行寄存变量 11 reg[3:0]databuf;//M1内部数据寄存 12 reg[7:0]state;//状态变量 13 14 //九种状态,怎么想的呢??? 15 parameter ready=8‘b0000_0000,//等待 16 start=8‘b0000_0001,//开始 17 bit1=8‘b0000_0010,//数据1 18 bit2=8‘b0000_0100,//数据2 19 bit3=8‘b0000_1000,//数据3 20 bit4=8‘b0001_0000,//数据4 21 bit5=8‘b0010_0000,//数据5 22 stop=8‘b0100_0000,//结束 23 idle=8‘b1000_0000;//空闲 24 25 always@(posedge sclk or negedge rst)//先把时钟设置好,就是这样设置的 26 begin 27 if(!rst) 28 scl<=1;//m1的scl时钟需要先是高位 29 else 30 scl<=~scl;//这里的数据是sclk的周期的二倍,把sclk的时钟信号传递给了scl,一种方法,5rf你懂的 31 end 32 33 always@(posedge ack)//再把数据接受好 34 databuf<=data;//只要请求到来,就会把数据传给databuf 35 36 //------主状态机:产生控制信号,根据databuf中的保存数据,按照协议产生sda串行信号 37 always@(negedge sclk or negedge rst)//这里是sclk 没有用scl用低电平触发 38 if(!rst) 39 begin 40 link_sda<=0;//断开总线 41 state<=ready;//进入准备状态 42 sdabuf<=1;//m1传输数据总线打开 43 ack<=0;//请求置0 44 end 45 else 46 begin 47 case(state) 48 ready: 49 if(ack)// 50 begin 51 link_sda<=1;//sda的总线打开 52 state<=start;//进入另外的开始阶段 53 end 54 else 55 begin 56 link_sda<=0;//sda 总线关闭 57 state<=ready; 58 ack<=1;//请求数据 59 end 60 start: 61 if(scl&&ack)//scl是高电平传状态,低电平传数据 62 begin 63 sdabuf<=0;//sdabuf寄存0 64 state<=bit1;//进入bit1状态 65 end 66 else 67 state<=start;//等待scl高电平到来 68 bit1: 69 if(!scl) 70 begin 71 sdabuf<=databuf[3];//sdabuf寄存高位数据 72 state<=bit2;//进入bit2状态 73 ack<=0;//关闭请求 74 end 75 else 76 state<=bit1;//等待scl变低电平,似乎是 77 bit2: 78 if(!scl) 79 begin 80 sdabuf<=databuf[2]; 81 state<=bit3; 82 end 83 else 84 state<=bit2; 85 bit3: 86 if(!scl) 87 begin 88 sdabuf<=databuf[1]; 89 state<=bit4; 90 end 91 else 92 state<=bit3; 93 bit4: 94 if(!scl) 95 begin 96 sdabuf<=databuf[0]; 97 state<=bit5; 98 end 99 else 100 state<=bit4; 101 102 bit5: 103 if(!scl) 104 begin 105 sdabuf<=0; 106 state<=stop; 107 end 108 else 109 state<=bit5; 110 stop: 111 if(scl) 112 begin 113 sdabuf<=1; 114 state<=idle; 115 end 116 else 117 state<=stop; 118 idle: 119 begin 120 link_sda<=0; 121 state<=ready; 122 end 123 default: 124 begin 125 link_sda<=0; 126 state<=1; 127 state<=ready; 128 end 129 endcase 130 131 end 132 133 endmodule

标签:

原文地址:http://www.cnblogs.com/qidaiymm/p/4906685.html