标签:

信号完整性仿真大多针对由芯片IO、传输线以及可能存在的接插件和分立元件所构成的信号网络系统,为了实现精确的仿真,仿真模型的精确性是首先需要保证的。一般情况下,Allegro PCB SI会执行传输线和分立元件的建模,而芯片IO和连接器的模型通常会由原厂提供。

当前业内常见的芯片IO模型有两种格式,IBIS模型和HSPICE模型;常见的连接器模型也是两种,SPICE (HSPICE)模型和S参数模型。Allegro PCB SI支持包括上述四种模型在内业界流行的仿真模型,但一般都需要转化为Cadence自己的DML(Device Modeling Library)后才能使用。

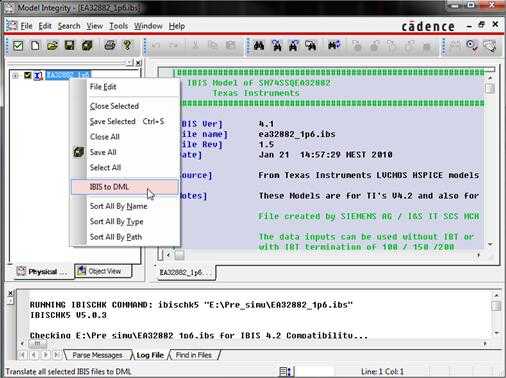

Allegro PCB SI在仿真时需要将仿真模型都转变成DML模型格式这一做法,区别于大多数EDA软件,这种做法可以说是有利有弊。弊,很明显,就是多一个额外的步骤,虽然这一步骤非常简便;利,则是有利于仿真库的管理,做到仿真库和原始模型文件的隔离,并且在文件格式转换的同时也执行了模型的校验。在大多数情况下,外部模型格式到Cadence DML模型格式的转换还是非常方便的,只需要用Cadence SPB系列工具包中的Model Integrity软件打开模型文件,然后点击转换到DML即可。

在本案例中,我们之前已经从Micron下载到寄存器和内存芯片的IBIS模型,可以有两种方法处理:

其一,在Model Integrity界面下或Allegro PCB SI界面下将IBIS模型转换成DML格式,供之后的仿真调用;

其二,从Cadence SPB 16.5版本开始,Allegro PCB SI名义上也直接支持IBIS模型,所以可以保留现有的两个IBIS文件不做转换,然后在之后的仿真中直接调用。之所以说是“名义上”,因为事实上Allegro PCB SI还是执行了转换,只是这个转换的过程在分配模型的同时一起执行了,没有摆在明面上。

我们先来看看如何使用Model Integrity转换IBIS模型。

图 6:Model Integrity界面

图 7:使用Model Integrity将IBIS文件转换至DML格式

不经转换直接调用IBIS的方式将在下面章节中介绍。

标签:

原文地址:http://www.cnblogs.com/yl103387239/p/4937685.html