标签:

一,UART

2,UART工作原理

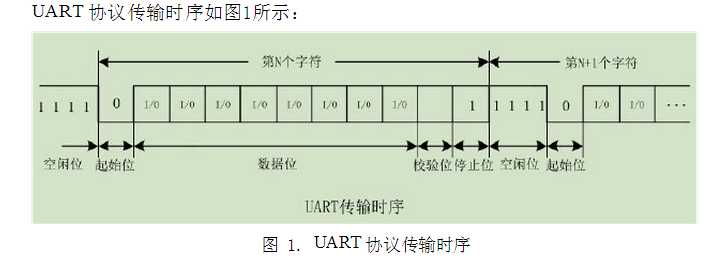

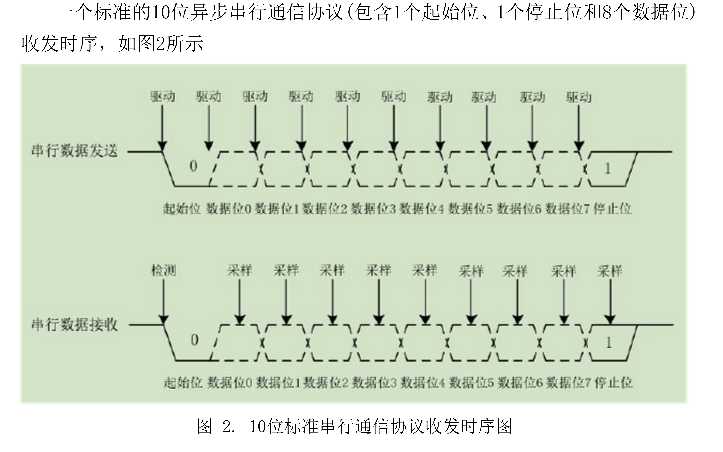

发送数据:空闲状态,线路处于高电位;当收到发送数据指令后,拉低线路一个数据位的时间T,接着数据按低位到高位依次发送,数据发送完毕后,接着发送奇偶校验位和停止位(停止位为高电位),一帧数据发送结束。

接受原理:空闲状态,线路处于高电位;当检测到线路的下降沿(线路电位由高电位变为低电位)时说明线路有数据传输,按照约定的波特率从低位到高位接收数据,数据接收完毕后,接着接收并比较奇偶校验位是否正确,如果正确则通知后续设备准备接收数据或存入缓存

为了能保证数据传输的正确性,UART采用16倍数据波特率的时钟进行采样。每个数据有16个时钟采样,取中间的采样值,以保证采样不会滑码或误码。一般UART一帧的数据位数为8,这样即使每个数据有一个时钟的误差,接收端也能正确地采样到数据

3、UART波特率发生器

波特率是衡量数据传输速率的指标,表示每秒传送数据的字符数,单位为Baud。UART的接收和发送是按照相同的波特率进行收发的。波特率发生器产生的时钟频率不是波特率时钟频率,而是波特率时钟频率的16倍,目的是为在接收时进行精确地采样,以提取出异步的串行数据。根据给定的晶振时钟和要求的波特率,可以算出波特率分频计数值。

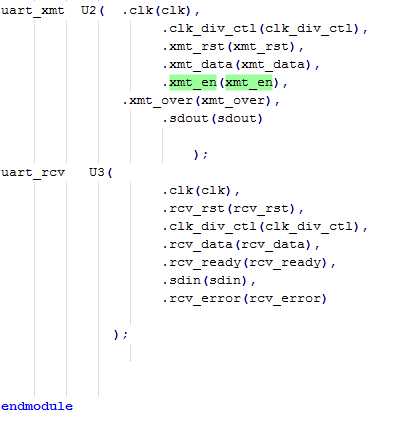

二,verilog设计

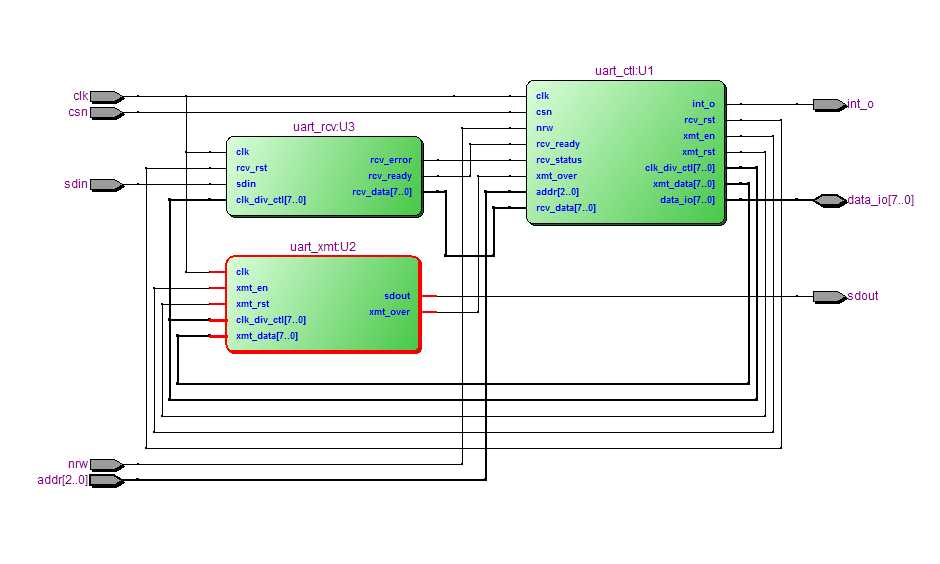

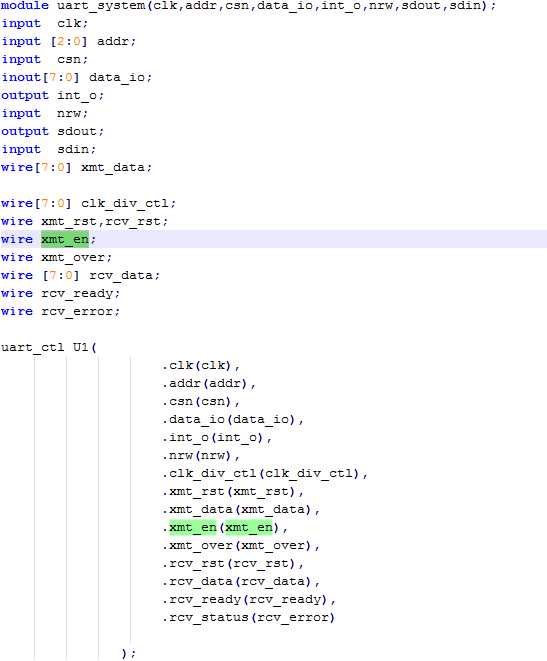

1, 顶层模块

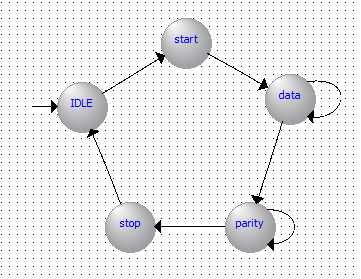

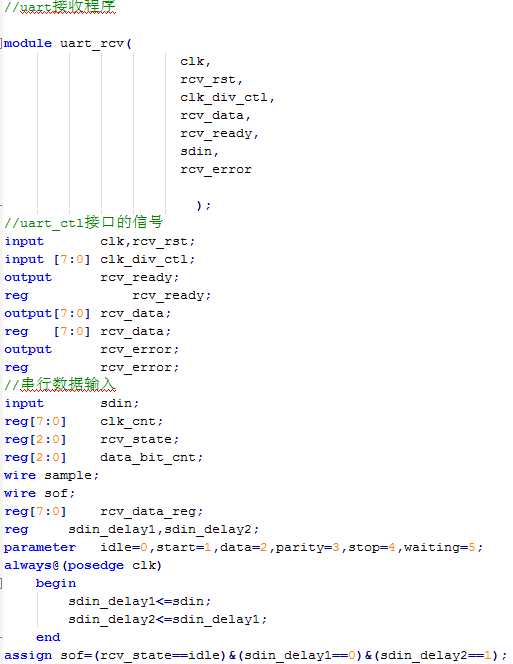

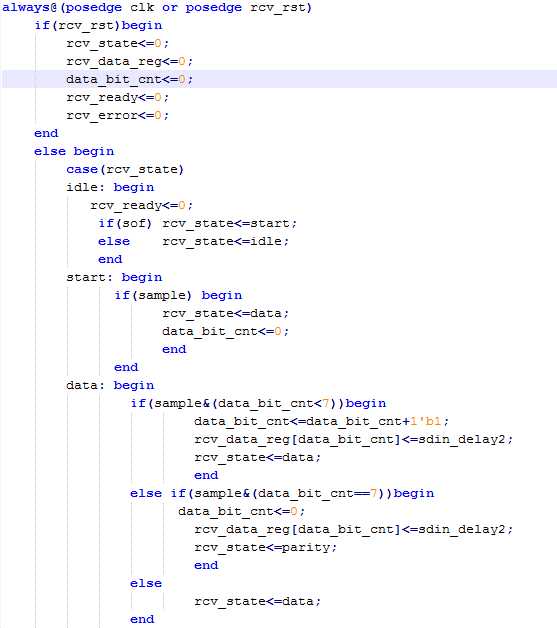

2,接受模块uart_rcv

状态转换图

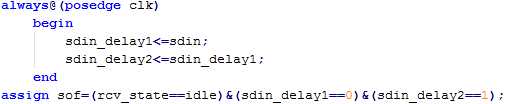

检测数据下降沿,线路有数据传输

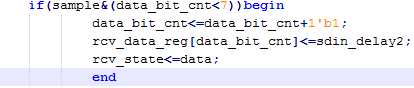

通过data_bit_cnt计数,实现对输入的串行数据进行并行转换

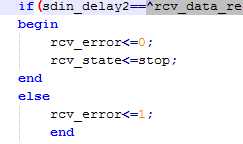

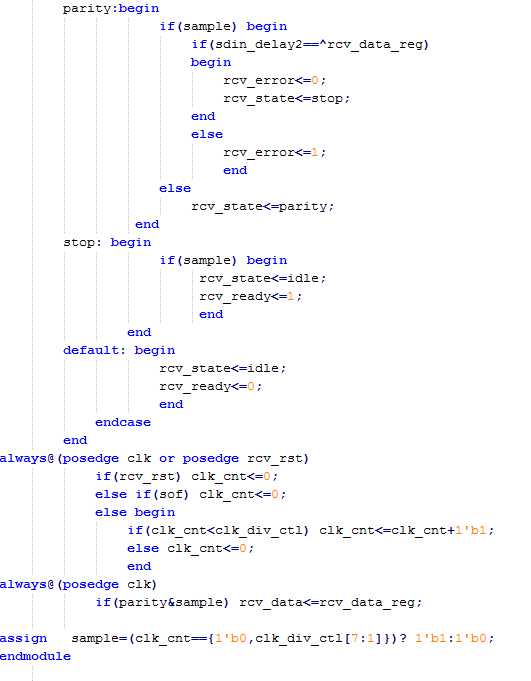

判断奇偶校验位是否正确

只要判断接受数据与^rcv_data_reg是否相同

注:^a操作就是将a中的每一位按位逐一进行异或,例如a=4‘b1010,则b=1^0^1^0=0,由此可以判断a中为1的位数是奇数还是偶数

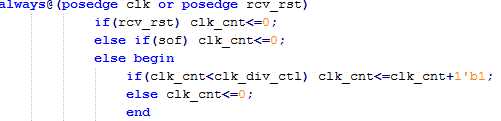

简易波特率发生模块

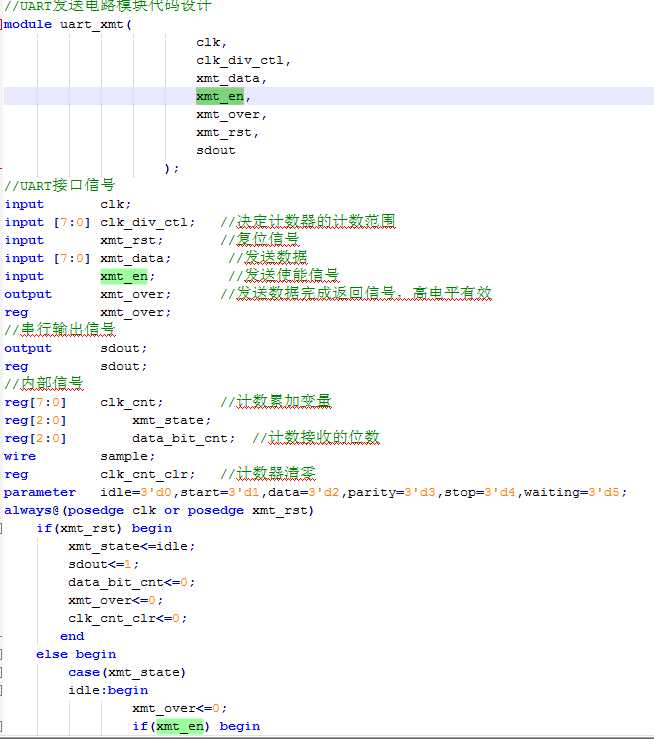

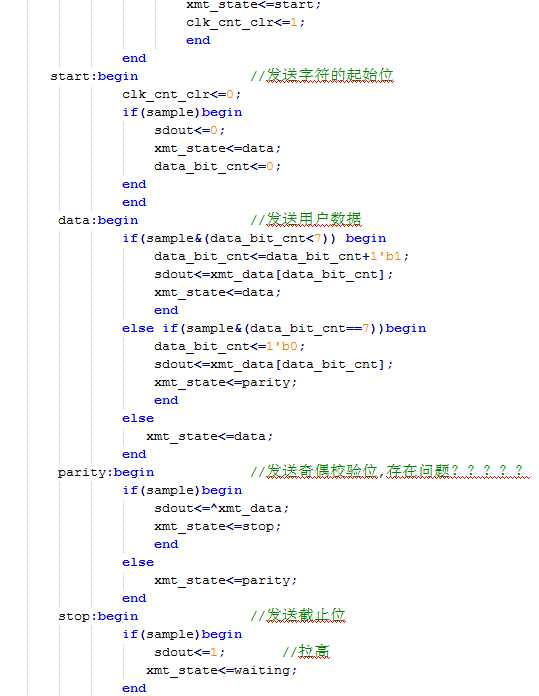

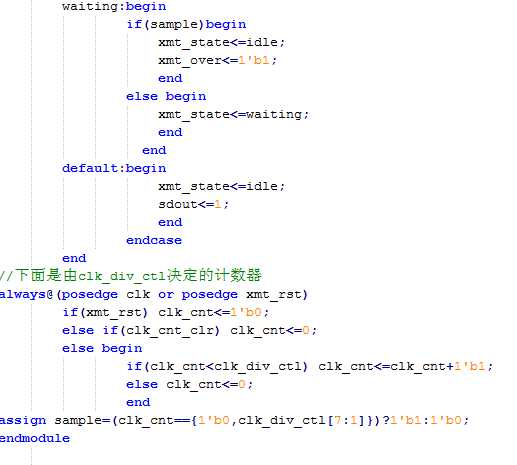

3,发送模块uart_xmt

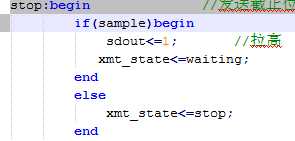

发送完奇偶校验位后需要拉高数据线

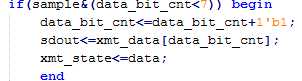

串并转换

基本原理与发送模块类似

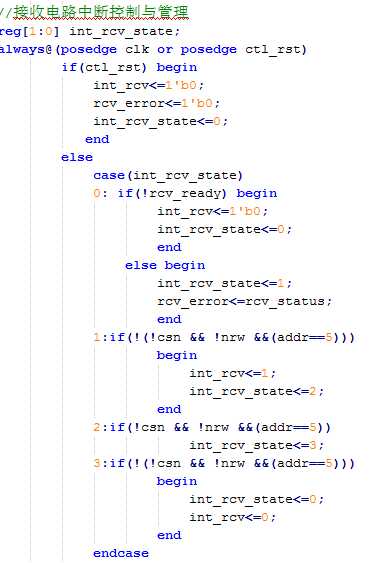

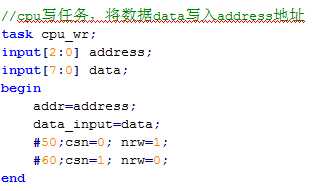

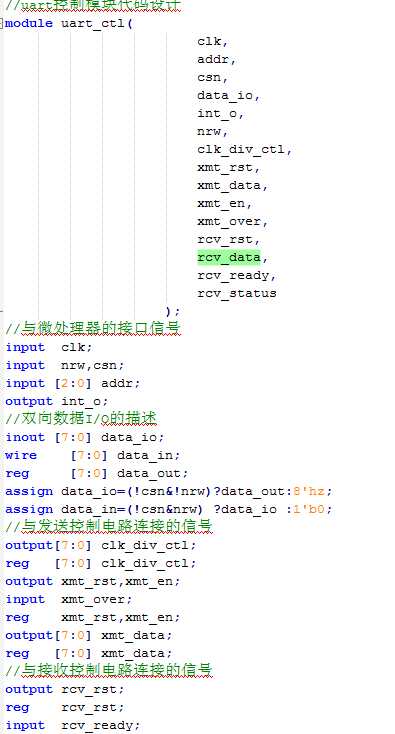

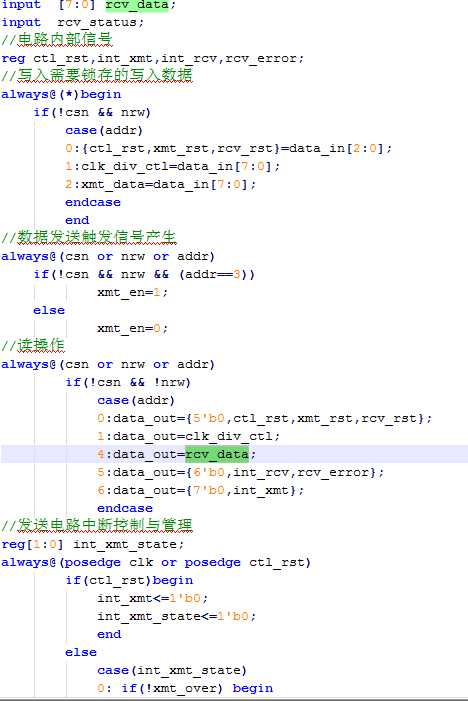

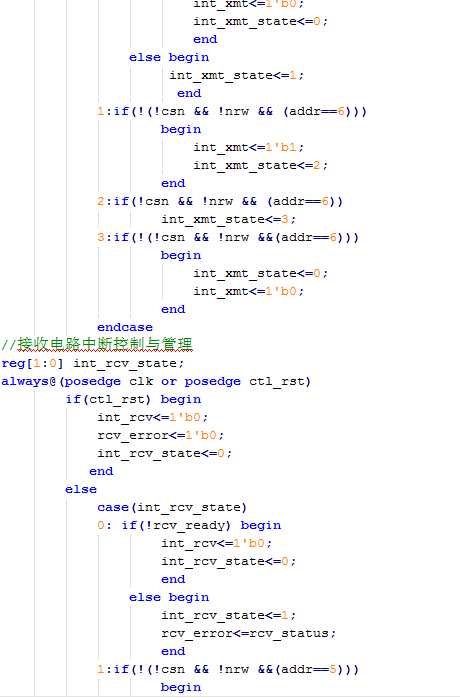

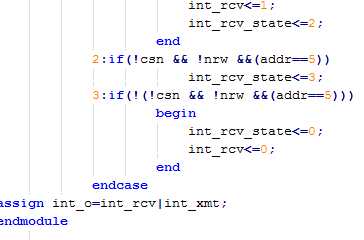

4,控制模块uart_ctl

// 地址对应寄存器

0:{ctl_rst,xmt_rst,rcv_rst} 地址0可读可写,复位信号

1:clk_div_ctl 地址1可读可写,时钟分频系数

2:xmt_data 地址2可写,发送数据缓存器

3: xmt_en 不可读,不可写,发送使能信号

4: rcv_data 地址4,可读,接受数据缓存器

5: {6‘b0,int_rcv,rcv_error} 地址5,可读,接受中断,奇偶校验位错误信号

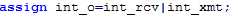

6: {7‘b0,int_xmt} 地址6,可读,发送中断位

中断信号发送给微机

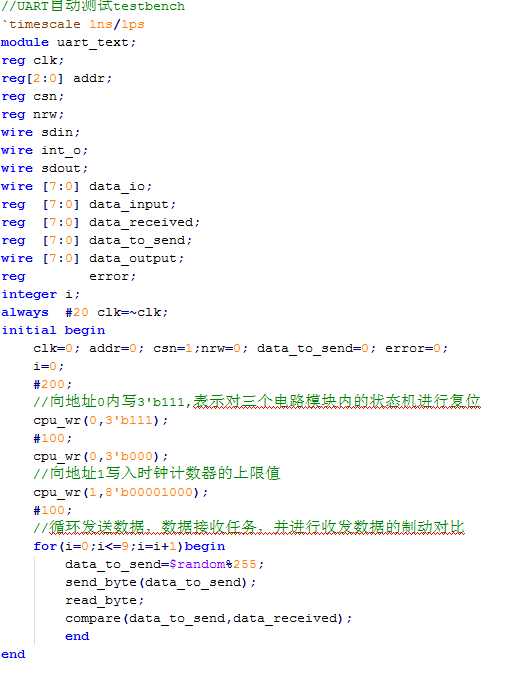

5,测试模块testbench

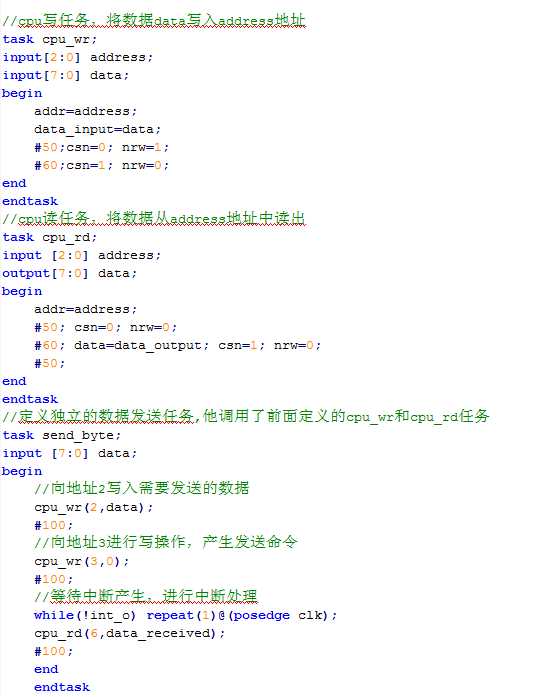

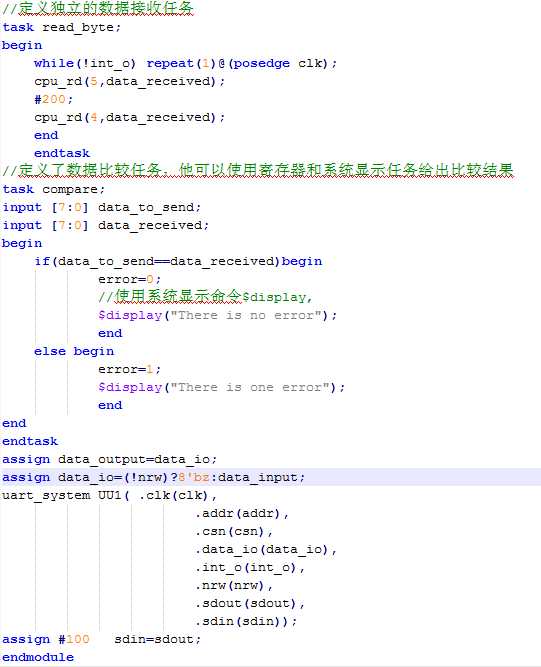

测试向量用了task任务,通过对比发送的数据和接受的数据,自动反馈是否产生错误

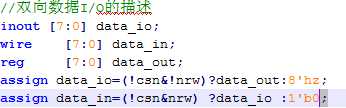

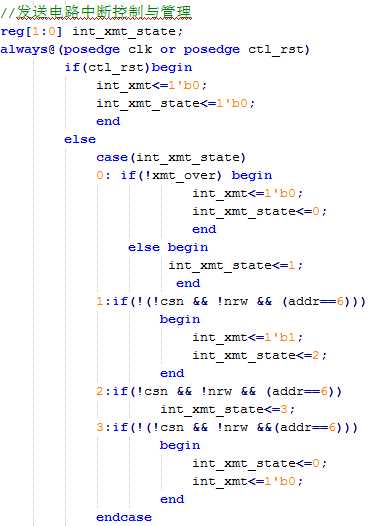

仿真cpu双向io口

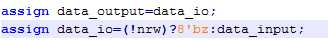

写任务

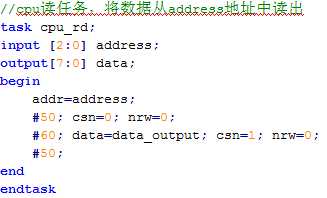

读任务

6,modelsim仿真结果

附:源程序uart_rcv.v

Uart_xmt.v

Uart_ctl.v

Uart_system

Testbench

标签:

原文地址:http://www.cnblogs.com/love-Jessica/p/4952468.html