标签:

关于 Quartus 的操作可以使用 Quartus 自带的帮助,帮助中有全套的操作教程。

中文网络教程链接(链接至altera中文官网,点击观看)

无论是英文帮助还是网络中文教程,他们的前提是你是有基础的,这些教程之会教给你我们的 quartus 套件该如何使用,至于 verilog 你应该实现学习,处理器的基本支持您应该都听的懂。入门知识并不在他们的职责之内,这本无可厚非。

这是我的第一个实验,目的是用一个按键控制一个 LED 灯,使用原理图输入。

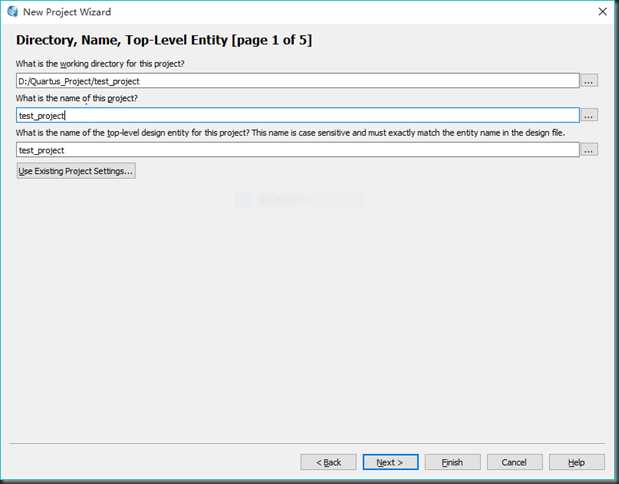

1. 点击 file –> new project wizard,新建一个项目

2. 输入工程目录

quartus要求事先新建一个空目录用于保存项目文件,路径不能有中文和空格。

此外项目名称和顶层模块名称一般和目录名称一致。

第三行的名称在使用 HDL 输入时必须和 顶层模块名称一致,否则编译报错,这里用的是原理图输入,暂时可以不管

3.添加其他文件到项目中

如果你已经写好了 verilog 文件,并且顶层模块名称与项目要求一致,在这里添加其他文件路径,这里我们留空。

4.选择 FPGA 的型号。

我用的 AX301 板上的 FPGA 属于 Cyclone IV EP4CE6FC8N,

Cyclone IV 是 Altera 的低端系列,Cyclone IV 有两个系列,其中 E 系列为不带高速收发器,而GX 系列带有高速收发器。另外结尾的 N 代表无铅工艺,L 代表 低电压。

从下面的表格中可也看到,该芯片有 6272 个 LE 单元,180 个用户管脚,2 个锁相环。

5.其他工具

quartus 可以使用其他工具来完成 FPGA 的设计,第一项是综合器的选择,第二项是仿真工具的选择,第四项是板级选择。

这里我们不用,不选留空也可以。

6.项目总览

用于确认前几部的选择是否正确,看看就可以。

7.项目建成之后,点击 file –-> new,新建一个原理图文件

8.原理图编辑器

双击原理图空白处,弹出以下对话框,在搜索框中输入 not,表示选择非门。

同理 and2 就是两输入的与门、or2 就是或门。要注意看看其他原件的符号,免得用的时候不知道。

输入完成后是这个样子,箭头按钮表示选择,小手表示拖动,此外还有导线(wire),总线(bus)和几个绘图按钮(方块、椭圆什么的)

如果输入或者输出是总线,则需要把名称改为像这样的 led[7..0],而不是 led[7:0]。

除了输入输出、符号之外,导线也可命名(右键点击导线,进行重命名)。

quartus 和 protel 一样使用网络标号来连接导线和总线,比如把一段总线命名为 a[3..0],接着把四根其他导线命名为a[3]、a[2]、a[1]、a[0],就可以可以实现他们之间的连接。

9.分配 FPGA 管脚

这个项目中用到了两个引脚,一个按键和一个 LED,查看用户手册,我的用户手册如下

这里我选择使用 LED0 和 KEY1,需要记住两个引脚名称 G15 和 E15。(-?-;)

分配管脚后

10.项目设置

这片 EP4CE6F17C8 芯片上可以接多个时钟,但由于该芯片内置了 PLL (锁相环,用于分频,倍频,改变时钟相位),对于初学者而言锁相环就够了并不需要使用多个时钟,所以芯片上就多出来的时钟管脚就用在按键上了,这个需要设置一下

在 project –> settings 下点击右上角的 Device…

找到 Device and Pin Options 这个页面,设置多用管脚为普通管脚

设置不用的管脚为三态,点击确定

由于上次我们没有设置引脚对应的管脚,虽然也生成了 sof 文件,但这个文件不能用。需要再次编译一下项目。

编译后查看一下警告、错误和提示信息。这里提示的是没有时序约束文件,初学者不用理会。

警告提示没有时钟,时钟在时序逻辑中一定会用到,这里是简单组合逻辑,没用用到时钟

而最上面的提示就是多用管脚的设置信息。

分配管脚后原理发生了变化,图上显示了分配的管脚名称

11.USB-Blaster 驱动安装

黑金的手册和视频上反复强调,不要带电插拔 Jtag 线(就是那组10pin 的排线),由于低端的 Cyclone IV 中没有钳位二极管,带电插拔 Jtag 口可能会烧坏 FPGA,我的流程是先关闭开发板开关,连上 Jtag 的两头,将 USB-Blaster 的另一头接上 usb 线,然后连接 USB-blaster 到电脑,连接开发板电源,最后打开开发板电源开关。

连好 USB-Blaster 到电脑,在控制面板依次找到 系统和安全 >> 系统 >> 设备管理器

没有安装驱动的在设备管理器中选择有黄色感叹号的设备,选择更新驱动程序,手动指定驱动文件夹路径到 C:\altera\13.0sp1\quartus\drivers\usb-blaster (这里假设安装路径为C盘)。

装好驱动后设备管理器是这个样子的

12.烧写到SRAM

一些个介绍 FPGA 的书中应该有提到,FPGA 基于 SRAM 工艺,SRAM 可以被反复配置,这个配置的过程就对 FPGA 进行编程,使之变成我们想要的功能,简单的编程可能像本项目一样只用到几个门,而复杂点的或许是编写数码管或者屏幕驱动。

后期可以把 FPGA 配置为一个处理器 ,quartus 中的 Qsys 或 SOPCBuilder 可以方便的生成一个处理器的 HDL 代码,这个被称为为 NIOS 的处理器远不像 ARM 那么复杂,可以供嵌入式处理器的入门学习。

连好开发板的必须线缆,下面进入烧写步骤。

设置 USB-Blaster

点击 AddFile… 选择项目 output_files 目录的 sof 文件(我的是 test_project.sof)。点击 start 按钮开始烧写,图为烧写成功。

由于 sof 文件烧写到的 SRAM 断电后就会丢失。所以 sof 文件用户调试,jic 文件和 pof 文件可以固定在 altera 的专用配置芯片 EPCS 上,从而实现离线运行。

保持连接电脑的状态,测试下按键,是否在按下时LED点亮了。你是否成功了呢? (●‘?‘●)

关闭 开发板电源,拔下 USB-Blaster 和电脑的连线,取下开发板的电源线,最后断开 Jtag口。

我的 FPGA 学习历程(02) —— 实验点亮 LED 灯

标签:

原文地址:http://www.cnblogs.com/sxyf/p/4964485.html