标签:

2、SDRAM内存工作原理

上面产生的误解关于 Bank ,这个bank 不是 和 S3C2440 芯片有关系(RAM 自身有bank , SDRAM 自身也有bank ,就像书 有 好几章节一样)

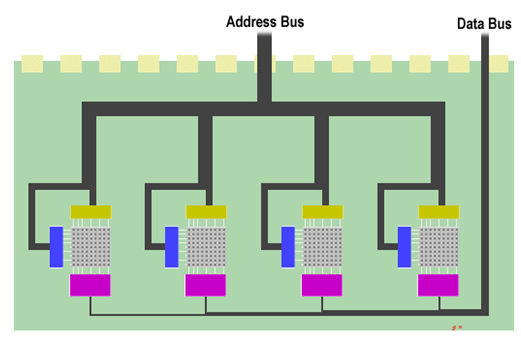

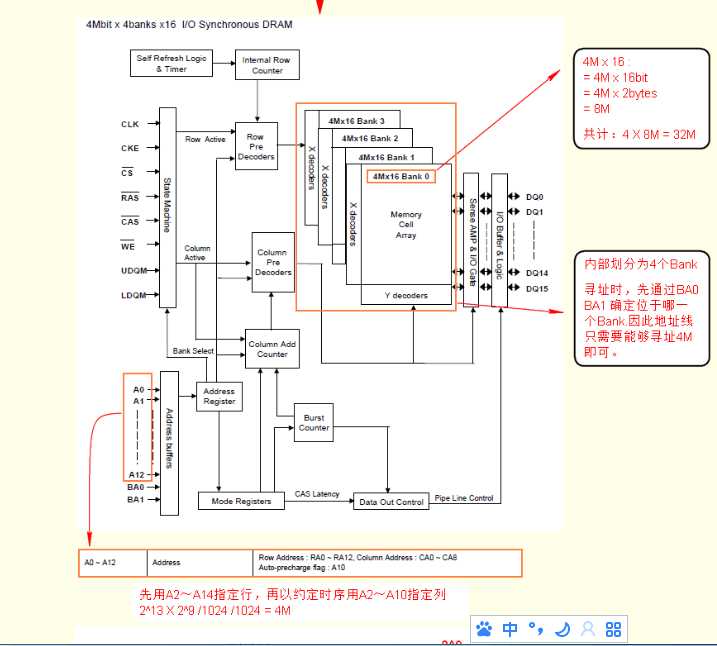

所以人们在 SDRAM内部分割成多个 L-Bank,目前基本都是 4个(这也是SDRAM规范中的最高L-Bank数量),由此可见,在进行寻址时就要先确定是哪个 L-Bank,然后在这个选定的 L-Bank中选择相应的行与列进行寻址。因此对内存的访问,一次只能是一个 L-Bank工作。如图2-50

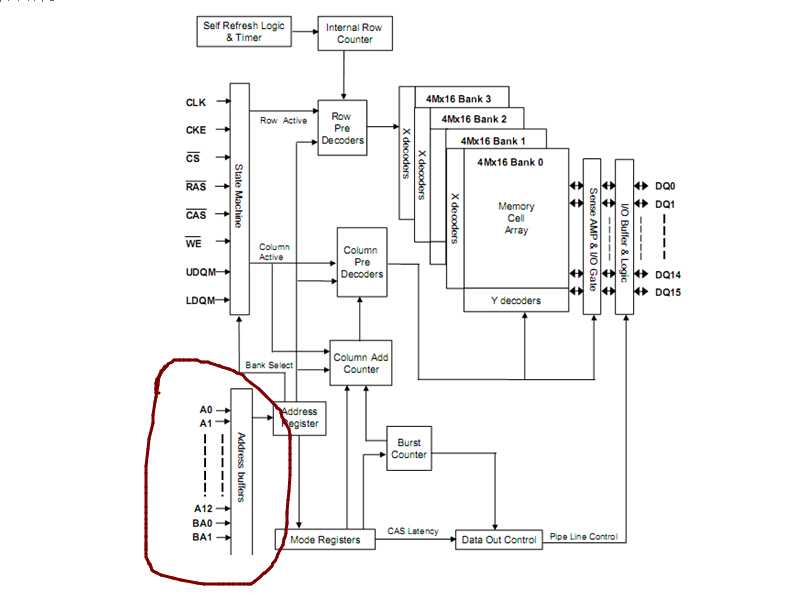

当对内存进行操作时(见下图),先要确定操作L-Bank,因此要对L-Bank进行选择。在内存芯片的外部管脚上多出了两个管脚BA0, BA1,用来片选4个L-Bank

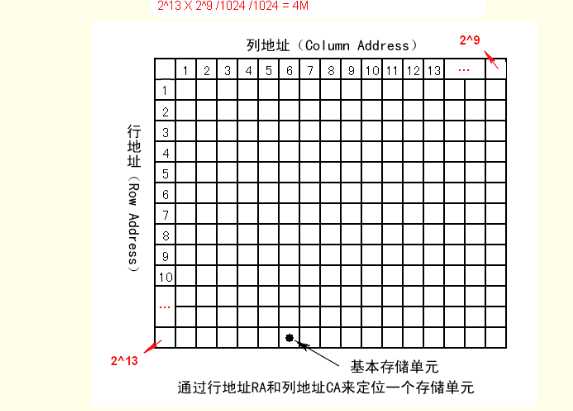

内存外接管脚地址线只有13根地址线A0~A12,它最多只能寻址8KB内存空间,到底使用什么机制来实现对64M内存空间进行寻址的呢?

SDRAM的行地址线和列地址线是分时复用的,即地址要分两次送出,先送出行地址(nSRAS行有效操作),再送出列地址(nSCAS列有效操作)。这样,可以大幅度减少地址线的数目,提高器件的性能和制作工艺复杂度。

但寻址过程也会因此而变得复杂。实际上,现在的SDRAM一般都以L-Bank为基本寻址对象的。由L-Bank地址线BAn控制L-Bank间的选择,

行地址线和列地址线贯穿连接所有的L-Bank,每个L-Bank的数据的宽度和整个存储器的宽度相同,这样,可以加快数据的存储速度。同时,BAn还可以使未被选中的L-Bank工作于低功耗的模式下,从而降低器件的功耗。

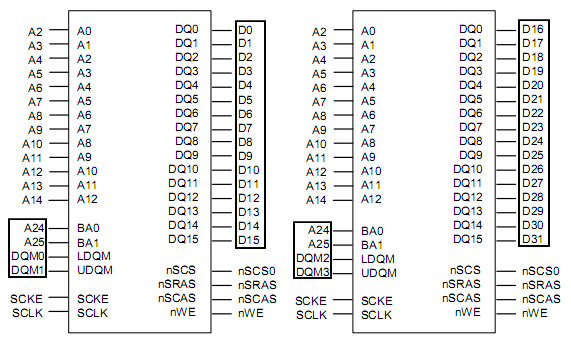

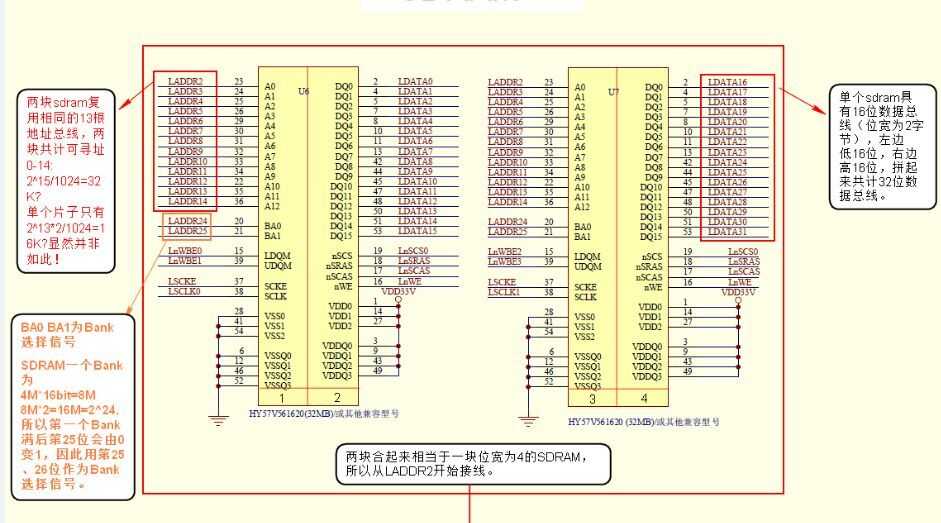

开发板内存控制器管脚接线(以MINI2440开发板为例)-

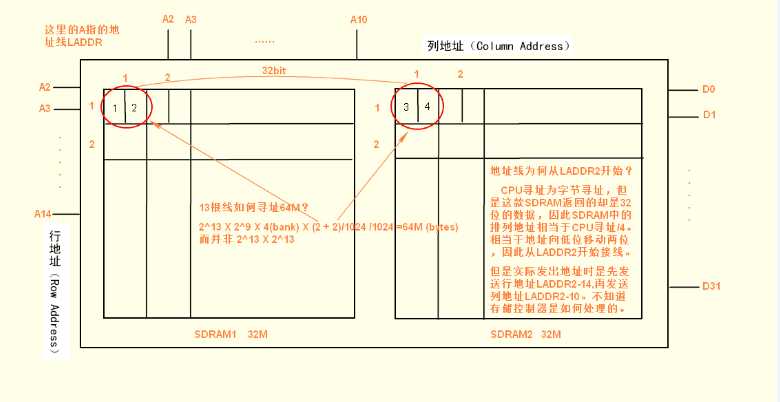

上图是S3C2440提供的两片16位芯片并联连接示意图,An是CPU地址总线,其中A2~A14为内存芯片寻址总线,之所以地址寻址总线从A2开始是因为内存地址都是按字节对齐的,,A24,A25为L-Bank片选信号,Dn为CPU数据总线,其它为对应控制信号线。

通过S3C2440 16位宽内存芯片接线图可以看出,两片内存芯片只有两个地方不一样,LDQM, UDQM和数据总线DQn接线方式不一样。

{LDQM和UDQM}

由于存储芯片位宽为16位,一次可以进行两个字节的读取。但是,通常操作系统里最小寻址单位是1字节,因此内存控制器必须要保证可以访问内存里每一个字节。UDQM ,LDQM分别代表16位数据的高,低字节读取信号,当读取数据时,LDQM /UDQM分别用来控制16位数据中高低字节能否被读取,当LDQM /UDQM为低电平时,对应的高/低字节就可以被读取,如果LDQM /UDQM为高电平时,对应的高/低字节就不能被读取。当向内存里写入数据时,LDQM /UDQM控制数据能否被写入,当LDQM /UDQM为低电平时,对应的高/低字节就可以被写入,如果LDQM /UDQM为高电平时,对应的高/低字节就不能被写入。通过对LDQM /UDQM信号的控制可以控制对两个存储芯片存储数据,由于两个存储单元的地址线是通用的,他们都能接收到CPU发出的地址信号,但是,发给两个存储单元的LDQM /UDQM信号是不同的,以此来区分一个字的高低字节。

S3C2440A为32位CPU,也就是说其数据总线和地址总线宽度都是32位(可以理解为32根线一端连接CPU内部,另外一端连接向内存控制器),那么内存数据的输入/输出端也要保证是32位总线,MINI2440上采用两片16位宽总线内存芯片并联构成32位总线。其中一个芯片连接到CPU数据总线的低16位,另外一个芯片连接到数据总线上的高16位,并联成32位总线,因此两个芯片的输入/输出总线连接到CPU总线上的不同管脚上。

总结: 知道这些就可以了,至于读写操作,这些 都是大神干的事情,偶们并不需要完全理解,当然时间够的话,理解了是好事,这个SDRAM芯片的时序图懂了,看其他的 datasheet 基本也不会有什么问题。记住不要舍本求末。

____________________________________________________________________________________________________________________________________________________________________________________

再次总结: // 还是要感谢各位的,一下子明白 为什么是64M

DSC$T.png)

W_[PKS_35XA~%$SQ0_SRK9.gif)

标签:

原文地址:http://www.cnblogs.com/shengruxiahua/p/5088007.html