标签:

gcc编译步骤:

预编译——> 编译——> 汇编——>连接——>

Make工具:在大型项目中有成百上千个源文件,Make工具是为了解决每次都通过手工输入gcc命令进行编译带来的非常不方便的问题 。

Makefile文件:是描述文件依赖关系的说明,由若干个规则组成。

Makefile规则格式:

目标:依赖关系

<tab键>命令

举个栗子

all:hello.o

gcc hello.o -o hello

hello.o:hello.c

gcc -c hello.c -o hello.o

clean:

rm *.o hello

引入变量改进后

CC=gcc

OBJECT=hello.o

all:$(OBJECT)

$(CC) $(OBJECT) -o hello

$(OBJECT):hello.c

$(CC) -c hello.c -o $(OBJECT)

clean:

rm *.o hello

CC=gcc

TARGET=all

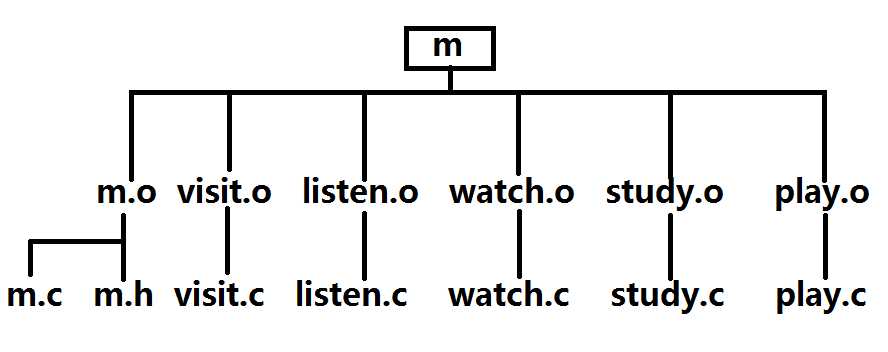

OBJECTS=m.o visit.o listen.o watch.o study.o play.o

$(TARGET):$(OBJECTS)

$(CC) $(OBJECTS) -o m

m.o:m.c m.h

$(CC) -c m.c -o m.o

visit.o:visit.c

$(CC) -c visit.c -o visit.o

listen.o:listen.c

$(CC) -c listen.c -o listen.o

watch.o:watch.c

$(CC) -c watch.c -o watch.o

study.o:study.c

$(CC) -c study.c -o study.o

play.o:play.c

$(CC) -c play.c -o play.o

clean:

rm *.o

Makefile预定义变量

$@ 规则的目标所对应的文件名

$< 规则中的第一个依赖文件名

$^ 规格中所有依赖的列表,以空格为分隔符

$(@D)目标文件的目录部分(如果目标在子目录中)

$(@F)目标文件的文件名部分(如果目标在子目录中)

CC=gcc

TARGET=all

OBJECTS=m.o visit.o listen.o watch.o study.o play.o

$(TARGET):$(OBJECTS)

$(CC) $^ -o m

m.o:m.c m.h

$(CC) -c $< -o $@

visit.o:visit.c

$(CC) -c $< -o $@

listen.o:listen.c

$(CC) -c $< -o $@

watch.o:watch.c

$(CC) -c $< -o $@

study.o:study.c

$(CC) -c $< -o $@

play.o:play.c

$(CC) -c $< -o $@

clean:

rm *.o

进一步改进:

CC=gcc

TARGET=all

OBJECTS=m.o visit.o listen.o watch.o study.o play.o

$(TARGET):$(OBJECTS)

$(CC) $^ -o m

*.o:*.c

$(CC) -c $< -o $@

clean:

rm *.o

标签:

原文地址:http://www.cnblogs.com/jin521/p/5106815.html