标签:style blog http color 使用 数据

本发明公开了一种双倍数据速率内存的内存控制器及其控制方法。内存控制器中包括仲裁器、主状态机、刷新管理单元、寄存器和功耗管理单元;主状态机向功耗管理单元反馈双倍数据速率内存的状态;根据功耗管理模块的通知,控制双倍数据速率内存进入或退出预充电掉电状态;功耗管理单元在双倍数据速率内存进入激活待机状态后,通知主状态机控制双倍数据速率内存进入预充电掉电状态,并在仲裁器指示当前接收到读写命令或刷新管理单元指示刷新周期到来时,通知主状态机控制双倍数据速率内存退出预充电掉电状态。应用本发明,能够降低软件资源在双倍数据速率内存功耗控制方面的消耗,并且在需要对双倍数据速率内存进行读写操作时快速退出低功耗状态。

[0001] 本发明涉及双倍数据速率(DDR,Double Data Rate)内存,特别涉及一种DDR内存的内存控制器及其控制方法。

[0002] DDR内存是目前广泛应用的一种内存器件,中央处理器(CPU,Computer Process Unit)或其他硬件加速器件对DDR内存的读写操作都需通过内存控制器实现。

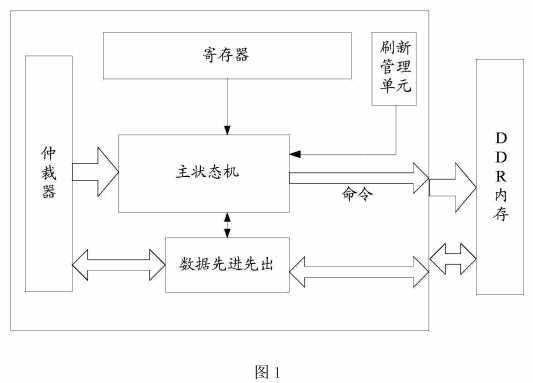

[0003] 图1为现有技术中内存控制器的结构示意图,该内存控制器包括:仲裁器、寄存器、主状态机、数据先进先出(Data FIFO)和刷新管理单元。

[0004] 仲裁器,用于在同一时刻有多个器件发起对DDR内存的读写操作时,仲裁出最高优先级的读写命令并发送给主状态机;在器件和数据先进先出的数据交互中转发数据。

[0005] 系统软件通过寄存器配置主状态机控制DDR内存进入自刷新状态的时机。寄存器还对主状态机进行常规配置。

[0006] 刷新管理单元,用于配置刷新周期,在刷新周期到来时向主状态机发送刷新请求。

[0007] 主状态机,用于按照寄存器的配置,控制DDR内存进入或退出自刷新状态;将仲裁器发送的读写命令转换 为与DDR内存接口相应的读写命令并发送给DDR内存;控制数据先进先出将仲裁器转发的数据发送到DDR内存,或将DDR内存发送的数据发送给仲裁器;在接收到刷新管理单元发送的刷新请求后,向DDR内存发送自动刷新命令,以控制DDR内存进行自动刷新。

[0008] 针对DDR内存的读写操作按照如下方式进行:

[0009] I)主状态机接收到仲裁器发送的对DDR内存的读写命令后,需要首先激活DDR内存。激活过程包括如下步骤:主状态机向DDR内存发送激活命令,激活命令中包含CPU或其他硬件加速器件指定的需要读操作的堆(bank)和行(row)地址;在001?内存内部,完成对所述行地址的译码并产生行选中信号把电容存储阵列中这个行的数据送到感应放大器(SA,Sense Amplifier),当数据停留在SA之后,DDR内存处于激活状态。

[0010] 2)在DDR内存处于激活状态之后,如果是读操作,主状态机将接收到的读命令转换为与DDR内存接口相应的读命令,该读命令中包含CPU或其他硬件加速器件指定的需要读操作的列(column)地址。在DDR内存内部,对上述列地址译码并产生选中信号选中SA里面的数据,然后把数据输入到读锁存器,最后输出到数据线上。主状态机控制数据先进先出将数据线上的数据发送给仲裁器,再由仲裁器转发给CPU或其他硬件加速器件。读操作完成后,DDR内存处于激活待机状态。

[0011] 3)在DDR内存处于激活状态之后,如果是写操作,主状态机将接收到的写命令转换为与DDR内存接口相应的写命令,该写命令中包含CPU或其他硬件加速器件指定的需要写操作的列地址,然后主状态机控制数据先进先出将待写入的数据输出到数据线上。在DDR内存内部,处于数据线上的数据被锁存到输入寄存器中,接着数据被写到SA中上述列地址对应的位置,最后执行预充电操作把SA中的数据写到电容存储阵列里面。写操作完成后,DDR内存处于激活待机状态。

[0012] DDR内存由读写操作产生的动态功耗是难以降低的,而在不执行读写操作时,DDR内存可能处于激活待机(active standby)状态、预充电待机(precharge standby)状态、激活掉电(active power down)状态、预充电掉电(precharge power down)状态和自刷新(self?refresh)状态,这些状态下的功耗称为静态功耗。其中,激活待机状态和激活掉电状态下的功耗较大,预充电待机状态下的功耗处于中等水平,预充电掉电状态和自刷新状态下的功耗较小。

[0013]目前,为了降低DDR内存的功耗,如果长时间没有读写操作,主状态机会控制DDR内存进入自刷新状态以降低功耗,这时DDR内存相当于休眠状态,数据不会丢失,但如果要重新对DDR内存里的数据进行读写则需要等待200个时钟周期和一个自动刷新命令的时间才能退出自刷新状态。另外,系统软件需要设计专门的功耗管理进程判断什么时候可以进入自刷新状态、什么时候需要退出,且需要通过寄存器重新配置主状态机,才能使主状态机能够在准确的时机控制DDR内存进入或退出自刷新状态。上述系统软件判断所需的时间一般都在毫秒级别以上,而某些便携式系统中,每隔一个固定的时间就需要对DDR内存进行读写操作,这个固定时间通常也在毫秒级别,这样不仅需要消耗较大的软件资源且响应速度很慢。

[0014] 本发明提供一种DDR内存的内存控制器,能够降低软件资源在DDR内存功耗控制方面的消耗,并且在需要对DDR内存进行读写操作时快速退出低功耗状态。

[0015] 本发明提供一种上述内存控制器的控制方法,能够降低软件资源在DDR内存功耗控制方面的消耗,并且在需要对DDR内存进行读写操作时快速退出低功耗状态。

[0016] 本发明的技术方案是这样实现的:

[0017] 一种DDR内存的内存控制器,包括:仲裁器、主状态机、刷新管理单元和寄存器,其中寄存器对主状态机进行常规配置;关键在于,所述内存控制器中还包括功耗管理单元;

[0018] 所述主状态机,向功耗管理单元反馈DDR内存的状态;根据功耗管理单元的通知,控制DDR内存进入或退出预充电掉电状态;

[0019] 所述功耗管理单元,在DDR内存进入激活待机状态后,通知主状态机控制DDR内存进入预充电掉电状态,并在仲裁器指示当前接收到读写命令或刷新管理单元指示刷新周期到来时,通知主状态机控制DDR内存退出预充电掉电状态。

[0020] 一种上述内存控制器的控制方法,关键在于,该方法包括:

[0021] A、功耗管理单元接收主状态机反馈的DDR内存的状态,判断DDR内存是否进入激活待机状态,如果是执行步骤B,否则继续执行步骤A ;

[0022] B、功耗管理单元通知主状态机控制DDR内存进入预充电掉电状态;

[0023] C、功耗管理单元监控到仲裁器指示当前接收到读写命令或刷新管理单元指示刷新周期到来时,指示主状态机控制DDR内存退出预充电掉电状态。

[0024] 可见,本发明实施例提供的内存控制器及其控制方法,在内部增加了功耗管理单元,该功耗管理单元在DDR内存处于激活待机状态时,通知主状态机控制DDR内存进入预充电掉电状态这一功耗较低的工作状态,并在外部输入读写命令或刷新周期到来时,通知主状态机控制DDR内存退出预充电掉电状态。一方面,功耗管理单元作为内存控制器内部的硬件,无需系统软件设置专门的功耗管理进程,也不需要在每次控制DDR内存进入或退出低功耗状态后重新配置寄存器,节省了系统软件在功耗管理上的消耗;另一方面,如果是因为接收到新的读写命令而需要DDR内存退出预充电掉电状态时,只需要3个时钟周期,如果是因为执行自刷新操作而需要DDR内存退出预充电状态时,只需要I个时钟周期,基本不影响内存控制器的读写效率和响应时间,响应速度大大提高。

[0031] 以上所述仅为本发明的较佳实施例而已,并不用以限制本发明,凡在本发明的精神和原则之内,所做的任何修改、等同替换、改进等,均应包含在本发明保护的范围之内。

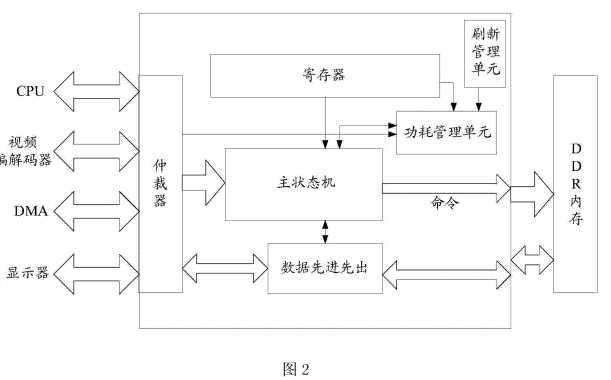

[0032] 图2为本发明实施例提供的DDR内存的内存控制器的结构示意图,该内存控制器包括:仲裁器、主状态机、刷新管理单元和寄存器,它们之间的连接关系及交互与现有技术中的相同,只是系统软件不再通过寄存器配置主状态机控制DDR内存进入或退出低功耗状态的时机,寄存器仅对主状态机进行公知的常规配置,另外刷新管理单元不与主状态机直接连接,这里不再赘述。图2中还示出了要对DDR内存进行读写操作的CPU及直接存储器存取(DMA)、视频编解码器和显示器等设备。

[0033] 该内存控制器中还包括功耗管理单元。

[0034] 上述主状态机,用于向功耗管理单元反馈DDR内存的状态;根据功耗管理单元的通知,控制DDR内存进入或退出预充电掉电状态。

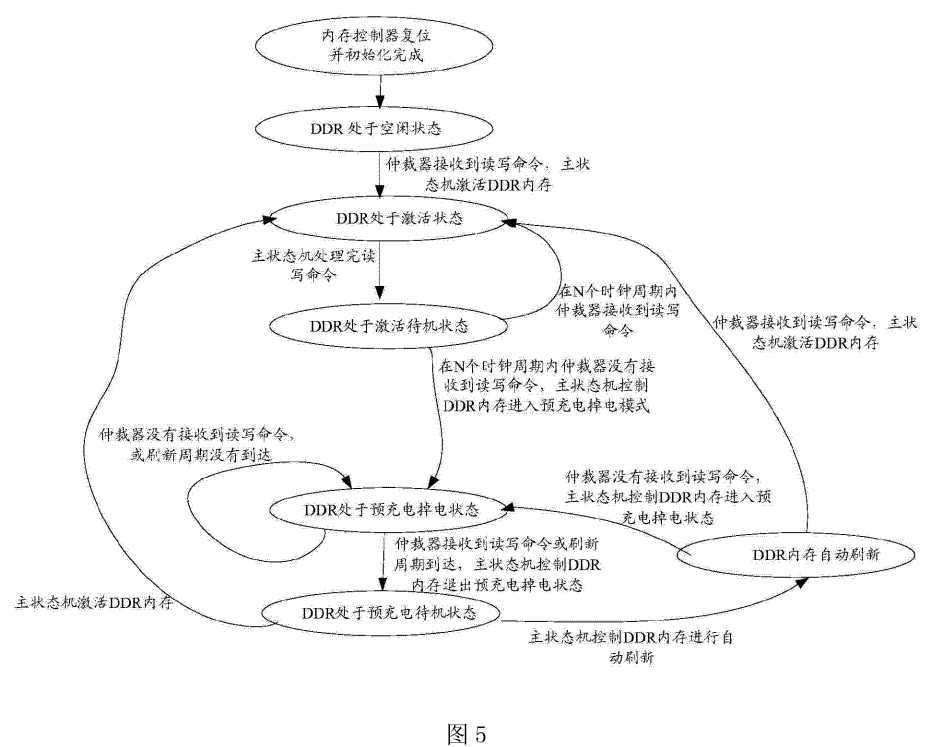

[0035] 上述功耗管理单元,用于在DDR内存进入激活待机状态后,通知主状态机控制DDR内存进入预充电掉电状态,并在仲裁器指示当前接收到读写命令或在刷新管理单元指示刷新周期到来时,通知主状态机控制DDR内存退出预充电掉电状态。如果是在刷新管理单元指示刷新周期到来时功耗管理单元通知主状态机控制DDR内存退出预充电掉电状态,功耗管理单元还会通知主状态机控制DDR内存进行自动刷新。进一步,当DDR内存处于自动刷新状态时,如果主状态机收到仲裁器发送的读写命令,则在自动刷新完成后激活DDR内存,如果没有收到仲裁器发送的读写命令,则在自动刷新完成后重新控制DDR内存进入预充电掉电状态。

[0036] 上述功耗管理单元通知主状态机控制DDR内存进入预充电掉电状态的时机不止一种情况,本发明实施例提供一种通过计时确定该时机的情况。寄存器为功耗管理单元配置计时阈值N,N的具体取值可以根据实际应用需要来确定,功耗管理单元在DDR内存进入激活待机状态时开始计时,当计时的时钟周期超过计时阈值N时通知主状态机控制DDR内存进入预充电掉电状态。

[0037] 本发明实施例中,主状态机控制DDR内存进入或退出某种状态,或者控制DDR内存执行某种操作,都通过相应的命令来实现,例如主状态机控制DDR内存进入预充电掉电状态时,会向DDR内存发送预充电掉电状态进入命令,控制DDR内存进行自动刷新时,会向DDR内存发送自动刷新命令。这些命令的格式和内容都属于本领域的公知常识,这里不再赘述。

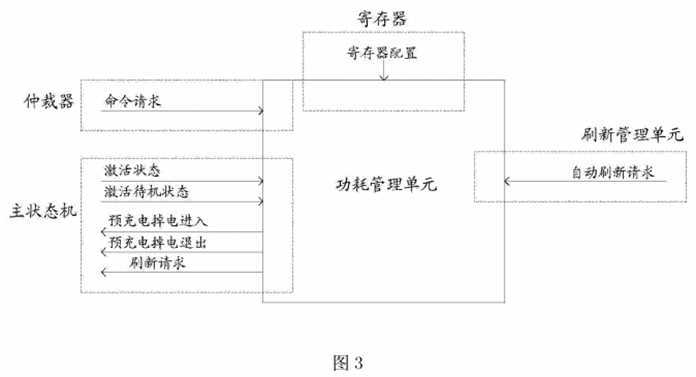

[0038] 图3为图2中所述功耗管理单元的信号传输示意图。

[0039] 功耗管理单元设置有命令请求输入接口、配置输入接口、激活待机状态输入接口、激活状态输入接口、第一刷新请求输入接口、第一刷新请求输出接口、第一预充电掉电状态输出接口和第二预充电掉电状态输出接口。

[0040] 上述命令请求输入接口与仲裁器的命令请求输出接口通过信号线连接,功耗管理单元通过该命令请求输出接口接收仲裁器发送的命令请求(cmd request)信号,该命令请求信号指示当前是否有外部输入的读写命令。

[0041 ] 上述配置输入接口与寄存器的配置输出接口通过信号线连接,功耗管理单元通过该配置输入接口接收寄存器发送的寄存器配置(register configure)信号,该寄存器配置信号中携带寄存器配置的计时阈值N。

[0042] 上述激活待机状态输入接口与主状态机的激活待机状态输出接口通过信号线连接,功耗管理单元通过该激活待机状态输入接口接收主状态机发送的激活待机状态(active standby state)信号,该激活待机状态信号指示当前DDR内存是否处于激活待机状态。

[0043] 上述激活状态输入接口与主状态机的激活状态输出接口通过信号线连接,功耗管理单元通过该激活状态输入接口接收主状态机发送的激活状态(active state)信号,该激活状态信号指示当前DDR内存是否处于激活状态。当DDR内存处于激活状态时,功耗管理单元不执行操作。

[0044] 上述第一刷新请求输入接口与刷新管理单元的第二刷新请求输出接口通过信号线连接,功耗管理单元通过该第一刷新请求输入接口接收刷新管理单元发送的自动刷新请求(Auto?refresh?request)信号,提示刷新周期到来。

[0045] 上述第一刷新请求输出接口与主状态机的第二刷新请求输入接口通过信号线连接,功耗管理单元通过该第一刷新请求输出接口向主状态机发送刷新请求(refreshrequest)信号,指示主状态机控制DDR内存进行自动刷新。

[0046] 上述第一预充电掉电状态输出接口与主状态机的第一预充电掉电状态输入接口通过信号线连接,功耗管理单元通过该第一预充电掉电状态输出接口向主状态机发送预充电掉电状态进入(precharge power down enter)信号,指示主状态机控制DDR内存进入预充电掉电状态。

[0047] 上述第二预充电掉电状态输出接口与主状态机的第二预充电掉电状态输入接口通过信号线连接,功耗管理单元通过该第二预充电掉电状态输入接口向主状态机发送预充电掉电状态退出(precharge power down exit)信号,指示主状态机控制DDR内存退出预充电掉电状态。

[0048] 功耗管理单元与寄存器、仲裁器、刷新管理单元和主状态机之间交互的各种信号均为电平信号,预先约定且使交互双方明确不同电平组合所代表的内容,即可实现前文所述的各种指示。

[0049] 下面给出本发明实施例提供的内存控制器的一个具体应用实例。

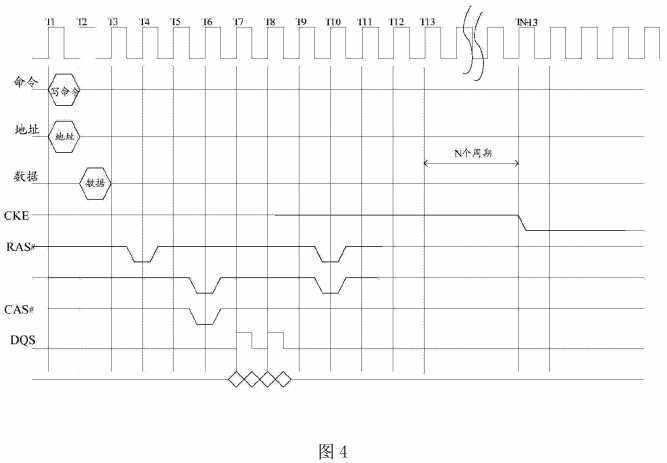

[0050] 在本应用实例中,CPU访问DDR内存进行写操作。图4为本应用实例中CPU访问DDR内存的时序图。其中CKE、RAS和CAS是DDR内存中控制逻辑的管脚,DQS为写操作中的锁存信号,这些均是本领域的公知常识,这里不再赘述。

[0051] Tl时亥lj,DDR内存处于空闲状态。

[0052] T2时刻,CPU在总线上发出写命令和地址。

[0053] T3时刻,CPU在总线上发出要写的数据。

[0054] T4时刻,内存控制器向DDR内存发送激活命令,DDR内存进入激活状态。

[0055] T6时刻,内存控制器向DDR内存发送写命令。

[0056] T7时刻,内存控制器开始向DDR内存写数据。

[0057] TlO时刻,内存控制器发出预充电命令完成写操作,该预充电命令持续3个时钟周期,之后DDR内存处于激活待机状态。

[0058] T13时刻,内存控制器中的功耗管理单元开始计时,当计时达到N个时钟周期总线上还未收到新的读写命令时,通知主状态机控制DDR内存进入预充电掉电状态以节省功耗。

[0059] 上述应用实例仅列举了内存控制器在写操作应用中的各种状态转换过程,更多的复杂应用可以在图5所示的状态转换图中体现出来。

[0060] 本发明实施例提供的内存控制器中的功耗管理单元,可以使用可编程逻辑器件实现,该功耗管理单元的各项功能都可以编程写入可编程逻辑器件。

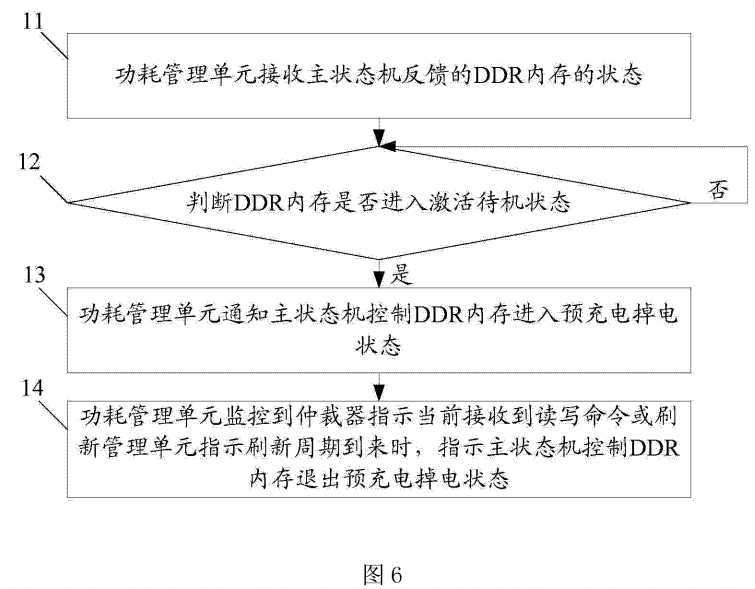

[0061] 本发明实施例还提供一种前文所述内存控制器的控制方法,图6为这种控制方法的流程图,该方法包括如下步骤:

[0062] 步骤11:功耗管理单元接收主状态机反馈的DDR内存的状态。

[0063] 步骤12:判断DDR内存是否进入激活待机状态,如果是执行步骤13,否则继续执行步骤12。

[0064] 步骤13:功耗管理单元通知主状态机控制DDR内存进入预充电掉电状态。

[0065] 步骤14:功耗管理单元监控到仲裁器指示当前接收到读写命令或刷新管理单元指示刷新周期到来时,指示主状态机控制DDR内存退出预充电掉电状态。

[0066] 上述步骤13中,功耗管理单元通知主状态机控制DDR内存进入预充电掉电状态之前,可以进一步包括:在DDR内存进入激活待机状态时开始计时。当计时的时钟周期大于寄存器配置的计时阈值时,功耗管理单元再执行所述通知状态机控制DDR内存进入预充电掉电状态的操作。

[0067] 上述步骤14中,当功耗管理单元监控到刷新管理单元指示刷新周期到来时,可以进一步指示主状态机控制DDR内存进行自动刷新。进一步,当DDR内存处于自动刷新状态时,如果主状态机收到仲裁器发送的读写命令,则在自动刷新完成后激活DDR内存,如果没有收到仲裁器发送的读写命令,则在自动刷新完成后重新控制DDR内存进入预充电掉电状态。

[0068] 与内存控制器中的介绍相同,上述方法中,功耗管理单元和寄存器、仲裁器、刷新管理单元及主状态机之间的各种交互,都通过信号传输实现,具体的信号类型这里不再赘述,这些信号也都是电平信号,预先约定且使交互双方明确不同电平组合所代表的内容。

[0069] 可以看出,本发明实施例提供的内存控制器机器控制方法,在内部增加了功耗管理单元,该功耗管理单元在DDR内存处于激活待机状态时,通知主状态机控制DDR内存进入预充电掉电状态这一功耗较低的工作状态,并在外部输入读写命令或刷新周期到来时,通知主状态机控制DDR内存退出预充电掉电状态。一方面,功耗管理单元作为内存控制器内部的硬件,无需系统软件设置专门的功耗管理进程,也不需要在每次控制DDR内存进入或退出低功耗状态后重新配置寄存器,节省了系统软件在功耗管理上的消耗;另一方面,如果是因为接收到新的读写命令而需要DDR内存退出预充电掉电状态时,只需要3个时钟周期,如果是因为执行自刷新操作而需要DDR内存退出预充电状态时,只需要I个时钟周期,基本不影响内存控制器的读写效率和响应时间,响应速度大大提高。

SRC=https://www.google.com.hk/patents/CN102243526B

双倍数据速率内存的内存控制器及其控制方法,布布扣,bubuko.com

标签:style blog http color 使用 数据

原文地址:http://www.cnblogs.com/coryxie/p/3861947.html