标签:des style blog http color os

To ensure that a memory device operates in self-refresh mode, the memory controller includes (1) a normal-mode output buffer for driving a clock enable signal CKE onto the memory device‘s CKE input and (2) a power island for driving a clock enable signal CKE_prime onto that same input. To power down the memory controller, the normal-mode output buffer drives signal CKE low, then the power island drives signal CKE_prime low, then the memory controller (except for the power island) is powered down. The power island continues to drive the memory device‘s CKE input low to ensure that the memory device stays in self-refresh mode while the memory controller is powered substantially off. To resume normal operations, the power module powers up the memory controller, then the normal-mode output buffer drives signal CKE low, then the power island is disabled, then the memory controller resumes normal operations of the memory device.

The present invention relates to electronics, and, in particular, to memory devices having self-refresh modes.

In typical computer hardware architectures, an integrated circuit (IC) memory device chip is controlled by a separate IC memory controller chip that controls the writing of data to and the reading of data from the memory device during normal operations of the memory device. Some memory devices are capable of operating in a self-refresh mode in which the memory device maintains its stored data without any active command from the memory controller, such as when the memory controller is powered off.

For some memory devices, such as DDR1 and DDR2 registered dual in-line memory modules (RDIMMs) defined by Joint Electron Device Engineering Council (JEDEC) standards JESD79F and JESD79-2E, respectively, where DDR stands for "double data rate," the memory device‘s RESET signal can be used to keep the memory device in self-refresh mode by holding the memory device‘s clock enable (CKE) line low while allowing the memory controller to be powered down. For other memory devices, such as DDR3 RDIMM memory devices defined by JEDEC standard JESD79-3C, asserting the RESET signal takes the memory device out of self-refresh mode. As such, when the memory controller is powered off, the RESET signal cannot be used to keep the memory device in self-refresh mode, thereby jeopardizing the integrity of the data stored in the memory device.

In one embodiment, the present invention is apparatus comprising a memory controller for controlling a memory device having a clock enable (CKE) input. The memory controller comprises first circuitry and second circuitry. The first circuitry is adapted to apply a first CKE signal to the CKE input during a normal operating mode. The second circuitry is adapted to apply a second CKE signal to the CKE input during a self-refresh operating mode. During the self-refresh operating mode, (i) the first circuitry is powered off and (ii) the second circuitry is powered on to drive the second CKE signal to a self-refresh signal level for the memory device.

In another embodiment, the present invention is a method for controlling a memory device having a clock enable (CKE) input. The method comprises (a) using first circuitry to apply a first CKE signal to the CKE input during a normal operating mode and (b) using second circuitry to apply a second CKE signal to the CKE input during a self-refresh operating mode. During the self-refresh operating mode, (i) the first circuitry is powered off and (ii) the second circuitry is powered on to drive the second CKE signal to a self-refresh signal level for the memory device.

As used in this specification, the term "powered off" refers to a state of an integrated circuit (IC) chip in which no power is applied to the chip. The term "powered on" refers to a state in which power is applied to the chip. The term "powering up" refers to a transition from the powered-off state to the powered-on state, while the term "powering down" refers to a transition from the powered-on state to the powered-off state.

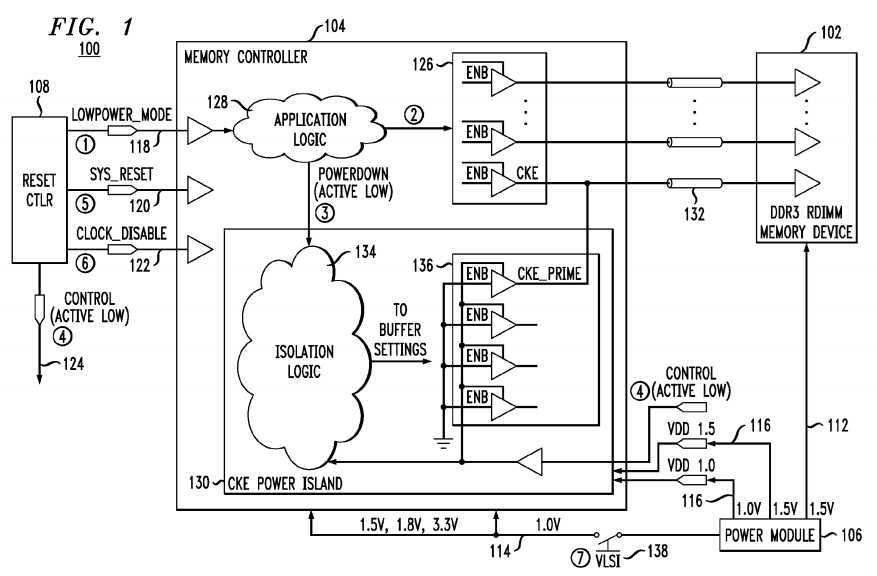

FIG. 1?shows a simplified block diagram of memory circuitry?100, according to one embodiment of the present invention. Memory circuitry?100?includes DDR3 RDIMM memory device?102, memory controller?104, power module?106, and reset controller?108. Memory controller?104?controls the writing of data to and the reading of data from memory device?102. Power module?106?provides power to memory device?102?via power lines?112?and to memory controller?104?via main power lines?114?and backup power lines?116. Reset controller?108?controls the operations of memory controller?104?via control lines?118-124.

In addition to other circuitry not shown in?FIG. 1, memory controller?104?includes output buffers?126, application logic?128, and CKE power island?130. Application logic?128?controls the operations of output buffers?126, which drive signals into memory device?102, including clock enable signal CKE via signal line?132?at the memory devices CKE input. CKE power island?130?includes isolation logic?134and output buffers?136. Isolation logic?134?controls the operations of output buffers?136, whose outputs are connected to the same signal lines as the outputs of output buffers?126, including clock enable signal CKE_prime, which is connected to the same signal line?132?that receives the CKE signal from a corresponding one of output buffers?126. Note that, in general, connections could be made on the die or in the package routing. In general, the corresponding buffer?126?can be used to drive the CKE signal onto signal line?132, when the corresponding buffer?136?is disabled, and vice versa. In addition, both corresponding buffers can be used simultaneously to drive equivalent output signals (i.e., the CKE and CKE_prime signals both high or both low) onto signal line?132.

Although?FIG. 1?shows memory circuitry?100?having separate components, in general, two or more of those components may be implemented in a single integrated system-on-a-chip (SOC).

Memory circuitry?100?supports two different modes of operation: normal operating mode and self-refresh operating mode.

FIG. 1?indicates, via circled reference numbers, the sequence of operations to transition memory circuitry?100?from its normal operating mode into its self-refresh operating mode, and vice versa. In particular, memory circuitry?100?can be transitioned from its normal operating mode into its self-refresh operating mode (i.e., a power-down transition) by the following sequence of events:

Note that power module?106?continues to provide power to memory device?102?via power lines?112?and to CKE power island?130?via backup power lines?116, such that isolation logic?134?controls output buffers?136to drive the CKE_prime signal low to enable memory device?102?to remain in its self-refresh mode.?Note that the seven steps involved in the power-down transition may be implemented in a different order. For example, the order of steps (2) and (3) can be reversed. Note further that some of the steps may be optional. For example, step (5) is provided as a safety measure, but may be omitted in light of step (2).

In addition, referring to the same circled reference numbers in?FIG. 1, but in descending order (with the exception of steps (1) and (2)), memory circuitry?100can be transitioned from its self-refresh operating mode back into its normal operating mode (i.e., a power-up transition) by the following sequence of events:

Note that, here, too, the seven steps involved in the power-up transition may be implemented in a different order. For example, the order of step (3) can be implemented after steps (1) and (2).

Memory circuitry?100?enables memory controller?104?to be substantially powered down while maintaining the integrity of the data stored in memory device?102.

In one implementation, each of elements?102-108?of?FIG. 1?is a discrete electronic module mounted on a circuit board and interconnected via suitable board traces. Memory controller?104?may be part of a larger integrated circuit module that provides, in addition to the control of memory device?102, other functions related to other system elements not shown in?FIG. 1. Similarly, power module?106?may provide power to other system elements not shown in?FIG. 1, including other memory devices.

Although the present invention has been described in the context of memory circuitry?100?of?FIG. 1?having a single DDR3 RDIMM memory device, it will be understood that, in general, the present invention can be implemented for any suitable type of memory topology having one or more memory devices, where those memory devices can be RDIMMs, such as DDR1, DDR2, or DDR3 RDIMMs, or other suitable on-board devices.

SRC=https://www.google.com.hk/patents/US8139433

Memory device control for self-refresh mode,布布扣,bubuko.com

Memory device control for self-refresh mode

标签:des style blog http color os

原文地址:http://www.cnblogs.com/coryxie/p/3861909.html