标签:

本文部分内容转自zhaocj的博客,感谢!地址为:http://blog.csdn.net/zhaocj/article/details/5495730

A/D转换,又称为模/数转换,是将模拟量信号转换为计算机能够处理的数字信号。S3C2440集成了8通道10位CMOS A/D转换器,最大转换率为2.5MHz A/D转换器时钟下的500KSPS。A/D转换器支持片上采样-保持功能和掉电模式的操作。

有如下特性:

分辨率:10位

差分线性误差:±1.0LSB

积分线性误差:±2.0LSB

最大转换率:500KSPS

功耗低

供电电压:3.3V

模拟输入范围:0~3.3V

片上采样-保持功能

普通转换模式

分离的X/Y方向转换模式

自动(顺序)X/Y方向转换模式

等待中断模式

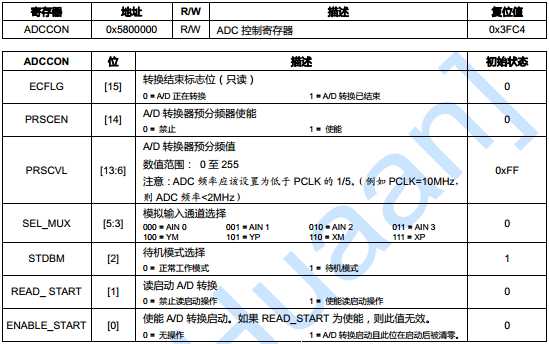

对于s3c2440来说,实现A/D转换比较简单,主要应用的是ADC控制寄存器ADCCON(如图1)和ADC转换数据寄存器ADCDAT0(如图2)。

图1 ADC控制寄存器(ADCCON)

第15位,用于标识A/D转换是否结束。

第14位,用于使能是否进行预分频。

第6~13位,存储的是预分频数值,因为A/D转换的速度不能太快,所以要通过预分频处理才可以得到正确的A/D转换速度,例如,我们想要得到A/D转换频率为1MHz,则预分频的值应为49。

第3~5位,表示的是A/D转换的通道选择。

第2位,可以实现A/D转换的待机模式。

第1位,用于是否通过读取操作来使能A/D转换的开始。

第0位,是在第1位被清零的情况下用于开启A/D转换。

A/D转换时间的计算:

当PCLK频率为50MHz并且预分频器的值为49时,共10位的转换时间如下:

A/D转换器频率 = 50MHz / (49+1) = 1MHz

转换时间 = 1 / (1MHz / 5周期 ) = 1/200KHz = 5us

注释:次A/D转换器被设计为最高工作在2.5MHz时钟下,因此转换率可以达到500KSPS(每秒采样次数)。

说明:上述公式中为什么是5周期?查了很久,找到一个解释:

“A/D converter freq=1MHZ,可是conversion time=1/(1MHZ/5 cycles),这个5 cycles是怎么来的,而且 1/频率 不就是时间么。原来是基础概念不清楚,这里的1MHZ仅仅是系统通过我们对AD预设分频以后得到的AD时钟频率,在2440里最大可以达到2.5MHZ,和我们的转换时间并不是成倒数关系。转换时间包括有:AD建立的时间(用几个时钟周期)、一位一位转换的时间(再用几个时钟周期)、保存数据的时间(再再用上几个时钟周期),在2440里面这些时间加起来应该是5个时钟周期,所以才会有上面的公式。另外SPS这个单位是ADC的参数:即每秒模数转换器采点数(采样率)。2440中最高可以达到500KSPS。”

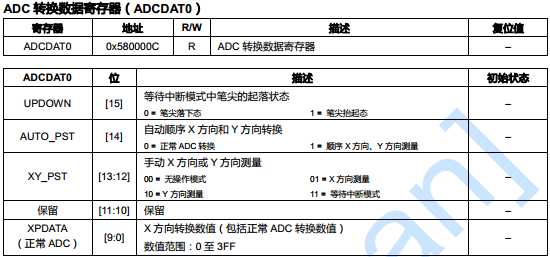

寄存器ADCDAT0的低10位用于存储A/D转换后的数据。

图2 ADC转换数据寄存器(ADCDAT0)

以AIN0为例,当模拟量通过AIN0通道传入A/D转换器,通过转换,将转换结果存储在ADCDAT寄存器的低10位中,而S3C2440的ADC转换器模拟量输入范围为0~3.3V,因此取ADCDAT寄存器的低10位数值1023对应3.3V,呈线性关系。

标签:

原文地址:http://www.cnblogs.com/may1016/p/5133388.html