标签:

此文是写给0基础学习者,也是对自己知识点总结水平的考验。

对于有C基础的人来说,学习verilog应该是轻而易举 —— 类比法学习。

第一步:格式。

对于C来说我们前面会写

‘include“stdio.h”

int main {.....};

直接转化到verilog中是

module module_name (....);

........

endmodule

对于C 的意思就是告诉编辑器,我要在有这个库的前提下,建立这么一个函数,它实现的功能是......。而对于Verilog来说就是告诉编辑器,我要建立一个数字模块,这个模块实现..... 功能。OK 我们再讨论省略部分的内容。

第二步:运算符

大家知道HDL 是数字电路的描述性语言,所以需要一点点数字电路的基础就行了,数字电路中三个最小最基本的逻辑是 与,或,非。在verilog中的运算符就是 &,|,! 。OK ,知道这么多就可以开始我们的verilog程序设计了。

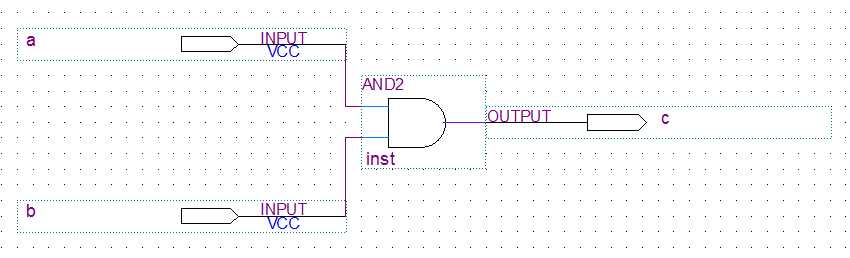

现在我们要实现一个下图所示的电路功能,这是一个a和b输入,c输出,内部实现与功能的电路图

设计开始和C一样先写格式,取一个工程的名字叫project_a .

module project_a ();

endmodule

好了,我们要想想看,我们拿到一个芯片做top view的时候我们看到的是什么? 是pin脚。所以我们要把pin脚的信息告诉编辑器,那么代码就变成了

module project_a ( input a, input b, output c );

endmodule

格式很灵活,还可以是

1 module project_a ( 2 a, 3 b, 4 c 5 ); 6 input a ; 7 input b; 8 output c ; 9 10 11 12 endmodule

或者是将6,7 两行合并成 input a ,b ;

个人比较推荐第二种,原因以后再说。格式问题,不用纠结。只是要注意一下哪里是 “;” 哪里是 “,” 就可以了。

现在整个top view 已经做完了,现在要说说具体实现了。在C语言中赋值是直接给的,在Verilog中赋值要借助两个关键字 always 和assign才可以把值赋过去。先说assign 的格式

assign c = a&b ;

意思就是左边变量c 这根线上的信号结果等于右边信号运算的结果。那么最终的程序就是

1 module digtal_HDL_test ( 2 a , 3 b , 4 c 5 ); 6 input a; 7 input b ; 8 output c ; 9 10 assign c = a&b ; 11 12 endmodule

再看always ,因为语法要求always里面所有赋值等式左边的变量都必须是reg,所以得把c的类型改一下,就是在always的前面加上一条语句 : reg c ;那么最终的程序就是

1 module digtal_HDL_test ( 2 a , 3 b , 4 c 5 ); 6 input a; 7 input b ; 8 output c ; 9 10 reg c ; 11 12 always @ (a or b) 13 c = a&b ; 14 15 endmodule

第12行的意思是 “经常(always)在(@) a或者b (a or b)发生变化的时候去执行下面的语句”

好了,现在我们程序设计就完毕了。现在让我们来回顾一下我们的程序包含了哪些东西

1,模块的结构和端口。端口还有inout 双向口(这个高级一点,http://www.cnblogs.com/sepeng/p/5126424.html 里面有介绍,可以先不追究)

2,运算符。verilog的运算符分为单目运算和双目运算符,以及三目运算符。部分和C的是一样的。

3,常量及变量。分为,数字,参数,变量(wire,reg ,memory)

4,连续赋值语句assign 以及过程赋值语句always。

具体说明就是念书了,请参照 夏宇闻老师的《Verilog数字系统设计教程》

练习流水灯实验,熟悉设计流程以及工具的使用,下板看到效果才行。

(流水灯实验中要贯穿,三目运算符,拼接移位操作,数字,常量,变量)

作业:硬件抽奖小模型。

一共有16个号码,其中有两个号码是中奖号码(具体号码是机密,程序内部定义),输入一个数字,按下使能键。如果不正确两个灯一直是亮的,如果正确,对应的那个灯就会灭。

附加功能:1,

标签:

原文地址:http://www.cnblogs.com/sepeng/p/5223318.html