标签:

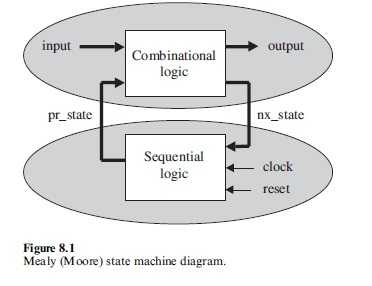

逻辑设计, 顾名思义, 只要理清了逻辑和时序, 剩下的设计就是做填空题了。

简单总结了有限状态机的一种设计方式, 详细参见 <<Circuit Design with VHDL>> chapter 8 State Machines

1 有限状态机

2 VHDL模板之一

1) 端口定义

library IEEE; use ieee.std_logic_1164.all; --! 端口定义 entity <entity_name> is port ( INPUT : in <data_type>; RST : in std_logic; CLK : in std_logic; OUTPUT : out <data_type> ); end <entity_name>;

2) 状态定义

--! 结构体 architecture <arch_name> of <entity_name> is type state is (state0, state1, state2, ...); signal c_state, n_state : state; begin end <arch_name>;

3) 时序逻辑

pfsmsyn: process (rst, clk) begin if (rst = ‘1‘) then c_state <= state0; elsif (clk‘event and clk=‘1‘) then c_state <= n_state; endif; end process;

4) 组合逻辑

pfsmlogic: process (input, c_state) begin case c_state is when state0 => if (input = ...) then output <= <value>; --输出 c_state <= state1; --状态 else ... end if; when state1 => ... ... ... ... ... ... when others => ... ... end case; end process;

标签:

原文地址:http://www.cnblogs.com/xinxue/p/5223810.html