标签:

Verilog

case-sensitive, all keywords are lowercase

1 continuous assignment

assign data_left = data_right; // right drive left(net)

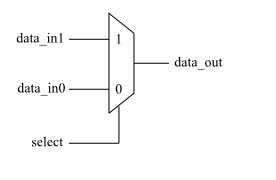

例 1) mux

assign data_out = select ? data_in1 : data_in0;

2 procedural assignment

1) blocking ("=")

execute sequential

2) nonblocking ("<=")

read (right) -> schedule (left) -> execute (<=)

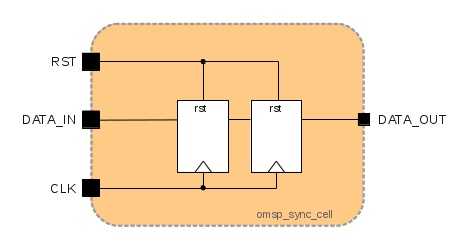

例 2) synchronizer

reg [1:0] data_sync; always @ (posedge clk or posedge rst) begin if (rst) data_sync <= 2‘b00; else data_sync <= {data_sync[0], data_in}; end assign data_out = data_sync[1]; synchronizer

标签:

原文地址:http://www.cnblogs.com/xinxue/p/5246441.html