标签:

一、sdram的介绍SDRAM(Synchronous Dynamic Random Access Memory),同步动态随机存储器,同步是指 Memory工作需要同步时钟,内部的命令的发送与数据的传输都以它为基准;动态是指存储阵列需要不断的刷新来保证数据不丢失;随机是指数据不是线性依次存储,而是自由指定地址进行数据读写。

二、s3c2410内部存储器

上面的图是我个人对存储器的理解。

我们知道,市面上内存的类型很多,那一款cpu是如何来识别如此多的RAM呢?这一切都是内存控制器来做的,我们就需要对内存控制器进行配置。当然内存控制器支持的 RAM类型也是有限的。其实cpu在取数据的时候,只是执行一条指令,例如:ldr r0,[r2];关于数据怎么来,cpu并不关心。整个数据的读取和写入全部由内存控制器完成。

三、s3c2410的地址空间

s3c2410的"存储控制器"提供了访问外部设备所需的信号,它有如下特性:

A.支持小字节 、大字节序(通过软件选择)

B.每个BANK的地址空间为128M,总共1GB(8BANKS)

C.可编程控制的总线位宽(8/16/32-bit),不过BANK0只能选择两种位宽(16/32-bit)

D.总共8个BANK,BANK0-BANK5可以支持外接ROM,SRAM等,BANK6-BANK7 除可以支持ROM、SRAM外,还支持SDRAM等

E.BANK0-BANK6共7个BANK的起始地址是固定的

F.BANK7的起始地址可编程选择

G.BANK6、BANK7的地址空间大小是可编程控制的

H.每个BANK的访问周期均可编程控制

I.可以通过外部的"wait"信号延长总线的访问周期 <

J.在外接SDRAM时,支持自刷新(self-refresh)和省电模式(power down mode)

S3C2410对外引出的27根地址线ADDR0-ADDR26的访问范围只有128MB,那么如何达到上面所说的1GB的访问空间呢?CPU对外还引出了8根片选信号nGCS0-nGCS7,对应于BANK0-BANK7,当访问BANKx的地址空间时,nGCSx引脚输出低电平用来选中外接的设备。这样,每个nGCSx对应128MB地址空间,8个nGCSx信号总共就对应了1GB的地址空间。8个BANK如下图所示:

如上图所示,左边对应不使用NAND FLASH作为启动设备,右边对应使用NAND FLASH作为启动设备

在fs2410上,BANK0接了NOR FLASH,也就说它既支持从NOR FALSH启动,也支持从NAND FLASH 启动。

接线如下

注意:

把跳线帽拔了是从NOR FLASH启动,此时零地址在NOR FLASH上,S3C2410片内的4k SRAM被映射到高地址0x40000000。

把跳线帽插上是NAND FLASH启动,此时SRAM被映射到零地址。此时,硬件上会自动把NAND FLASH前4k拷贝到SRAM中去。

S3C2410作为32位的CPU,可以使用的地址范围理论上可以达到4G。除了上述用于连接外设的1GB地址空间外,还有一部分是cpu内部寄存器的地址,剩下的地址空间没有使用。

四、SDRAM的工作原理

SDRAM的内部是一个存储阵列。阵列就如同表格一样,将数据"填"进去。在数据读写时和表格的检索原理一样,先指定一个行(Row),再指定一个列(Column),我们就可以准确地找到所需要的单元格,这就是内存芯片寻址的基本原理。

先来看看fs2410上面内存的接线原理图

内存的芯片是:K4S561632D-TC75

关键特性如下:

1.4M x 16bit x 4BANK = 32 M

2.64ms refresh period (8K Cycle)

(一个bank刷新完所需时间64ms,总共8 k = 8192个行,每一行刷新的间隔时间为64ms / 8192 = 7.8125us)

3.MAX 主频133MHz(CL=3)

注意:CL,就是在CAS发出之后,仍要经过一定的时间才能有数据输出,从CAS与读取命令发出到第一笔数据输出的这段时间,被定义为CL(CAS Latency,CAS潜伏期)。

这里只是简单罗列了一些重要特性,其他特性读者可以查看其datasheet。

引脚功能:

下面我们再来看看sdram 是如何寻址

1.通过ADDR24,ADDR25,确定bank地址

2.通过RA0~RA12,确定行地址(8192个行)

3.通过CA0~CA8,确定列地址(512个列)

选定bank后,通过行地址和列地址就可以定位在那个单元格,在结合原理图我们知道,fs2310接了两个sdram,地址线复用,数据线分开。这样一个4字节的数据,前两个字节存放在第一个sdram,后两个字节存放在第二个sdram。

注意:先发bank地址,在发行地址,在发列地址

此时你也许有一个疑问,如果按照上面的描述,对于一个给定的地址进行读写都是4byte,但是有我们知道,有些时候我们读取或写入只是某一个字节。对于1byte的读写是通过LDQM、UDQM。分别称为低字节屏蔽、高字节屏蔽。

在来看看sdram的时序图

Trp(Row precharge time):行预充电时间(min : 20 ns)

Trcd(/RAS to /CAS delay):行无效到列有效的时间(min : 20 ns)

呵呵,要想得到这样的时序,我们只需要配置内存控制器就可以了。

我们接的是nGCS6

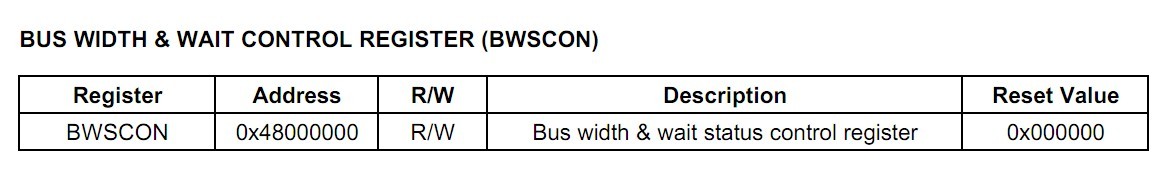

27、26都是对于SRAM 的,我们是SDRAM使用默认的就可以.[25:24] 10,有人也许会问,我们的sdram不是16bit的吗?

不要忘记了我们接了2块sdram,用了32根数据线。

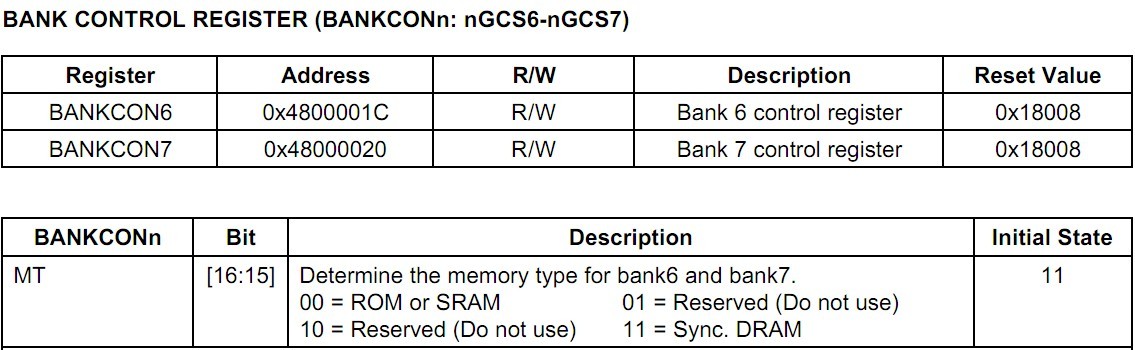

我们的sdram,[16:15] 使用11

Trcd的值 datasheet给出的最少是20ns,默认是10 = 4 clocks 对于 100MHZ,也就是40ns,个人觉得此处可以使用默认值

SCAN 10=9bit

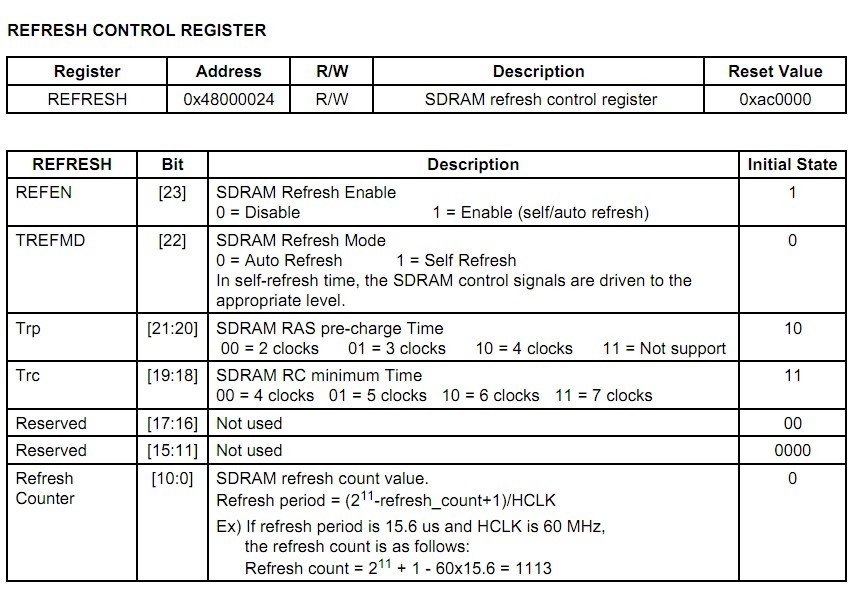

刷新控制器配置如下:

REFEN : 1

TREFMD : 0

Trp : 00

Trc : [datasheet: min 65ns]这里我们选择10 = 6clocks

Refresh Counter

我在板子上设置HCLK = 101.4MHZ,Refresh count = 2^11 + 1 - 101.4 x 7.8125 = 1256

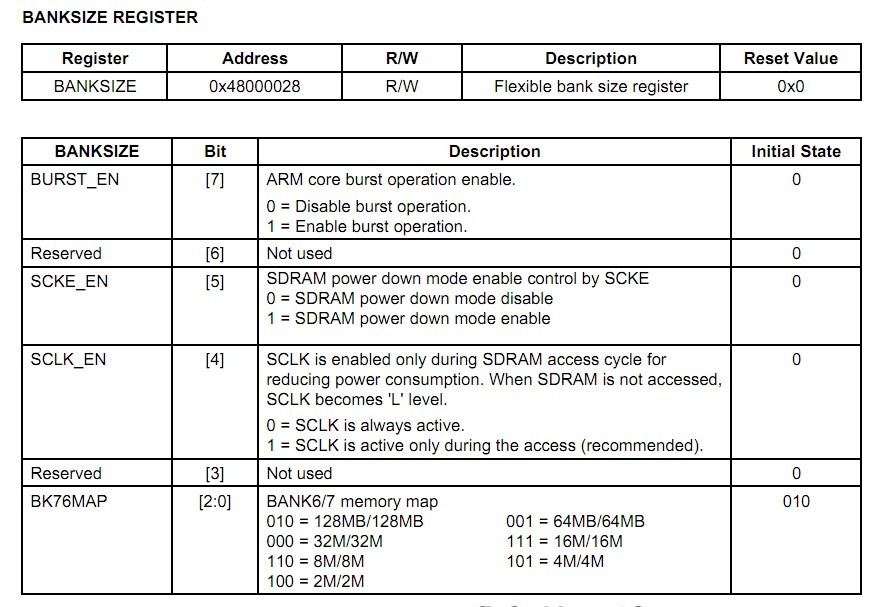

这里我们主要关注BK76MAP,其他的使用默认值

BANK6/7对应的地址空间与BANK0-5不同。BANK0~5的地址空间大小都是固定的128MB,地址范围是(x * 128M)到(x +1 )*128M -1,x表示0到5。BANK6/7的大小是可以边的,以保持这两个空间的地址连续,即BANK7的起始地址会随他们的大小变化。 <

fs2410BANK6接的是2块32M sdram,大小为64M,BANK7没用,所以[2:0] 000=64MB/64MB

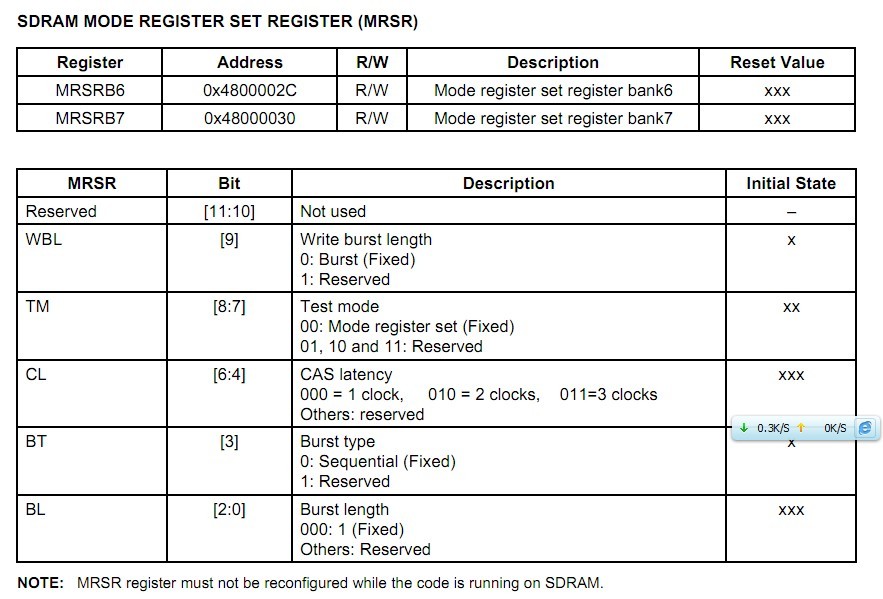

这里我们只需要设置CL就可以,其他都是fixed(固定),不需要设置。

CL : 011 = 3clocks.

SMRDATA:

.word (2 << 24) + (1 << 26) @BWSCON

.word 0x0700 @BANKCON0

.word 0x700 @BANKCON1

.word 0x700 @BANKCON2

.word 0x700 @BANKCON3

.word 0x700 @BANKCON4

.word 0x700 @BANKCON5

.word (3 << 15) + (1 << 0) @BANKCON6

.word 0x18001 @BANKCON7

.word (1 << 23) + (2 << 18) + ( 1256 << 0) @REFRESH

.word (1 << 7) + (1 << 0) @BANKSIZE

.word (3 << 4) @MRSRB6

.word (3 << 4) @MRSRB7

案例:从 nand 启动,然后将 sram的代码拷贝到sdram,然后跳到sdram中去执行代码

start.S

.extern main

.text

.global _start

_start:

#define pWTCON 0x53000000

#define CLKDIVN 0x4c000014

#define MPLLCON 0x4c000004

#define MEMBASE 0x48000000

bl disable_watchdog

bl init_sys_clock

bl init_sdrm

bl copy_sram_to_sdram

ldr pc,=on_sdram @pc指针指向内存执行代码

on_sdram:

@此时内存已经初始化好,设置栈指针

ldr sp,=0x33000000

bl main

mainloop:

b mainloop

disable_watchdog:

@关看门狗,不然cpu会不断重启

ldr r0,=pWTCON

mov r1,#0

str r1,[r0]

mov pc,lr init_sys_clock:

@目前为止,cpu工作在12MHZ频率下

@提升cpu工作频率FCLK:HCLK:PCLK=1:2:4

ldr r0,=CLKDIVN

mov r1,#3

str r1,[r0] @ifHDIVN=1,must asynchronous buf mode

mrc p15,0,r0,c1,c0,0

orr r0,r0,#0xc0000000

mcr p15,0,r0,c1,c0,0

@设置MPLL,使cpu工作在202.80MHZ

ldr r0,=MPLLCON

ldr r1,=0x000a1031

str r1,[r0]

mov pc,lr

copy_sram_to_sdram:

@将sram的4k数据全部复制到sdram中去

@sram的起始地址为0x00000000,sdram中的起始地址为0x30000000

mov r1,#0

ldr r2,=0x30000000

mov r3,#4096 @4 * 1024

1:

ldr r4,[r1],#4

str r4,[r2],#4

cmp r1,r3

bne 1b

mov pc,lr

init_sdrm:

@初始化sdram

ldr r0,=MEMBASE @13个寄存器的首地址

adrl r1,SMRDATA @13个寄存器值存放的地址

mov r2,#52 @13 * 4 = 52 add r2,r2,r1

1:

ldr r3,[r1],#4

str r3,[r0],#4

cmp r1,r2

bne 1b /*every thing is fine now*/

mov pc,lr @ .ltorg @声明一个数据缓冲池的开始

SMRDATA:

.word (2 << 24) + (1 << 26) @BWSCON

.word 0x0700 @BANKCON0

.word 0x700 @BANKCON1

.word 0x700 @BANKCON2

.word 0x700 @BANKCON3

.word 0x700 @BANKCON4

.word 0x700 @BANKCON5

.word (3 << 15) + (1 << 0) @BANKCON6

.word 0x18001 @BANKCON7

.word (1 << 23) + (2 << 18) + (1256 << 0) @REFRESH

.word (1 << 7) + (1 << 0) @BANKSIZE

.word (3 << 4) @MRSRB6

.word (3 << 4) @MRSRB7

led.c

#include "s3c2410.h"

//初始化

int led_init()

{

//GPFCON -> [8:15]清零

GPFCON &= ~(0xff << 8);

//GPF4 GPF5 GPF6 GPF7设为输出模式

GPFCON |= 0x55 << 8;

//输出高低平,关闭四路LED灯

GPFDAT |= 0xf << 4;

return 0;

}

//关闭LED

int led_off()

{

GPFDAT |= 0xf << 4; return 0;

}

//延时函数

int delay_time(int time)

{

int i,j; //让两个for循环作为延时

for(i = 0;i < time;i ++)

for(j = 0;j < time;j ++);

return 0;

}

//流水灯

int run_water_led(int count)

{

int i = 0; while(count --)

{

led_off();

delay_time(1000);

for(i = 4;i < 8;i ++)

{

GPFDAT &= ~(0x1 << i);

delay_time(1000);

}

}

return 0;

}

int main()

{

int i;

led_init(); run_water_led(5);

led_off();

return 0;

}

Makefile:

led.bin:start.S led.c

arm-none-linux-gnueabi-gcc -c -g start.S -o start.o

arm-none-linux-gnueabi-gcc -c -g led.c -o led.o

# arm-none-linux-gnueabi-ld -Ttext 0x00000000 start.o led.o -o led_elf

arm-none-linux-gnueabi-ld -Ttext 0x30000000 start.o led.o -o led_elf

arm-none-linux-gnueabi-objcopy -O binary -S led_elf led.bin

cp led.bin /tftpboot

clean:

rm -rf *.o led_elf led.bin

转自:http://www.embedu.org/Column/Column543.htm

标签:

原文地址:http://blog.csdn.net/blackberrytcl/article/details/51362831