标签:

一、概述高级微控制器总线体系(AMBA)规范定义了在设计高性能嵌入式微控制器时的一种片上通信标准。

AMBA2.0标准定义了3种不同的总线:

l 高级高性能总线(AHB)

l 高级系统总线(ASB)

l 高级外设总线(APB)

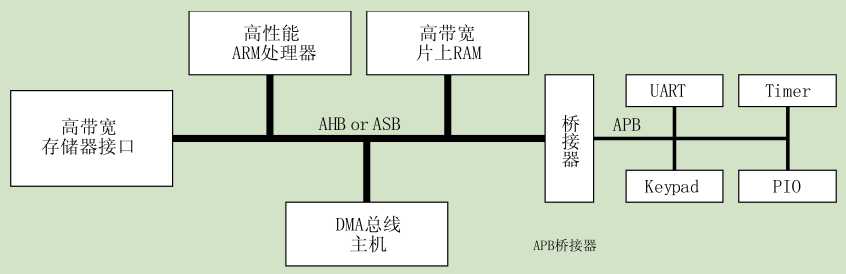

一般的系统会选择AHB/ASB+APB的总线架构,图1是一个典型的AMBA系统

图 1 典型AMBA系统

AMBA AHB用于高性能、高时钟频率的系统模块;AMBA APB则用于低功耗外设。

1、AHB信号列表

|

信号名 |

来源 |

描述 |

|

HCLK |

时钟源 |

总线时钟,其他总线信号参考对齐于HCLK上升沿 |

|

HRESETn |

复位控制器 |

总线复位信号,低有效 |

|

HADDR[31:0] |

主机 |

AHB地址总线 |

|

HTRANS[1:0] |

主机 |

表示传输类型,有空闲、非连续、连续、忙 |

|

HWRITE |

主机 |

高电平表示写,低电平表示读 |

|

HSIZE[2:0] |

主机 |

传输大小,典型情况有字节(8bit)、半字(16bit)、字(32bit),最大到1024bit |

|

HBURST[2:0] |

主机 |

表示传输是否组成突发 |

|

HPROT[3:0] |

主机 |

提供总线访问的附加信息,给那些支持保护级别的模块用 |

|

HWDATA[31:0] |

主机 |

写数据总线,主机向从机写入的数据 |

|

HSELx |

译码器 |

每个AHB从机有自己的独立选择信号,表示选择对应从机;由地址总线简单译码得到。 |

|

HRDATA[31:0] |

从机 |

读数据总线,从机向主机返回读的数据 |

|

HREADY |

从机 |

为高表示总线传输完成,拉低用来扩展传输周期 |

|

HRESP[1:0] |

从机 |

传输响应,为传输状态提供附加信息。有OKEY,ERROR,RETRY,SPLIT |

|

HBUSREQx |

主机 |

主机x向仲裁器发起一次主机请求 |

|

HLOCKx |

主机 |

主机请求锁定对总线的访问,在此信号为低前,其他主机无法获得总线访问。 |

|

HGRANTx |

仲裁器 |

表示对对应的主机授予总线访问权限。 |

|

HMASTER[3:0] |

仲裁器 |

表明那个主机正在进行传输。 |

|

HMASTLOCK |

仲裁器 |

表明当前主机正在进行锁定传输 |

|

HSPLITx[15:0] |

从机 |

支持分块传输的从机,分块总线上每一位对应一个总线主机。 |

2、APB信号列表

|

信号名 |

描述 |

|

PCLK |

总线时钟,其他总线信号参考对齐于PCLK上升沿 |

|

PRESETn |

总线复位信号,低有效 |

|

PSEL |

来自AHB2APB桥的2级译码信号,选中相应外设,表示对应外设即将发生一次传输。 |

|

PENABLE |

PENABLE表示一次APB传输的第二个时钟周期 |

|

PWRITE |

读写控制线,高为写,低为读 |

|

PRDATA |

从机返回的读的内容。-> |

|

PWDATA |

主机向从机的写入的内容 |

|

PADDR |

APB地址总线 |

二、APB总线

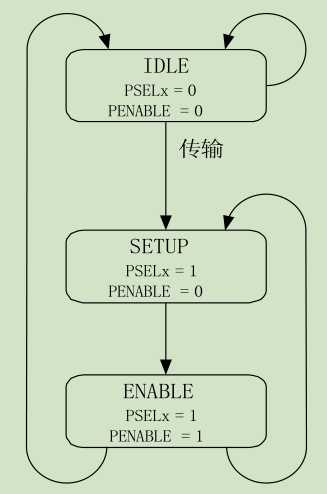

1、状态图

用图2所示状态图可以表示APB总线传输过程中的状态转换关系。

图 2 APB传输状态图

状态说明:

IDLE :空闲状态,总线大部分时间处于此状态。

SETUP :对应外设的psel信号被断言,表明对应外设即将有传输要求,总线进入SETUP状态。总线在SETUP状态保持一个周期,并总是在下一个时钟上升沿进入ENABLE状态。

ENABLE :penable信号被断言,地址、写、选择信号在SETUP进入ENABLE过程中保持不变。ENABLE状态持续一个周期,如果之后没有进一步的传输要求,总线返回到IDLE。如果紧跟另一个传输,则进入SETUP状态,进行第2次传输。

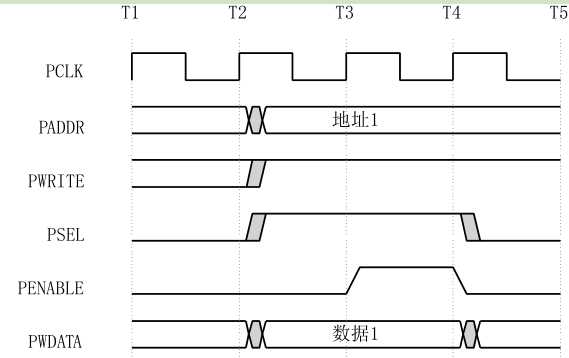

2、写传输

图3表明了一个写传输的过程:

图 3 APB写传输

如图3所示,一次传输过程中,psel保持两个周期不变,且在此期间,paddr、pwrite也保持不变,penable在psel有效的第2个周期有效。为了降低功耗,地址信号和写信号将在传输后不再改变,直到发生下一次传输。协议仅要求使能信号有个规则的跳变,背靠背传输情况下,选择和写信号可能有小跳变。

写逻辑推荐写法:

1 assign wr = psel & pwrite & (penable); 2 always @(posedge pclk or negege present) 3 begin 4 if(!presetn) 5 begin 6 REG_A <= 32’h0; 7 end 8 else if(wr & paddr = REG_A_ID) 9 begin 10 REG_A <= pwdata; 11 End 12 end

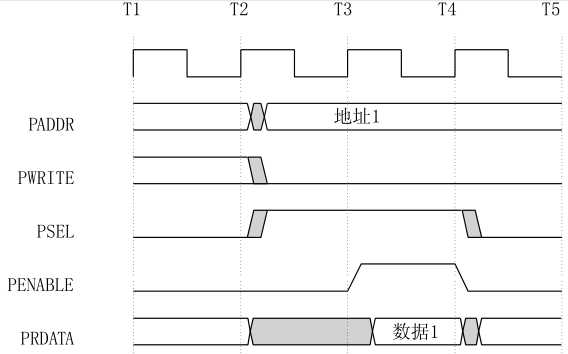

3、读传输

图4是一个读传输时序图:

图 4 APB读传输

读传输时各信号的时序和写时一样,在读传输中,从机必须在ENABLE周期提供数据,数据在ENABLE末尾的时钟上升沿被采样。

读逻辑推荐写法:

1 assign rd = psel & (~pwrite) & (~penable) ; 2 always @(*) 3 begin 4 if(rd) //setup 5 begin 6 case(paddr) 7 REG_A_ID : prdatanxt = REG_A; 8 REG_B_ID : prdatanxt = REG_B; 9 …… 10 default : prdatanxt = 32’h0; 11 endcase 12 end 13 else 14 begin 15 prdatanxt = 32’h0; 16 end 17 end 18 always @(posedge pclk or negege present) 19 begin 20 if(!presetn) 21 begin 22 prdata <= 32’h0; 23 end 24 else begin 25 prdata <=prdatanxt; 26 End 27 end

三 、AHB总线

从上面可以看出,APB总线非常简单,用于一些简单的外设连接非常方便,AHB则要复杂的多。下面简单的对其进行介绍,详细的请参看ARM官方文档。

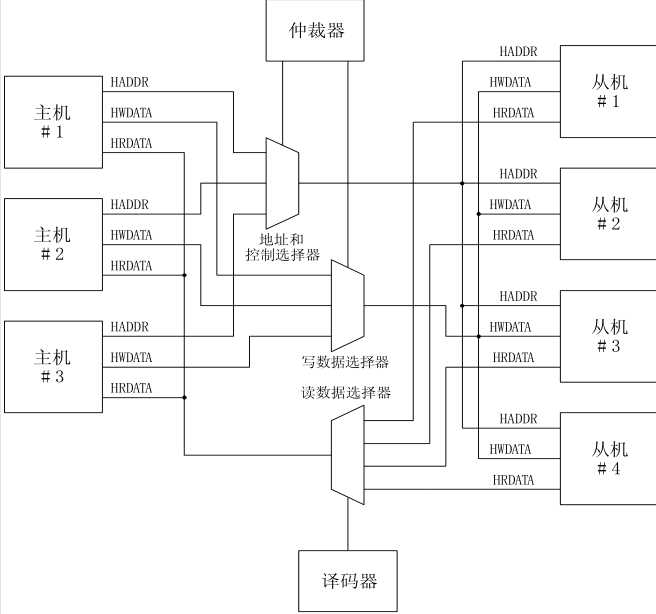

1、总线互联

AHB使用多路器进行总线互联,总线信号全部为单向传输,相比其他的三态总线,能运作在更高的频率,并且有利于综合实现。图 5为AHB总线互联架构:

图 5 AHB总线互联架构

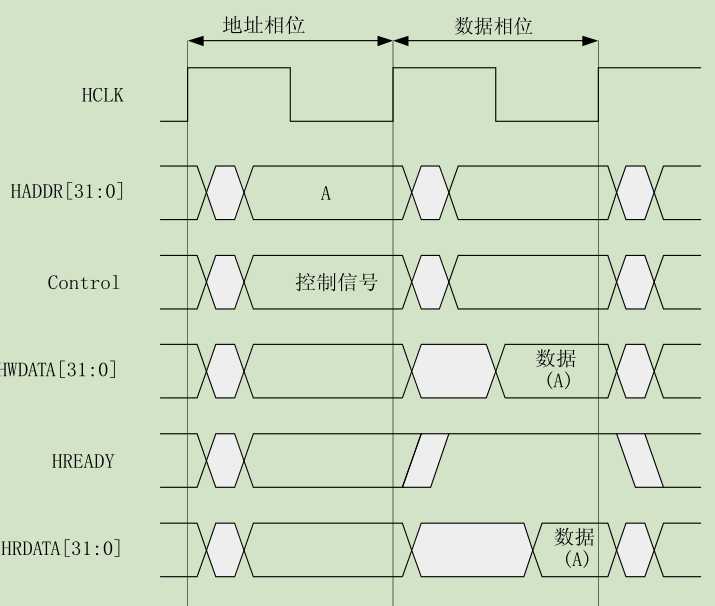

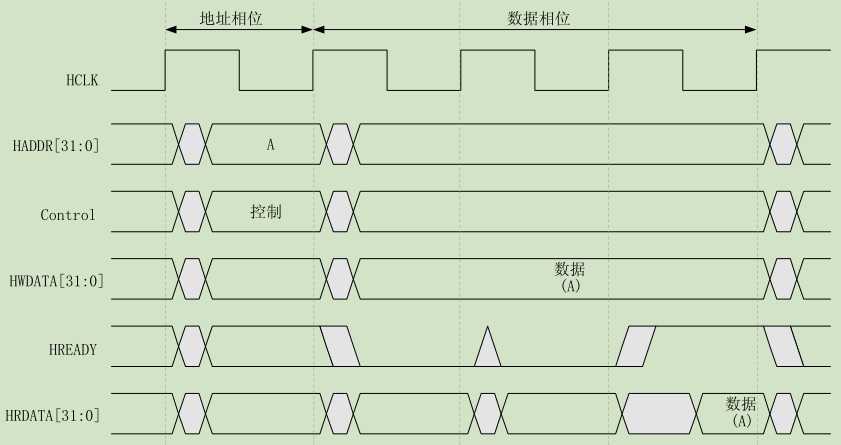

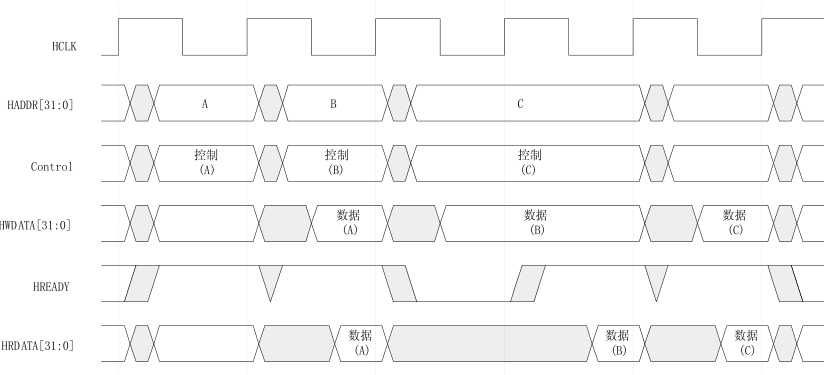

2、基本传输

AHB传输包含两个不同的部分:

l 地址相位,持续单个周期

l 数据相位,可能需要多个周期,可通过HREADY实现(会影响下一个传输的地址相位。)

图 6-1、6-2、6-3为一个AHB总线传输基本时序图:

图 6-1 AHB传输时序1

图 6-2 AHB传输时序2

图6-3 AHB传输时序3

图6-3中,地址A和地址C的传输为零等待传输,地址B的传输插入了一个等待周期,这个等待周期扩展了地址B传输的数据相位,同时影响了地址C传输的地址相位。

标签:

原文地址:http://blog.csdn.net/lkiller_hust/article/details/51344815