标签:

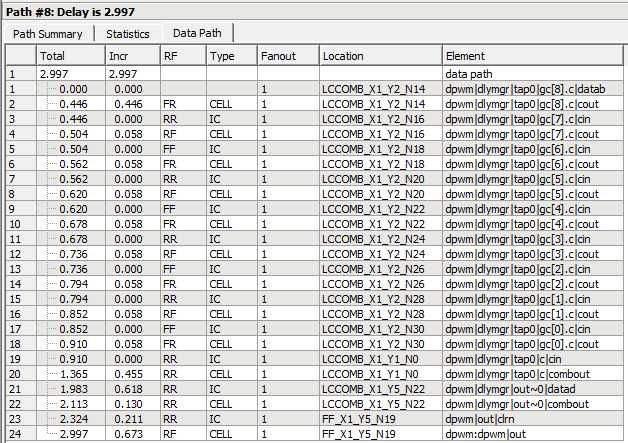

最近在FPGA上做ps级的Delay line,所以认真剖析了一下Cyclone IVE4的布局布线延迟。这里说明CARRY链的几个特性规则,如有错误请各位大大指出,谢谢。

(另外由于匆忙没有时间验证其他Cyclone系列(基于LE结构)是否遵循此特性,若其他系列中有出入请告知我。。)

规则一:CARRY链在LAB中必须顺序从上到下进位,跨LAB同样如此(从Altera的坐标系角度上说是按照Y减小的方向进位)

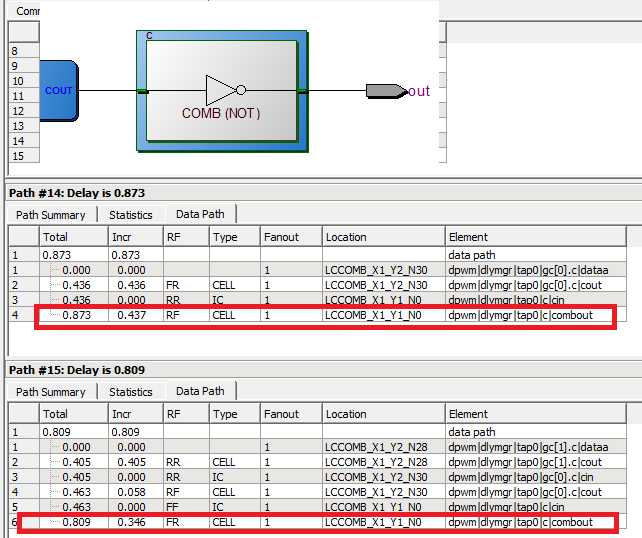

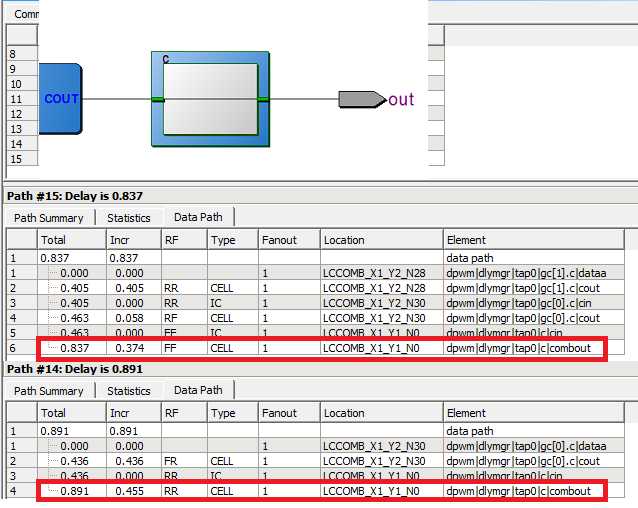

规则二:具有反相功能的延迟普遍比不反相延迟要小一点(此条不仅适用于CARRY,普通4LUT也是如此)

规则三:与或逻辑比较快,同或异或比较慢。(延迟增加约4倍)

表面解释此现象可以说因为本身进位链就是为进位逻辑服务的,所以优化了Carry实现的延迟(恳求各位大大给出物理上的正解= =)。

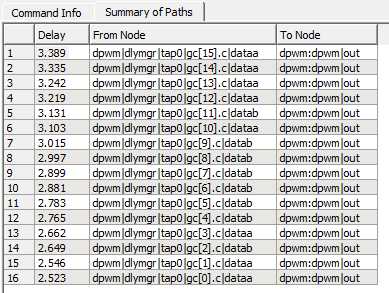

规则四:对于延时应用来说,为了取得近可能相近的延迟差,最好使每个抽头所处的环境相同(即抽头的CHAIN逻辑相同,且经过同一链)

标签:

原文地址:http://www.cnblogs.com/esxgx/p/alcy4_carry.html