标签:

Leakage power随着CMOS电路工艺进程,功耗越来越大。

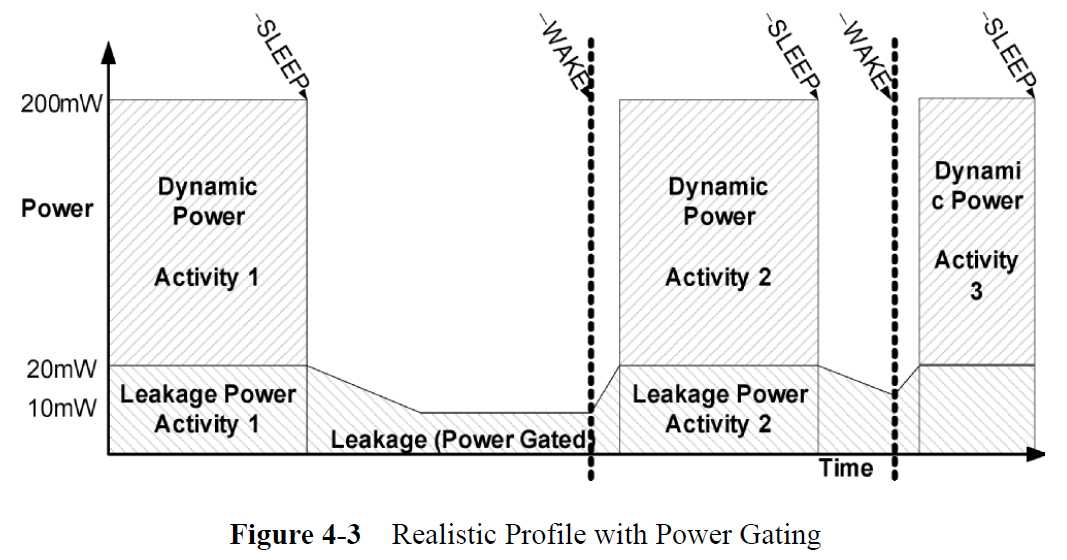

Power Domain的开关一般通过硬件中的timer和系统层次的功耗管理软件来进行控制,需要在一下几方面做trade-off:

1)可能节省的leakage power,

2)entry和exit的power和time消耗,

3)Power sleep和active的频率,

power gating可以完全关掉dynamic的power消耗,但是leakage只会减少,不会消失,因为power gating技术仍需要加入一些isolate cell

和retention cell,带来leakage。

power gate对不同的sub-system的影响:

对于cache cpu system,Power gating可以很大程度的减少leakage,消除dynamic power,但是cache内容的复原,需要花费

很大的time和energy;

对于peripheral system,device的driver可能需要特殊的initial hardware sequence,使得软件的负担加重;

对于multi-processor CPU,每当一个core完成自己的task,都可以power gating,清除自己的cache,但是big-little的core调用

需要一定的算法支撑。

外部power gating,要求板级中有多个voltage regulator,带来相应的RC,增大了板级负担,而且,switch time花费的太多。

所以现在多使用internel power gating。

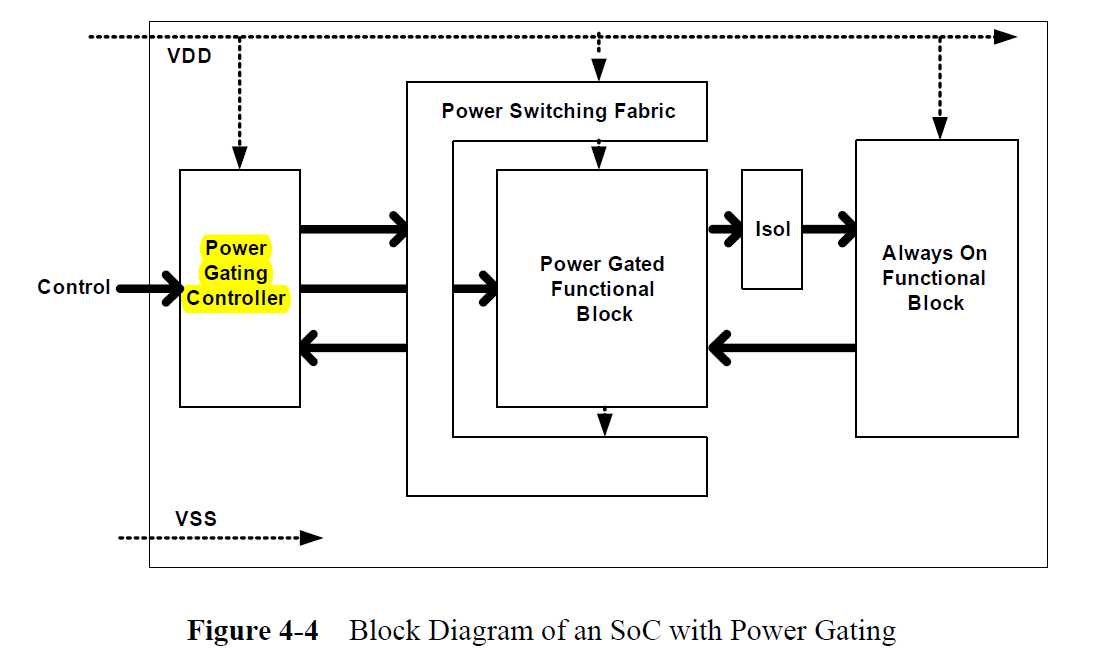

一个典型的Power Gate系统:

由于power gated block的输出由于电容的存在,电压丢失的比较慢,使得电压在Vt附近停留较长时间,可能出现狐电流(crowbar current)

所以需要加入isolate单元,同时支持两个voltage的操作,提高timing closure。

为了能够恢复到原来的状态,还需要加入rentention register来代替regular的register。retention register会附加一个shadow latch在

regular register之后,使用高Vt单元来减少leakage,但是timing会不太好。

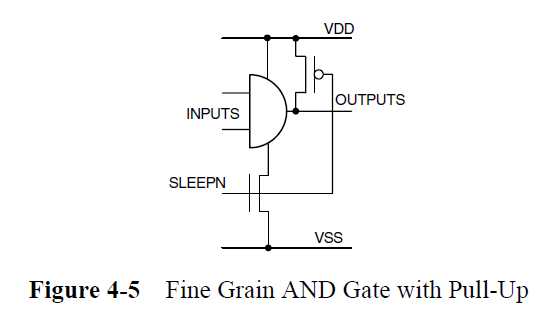

Power Switch的结构:fine grain power gating和coarse grain power gating。

fine grain power gating表示,每个switch都放在cell内部。这样使得面积增大1x-3x。

这样做的优势:可以更好的控制由于IR-Drop而导致的timing问题。

coarse grain power gating,一个block的gates拥有一组switch cell。比较节约面积。

但是这样的设计,必须控制好起电的冲击电流,控制power network中的IR-drop。

目前使用最多。

Power Gating设计中的重点:

1)Power Switch的设计;

2)Power Gating controller的设计;

3)retention register和isolation cell的选择及插入;

4)Power Gating对area和timing的影响;

5)clock和reset模块的设计;

6)Power State transaction的verfication;

7)针对manufacturing的DFT设计策略;

标签:

原文地址:http://www.cnblogs.com/-9-8/p/5487239.html