标签:

Switching Fabric的设计:

三种架构:P沟道的switch vdd(header switch),N沟道的switch vss(footer switch),两个switch。

但是如果加入两个switch,与门电路结合,可能会产生较大的IR-drop,增大delay,所以这种方式很少用。

P沟道的switch vdd,广泛应用在volatge scaling设计中。

N沟道的switch vss,很少用,有switch的电路,一般都需要level shifter。

但是一般level shifter都是一个共地,两个voltage。

Switch Fabric的控制:

主要考虑是为了减少in-rush current,voltage spike。

两种方法:

1)对switch的菊花链的控制信号(daisy-chain),control signal连接到第一级的switch,

进行buffer之后,在传递给到第二级的switch。

需要引入ack信号,来保证有效的power up。

2)对control signal进行分级,第一级开启一个weak/trickle的switch,

第二级开启main switch,

switch signal必须在always on的power内,会增加power routing的复杂性。

而且在DFT设计中,必须保证Power Gating signal是可控的。

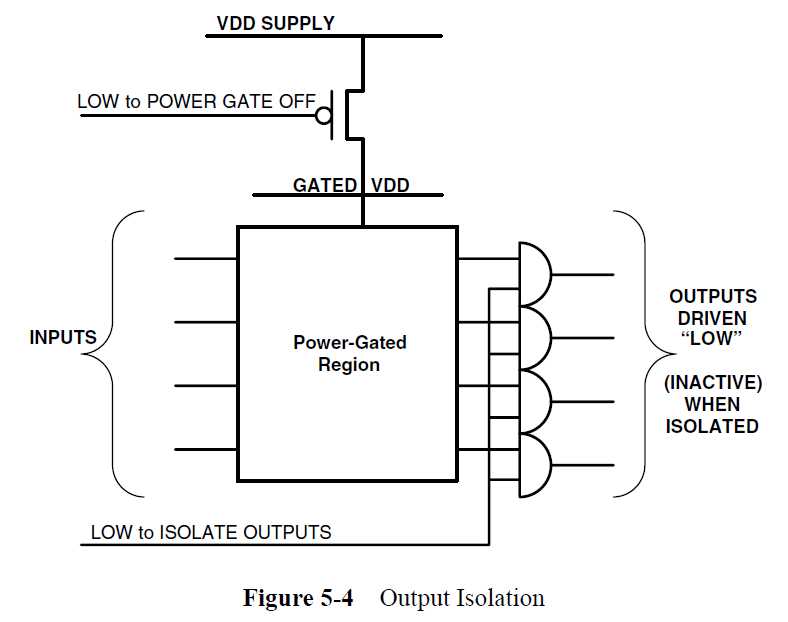

Signal isolation的必要性:

1)保证power down的region不会对power up的region的input端口产生弧电流,

2)保证power down region的浮空输出不会对power up的region产生影响,

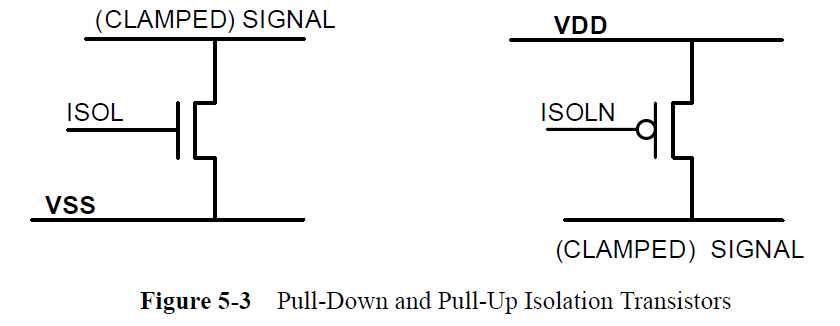

Isolation的cell,一般采用AND门电路或OR门电路进行,但这样会引入门电路的延时。

lib中的cell一般会针对leakage和timing,对这样的门电路进行优化。

还有一种方式是直接通过isolation信号将output钳位在某一电平。

但是这样会引起multi-drive的问题,isolation必须在掉电之后才能有效,无法实现。而且DFT的设计也很困难。

这样做的好处是节省area,而且timing较好。

目前的isolation cell一般都加在output端,对于reuse-ip,可以直接在内部包含isolation cell。

为了避免不必要的leakage 泄漏(sneak path),一般对于header-switched design,选择高电平的isolation控制信号,

低电平的reset有效信号和clamp到"0"。

提供retention操作的几种方式:

1)软件的方式读写register;

2)利用scan-chain的方式,将信息存储起来;

3)使用retention的register。

第一种方式,要求软件工程师了解很多的硬件操作,不介绍。后俩种对系统几乎透明,主要介绍。

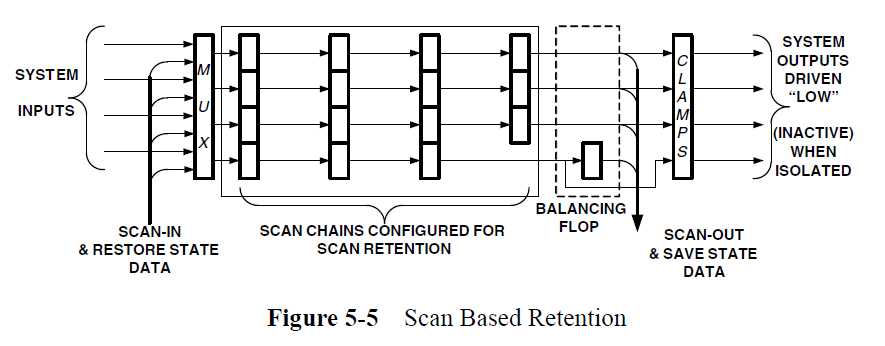

使用scan-chain的方式:

1)由于scan-chain的数目和长度都是在综合过后,才能确定的,而Power Gating在前端必须验证;

2)从数据位宽角度,scan-chain的数目必须和存储器的位宽一致;

3)由于scan-enable的信号是由所有的chain共享的,所以需要做balance;所有的san-chain等长;

4)在scan操作过程中,信号toggle的频率比正常工作大很多,DFT工具会分析IR-drop,并调整,但是retention中需注意;

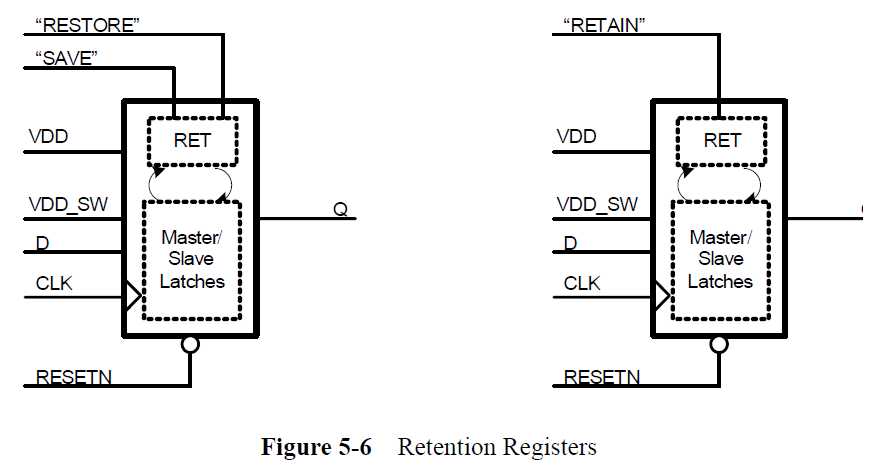

retention的register:由一个regular的register和一个shadow register组成,shadow register是always power on的。

有的由两个信号save,restore组成,有的只有一个retention信号。

save操作多在clock已经关掉,但是power还在的情况下有效,restore在power有效,clock还没开始的情况下有效。

相较于一般的register,带retention功能的,面积增加20%左右,而且shadow register多采用highVt的cell

来避免leakage过大,但是对于reset和clock tree一般选择lowVt的cell来保证timing。

partial retention:保留shallow state(control register),复位deep state(register contain large amount data);

在power up之后,电路中不会有X存在即传递,这样需要分别的reset信号来控制retention和non-retention部分。

在进行DFT测试时,需要保证可以force retention的寄存器,来检查save和restore都是deassert。

同样可以去除这个force,来检查save和restore可以assert。

Power Gating Controller:

有一个handshake来保证power down和power up的完备性。

由switch产生的ack信号,多是异步的,power controller需要做sync处理。

标签:

原文地址:http://www.cnblogs.com/-9-8/p/5495224.html