标签:

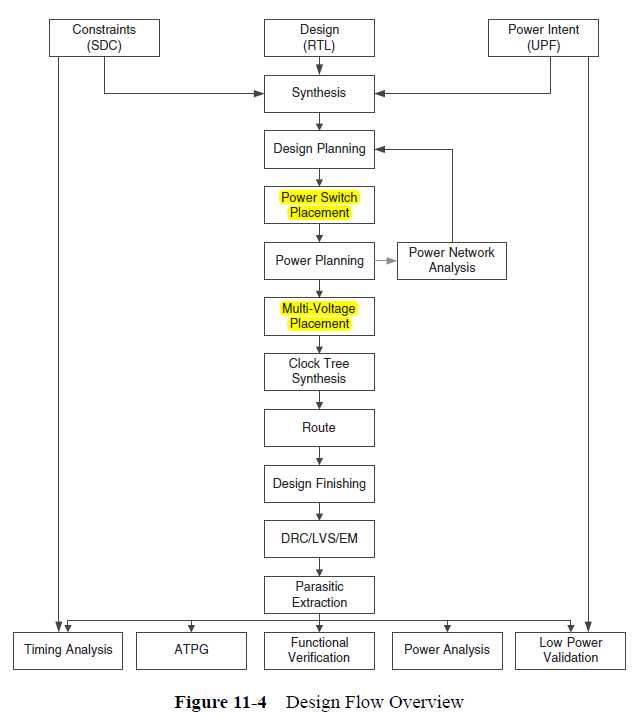

power domain:一个逻辑的集合体,包含power supply的一些信息。建立在FE。

voltage area:chip上的一块物理区域。可以看作power domain的物理实现。

Level shift,isolate cell,retention register的插入,越早越好,这样他们对timing和physical design的

影响,能更早的可见,CTS和DFT应该是对power已知的。

Power Intent描述设计中的power domain,level shifter,isoaltion cell和retention FF的插入,以及power switch的on/off。

指定lib cell来作为isolation cell进行综合。

retention register可以在综合的过程中,被自动的综合,只需要在cpf中定义retention style和一些attribute。

Level shifter,也可以在定义location和rule之后,直接在综合中自动插入到netlist中

Power rail的routing:

power rail的优化一般以减小voltage drop为目标,在power switch中,会存在较大的IR drop。

可以通过power network synthesis(PNS)来分析power的distribution。

PNS分析可以直接指定最大的voltage drop,routing layers等约束,来进行分析。

一个带sleep transistor的power network主要由三部分组成:

1)一个permanent power network;

2)一个virtual power network;

3)一个array sleep transistor;

在一个带有switch的power网络中,需要分析static和dynamic IR drop analysis。

static IR drop通常可以通过增加switch cell的个数和调整他们的位置来优化。

dynamic IR drop通常通过插入decoupling capacitor的方式来调整。

decoupling capacitor通常处理power ground和不同power rail之间的noise,capacitor的位置应该

尽可能的靠近daisy chain switch cell的起始。但是decoupling capacitor的插入会增大leakage。

在power gating中,decoupling capacitance越大,in rush电流越大,在permannet power net

上靠近switch cell的部分插入capacitor可以减小这种影响,数目需要和leakage/area做 trade-off

Lower power的validation,主要有三种方法:

1)Gate level logic simulation,

可以检查逻辑start up中的reset是clean的;

逻辑可以在不同的sleep mode之间来回切换;

在shutdown之后,逻辑可以正常工作;

在shutdown之后,可以正常的power up;

2)Equivalence checking,

Formal equivalence checking,保证gate level的netlist与original的RTL和CPF code是一致的;

3)Rule-based methods

检查gate level的netlist上的power structure是可行的,包括isolation cell和level shifter放置在

正确的domain,always on的cell被正确放置,以及cell的一些冗余等。

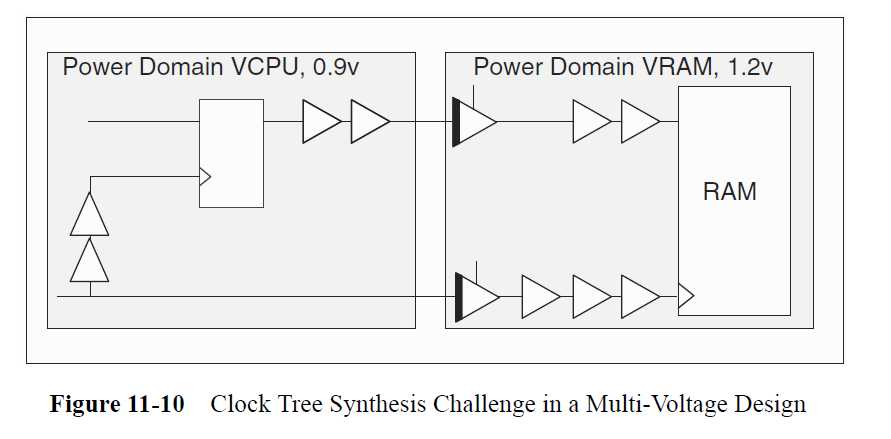

multi-voltage下的CTS:

在一个design中,clock network由于其超高高的toggle速率,power consume可能会达到一半。

当一个FF的clock path和data path的buffering不能够balanced across voltage area时,他们之间的skew处理会比较困难。

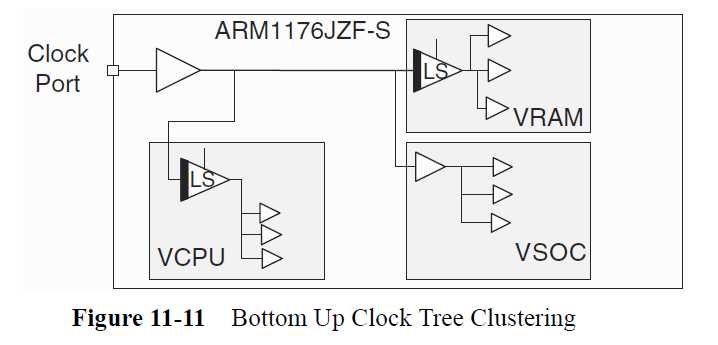

目前的时钟树综合算法,都是multi-voltage aware的,采用bottom-up的形式来构建时钟树。

每个voltage area的clock network被优化到最小的skew。

其中的LS表示level shifter,由于其引入的delay较大,所以在各个sys内部做平衡,顶层clean。

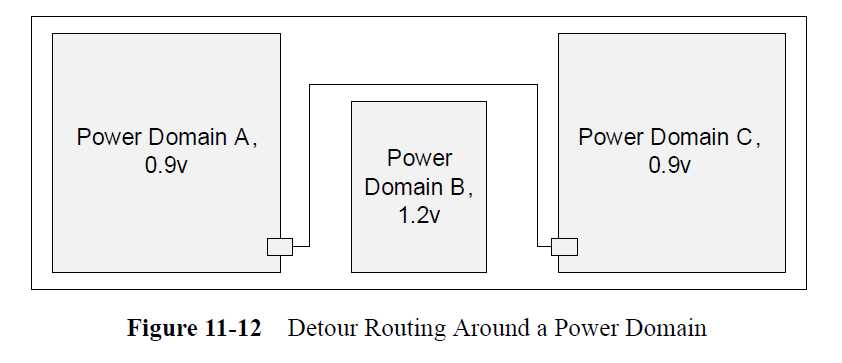

multi-voltage在routing工具中,同样是可aware的,

当从一个voltage area到另一个voltage area的signal要进行布线时,

1)加入level shifter来穿过各个voltage area;

2)detour the route;(绕远路)

加入LS的方式,带来delay,power,area方面的影响,一般选择方式二,

进行Power analysis:主要验证两个方面:

1)在power gate后的voltage drop see by standard cell。

2)处理power-up sequece过程中的in-rush电流。

多个voltage power的情况下,在进行STA分析时,必须考虑到多个operating mode和corner,以及chip variation。

on-chip的variation会使得die上的timing变得复杂。

针对multi-voltage的DFT challenge:

1)Power aware architecture和scan chain的reorder;

2)across power domain的过程中,DFT信号的level shifter和isoaltion cell的自动插入;

3)across power domain的信号的timing issue;

4)scan enable信号的布线调整,来避免power domain crossing;

在Manufacturing Test中,由于Power Consumption的不同,会导致voltage drop的不同,继而使得critical path

的改变,所以,在目前的Manufacturing的test中,需要做stuck-at和delay-fault的test,而且在不同的

operating voltage和temperature下,都必须分别进行测试,所以test time(cost)和coverage之间会有一个trade-off。

isoaltion cell和level shifter一般放在voltage area的边缘来保证对timing的影响降低到最小。

power up的sequence设计限制in-rush的电流,通常将switch分组,在speed和noise之间做trade-off。

标签:

原文地址:http://www.cnblogs.com/-9-8/p/5483351.html